- •Глава 1

- •1.1. Принципы управления и задачи, решаемые автоматизированными системами

- •1.2. Автоматизация управления системой электроснабжения

- •1.3. Информация в системах управления электроснабжением железных дорог

- •1.5. Демодуляция

- •1.6. Кодирование

- •Глава 2

- •2.3. Шифраторы и дешифраторы

- •2.4. Триггеры

- •2.6. Распределители импульсов

- •2.8. Устройства, реагирующие на уровни сианалов

- •2.9. Врелязадающие и времяизлеряющие схемы

- •2.10. Модуляторы импульсных последовательностей

- •Глава 3

- •3.1. Устройства автоматического повторного

- •Глава 4

- •4.1. Назначение устройств автоматики контактной сети

- •Устройства автоматики фидеров контактной сети переменного тока

- •Испытание контактной сети постоянного тока до апв

- •Устройство автоматики фидеров контактной сети постоянного тока

- •Автоматика постов секционирования

- •Автоматика пунктов параллельного соединения

- •Автоматизация работы трансформаторов

- •Автоматика понижающих трансформаторов

- •Автоматика трансформаторов собственных нужб

- •Глава 6 принципы построения устройств телемеханики

- •6.4. Методы синхронизации распределителей

- •6.5. Принципы построения устройств телеизмерения

- •Глава 7

- •7.1. Телемеханизация системы электроснабжения

- •7.8 Принципы выполнения ту и тс подсистемы «Лисна-в»

- •7.10. Передающий полукомплект телесигнализации

- •Глава 8

- •Глава 9

- •Глава 10

2.6. Распределители импульсов

Распределителем импульсов называется устройство, которое распределяет поступающую на его вход серию импульсов по независимым выходным цепям. При наличии у распределителя N выходов он преобразует временную последовательность импульсов (последовательный единичный код) в код C4N

существует многочисленный класс распределителей импульсов, отличающихся как принципом действия так и элементной базой: на электромеханических элементах (шаговые искатели, релейные распределители); на магнитно-диодных и магнитно-транзисторных элементах. Простейшим распределителем импульсов является кольцевой сдвигающий счетчик с числом устойчивых состояний, равным числу распределяемых импульсов (см. рис. 2.29).

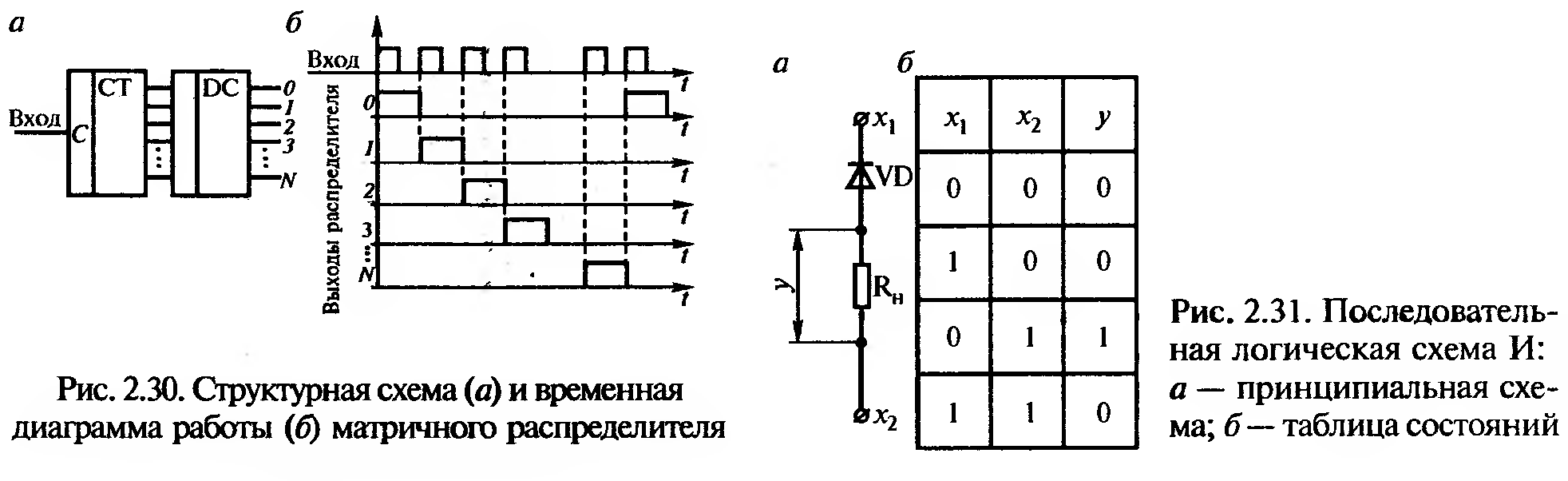

При большом числе выходных цепей более рациональным является матричный распределитель, состоящий из многоразрядного счетчика СТ и дешифратора DC (рис. 2.30, а). Дешифратор преобразует кодовую комбинацию сигналов с выходов счетчика в код C4N . По мере поступления импульсов на вход С счетчика СТ на его выходах меняется комбинация сигналов, поступающих на входы дешифратора DC. Сигнал переходит последовательно с одного выхода дешифратора на другой (рис. 2.30, б).

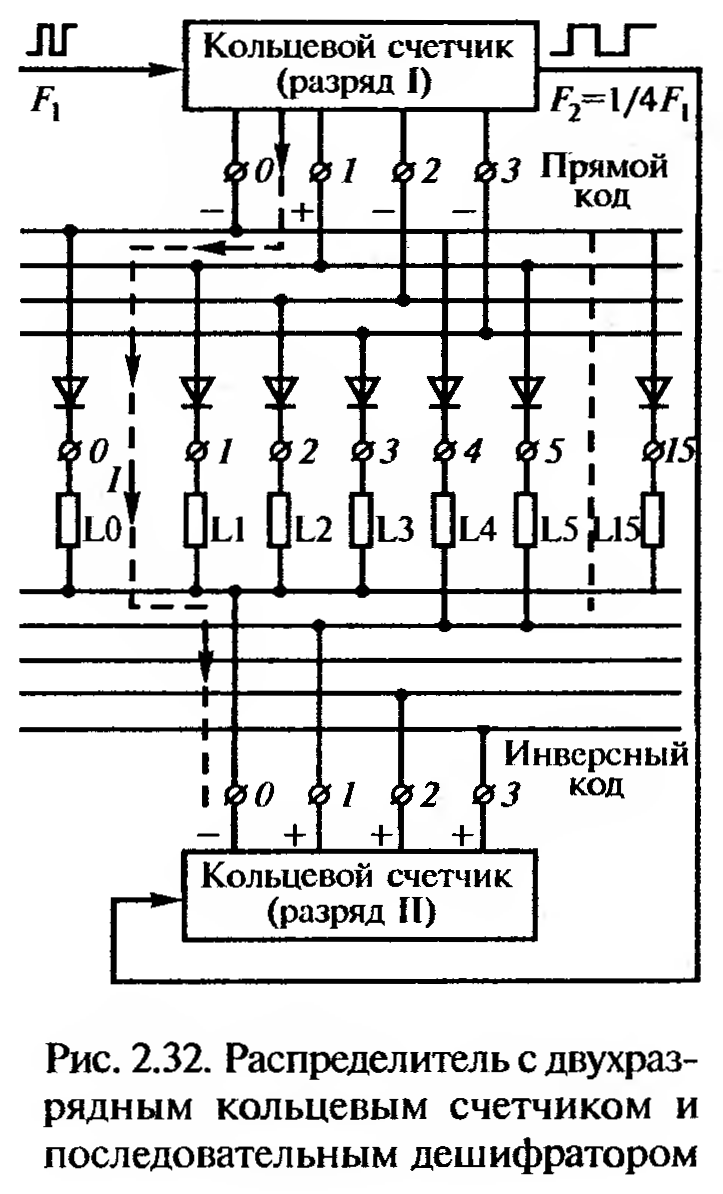

В распределителях могут быть использованы одно- или многоступенчатые дешифраторы. Одноступенчатые дешифраторы в распределителях применяются при числе выходов N≤16 (реже при N= 32). При большем числе выходов в распределителях используются многоступенчатые дешифраторы, позволяющие значительно уменьшить число логических элементов. Так в распределителе с двухразрядным счетчиком применяются дешифраторы с последовательными схемами совпадения И. Принципиальная электрическая схема последовательного логического элемента И приведена на рис. 2.31, о. Схема включает один диод VD и резистор нагрузки RH. По резистору может протекать ток только при одной комбинации входных потенциалов (сигналов): на входе x1 низкий

потенциал (сигнал 0), на входе х2 высокий потенциал (сигнал 1). При этом на резисторе RH создается падение напряжения (сигнал 1). Резистор RH является выходным элементом логической схемы. В таблице рис. 2.31, б приведены сигналы на выходе у в зависимости от комбинации сигналов на входах х1 и х2.

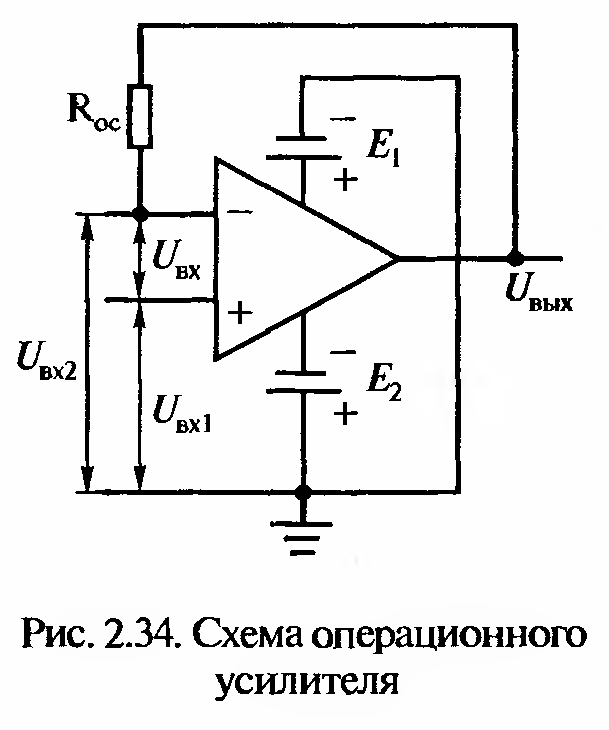

Последовательные схемы И включаются между выходами кольцевого счетчика первого разряда (прямой код) и второго разряда (инверсный код) (рис. 2.32).

В исходном состоянии счетчика на выходе 0 первого разряда высокий потенциал, а на выходе 0 второго разряда — низкий. Ток протекает через последовательную логическую схему L0, на выходе которой появляется сигнал 1, на остальных (1... 15) — сигналы 0. При поступлении на вход распределителя последовательности импульсов с частотой F\ первый разряд переключается. После первого импульса высокий потенциал будет на выходе 1 первого разряда. Через логическую схему L1 пройдет ток (цепь тока показана на рис. 2.32 пунктирной линией).

Второй

разряд счетчика переключается с частотой

F2

=

1 /4

F1.

Каждый его выход поочередно подключается

через логическую последовательную

схему к выходам первого разряда счетчика.

Число выходов распределителя N=

N1

N2,

где

N1

и

N2

—

число выходов первого и второго разрядов.

Второй

разряд счетчика переключается с частотой

F2

=

1 /4

F1.

Каждый его выход поочередно подключается

через логическую последовательную

схему к выходам первого разряда счетчика.

Число выходов распределителя N=

N1

N2,

где

N1

и

N2

—

число выходов первого и второго разрядов.

Недостатком рассмотренного распределителя является отсутствие общей точки отдельных логических схем, необходимой для подключения к нулевой шине питания, а значит нельзя применять стандартные логические элементы (транзисторные или интегральные), так как они всегда имеют связь с источником питания. В системах телемеханики ЭСТ-62 и «Лисна» в качестве нагрузок для таких дешифраторов используются обмотки записи тороидальных трансформаторов с прямоугольной петлей гистерезиса.

В современных устройствах телеуправления (например, в системе МРК) в качестве нагрузок используются светодиоды оптронных элементов, которые гальванически развязаны с источниками питания и могут включаться в последовательную схему совпадения.

Двоичные счетчики с дешифраторами параллельного типа часто используют вместо кольцевых счетчиков. В распределителях систем телемеханики ЭСТ-62 и «Лисна» применяется двухступенчатый комбинированный параллельно-последовательный матричный дешифратор и двоичный многоразрядный счетчик (рис. 2.33, а). Дешифраторы А и Б

параллельного типа образуют первую ступень, причем дешифратор А работает в прямом, дешифратор Б — в инверсном коде (на его выходах включены инверторы). К дешифратору А подключены n1 низших разрядов счетчика, к дешифратору Б — высшие разряды п — n1 (п — полное число разрядов). С помощью дешифраторов комбинации кодов на входах преобразуются в распределительные: код С1N1. (дешифратор А) и

(дешифратор Б), где N1 = 2"1, a n2 = 2n-n1. Дешифратор В второй ступени является дешифратором последовательного типа.

В устройствах телемеханики ЭСТ-62, «Лисна» и МРК с целью удвоения числа выходных цепей используют два дешифратора А и А' прямого кода (рис. 2.33, б), подключаемые к счетчику параллельно. Выходы дешифраторов А и А' связаны с дешифратором Б инверсного кода через дешифраторы В и В' последовательного типа. Дешифраторы А и В работают только на импульсах (запрет на паузе), а А' и В' — на паузах (запрет на импульсах) тактовой серии.

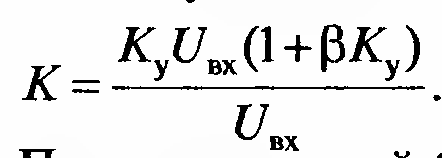

Операционные усилители

Операционные усилители (ОУ) в интегральном исполнении составляют основу современной электронной схемотехники и находят широкое применение в электронных устройствах. Такие усилители еще использовались для решения оперативных управлений в аналоговых вычислительных машинах и аппаратуре электронной техники первого поколения.

До появления линейных интегральных схем к классу операционных усилителей относили многокаскадные усилители постоянного тока с обратными связями, которые использовались в аналоговой вычислительной технике для выполнения математических операций сложения, вычитания, умножения, деления, дифференцирования, интегрирования, логарифмирования и т.д. Однако усилители постоянного тока на дискретных транзисторах имели многочисленные недостатки.

Появление серийных партий ОУ в виде интегральных микросхем позволило значительно усовершенствовать их технические и эксплуатационные показатели. Все это существенно расширило универсальность и функциональную ориентацию интегральных ОУ.

Основные свойства операционных усилителей. Универсальный ОУ является усилителем постоянного тока с высоким коэффициентом усиления (Ку = 103...106), высокое входное сопротивление (RBX -> ∞) и низкое выходное (Явых —>0). К основным свойствам идеального ОУ следует также отнести широкую полосу частот, начиная с частоты f = 0 и постоянство амплитуды усиливаемого сигнала во всем диапазоне частот.

Операционный усилитель (рис. 2.34) обычно имеет дифференциальный вход (два входных зажима, на которые подаются напряжения Uвх1 и UBx2). Входное напряжение UBX является разностью напряжений Uвх1 и Uвх2. Причем каждое из входных напряжений UBx

и UBX2 может быть положительным и отрицательным относительно потенциала общей (заземленной) точки двух источников питания Е1 и E2.

Большинство стандартных интегральных ОУ имеет один выход. Выходное напряжение UВЬ1Х находится в фазе с напряжением и противофазно напряжению Uвх2, оно пропорционально дифференциальному напряжению входа Uвх = Uвх1 - Uвх2

Питание

ОУ осуществляется от двух соединенных

последовательно источников с

одинаковыми постоянными ЭДС и Е2

или от одного источника со средней

точкой, которая заземлена. При

использовании делителей напряжения

возможно питание ОУ от одного

источника, однако это приводит к

увеличению потребления энергии и

снижению показателей работы ОУ.Обратная

связь (ОС), образованная между входом

и выходом ОУ, позволяет получить

многие положительные свойства

передаточных характеристик между

Uвых

и Uвх.

Пусть часть (Uвых

через резистор (или иной элемент)

обратной связи Roc,

равная

ßUВЫХ,

поступает на вход ОУ. При этом

ß-коэффициент

передачи цепи ОС обычно меньше единицы

(ß

< 1).

Коэффициент

ß

может быть действительной или мнимой

величиной.При наличии ОС на вход ОУ

поступает только часть напряжения,

равная Uвых

=

ßUBbIX,

тогда

UBbIX

=

KyUBX(1

+

ßKу),

где Ку

—

коэффициент усиления ОУ при разомкнутой

цепи ОС. В схеме с ОС коэффициент

усиления К

= Uвых

/ UBX.

Подставив

в это выражение UBblx,

получим:

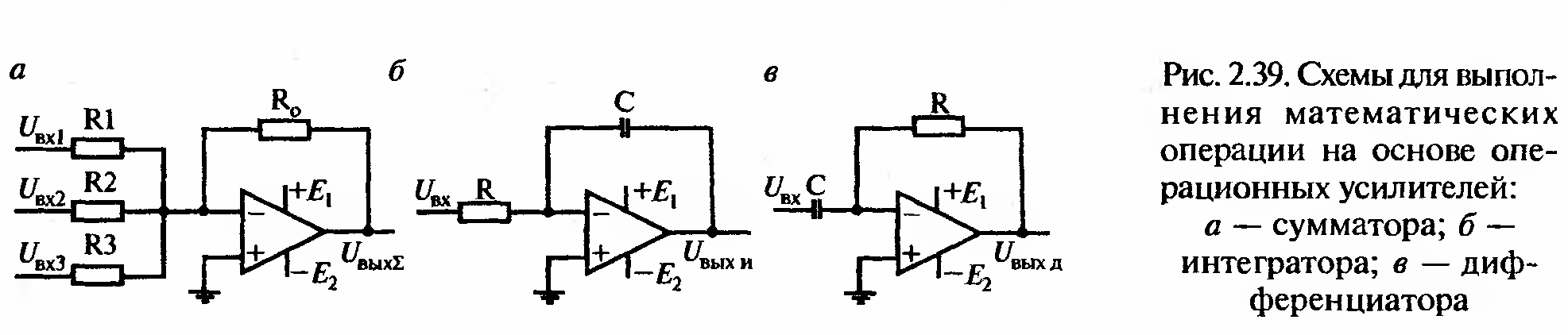

Таким образом, коэффициент

усиления ОУ с ОС К

= Ку(1

+ ßKу).

Таким образом, коэффициент

усиления ОУ с ОС К

= Ку(1

+ ßKу).

При разомкнутой ОС (ß = 0) соотношение между K и Kу будет K = Kу.

Структурные схемы стандартных ОУ приведены на рис. 2.35, на котором показаны схемы трехкаскадного и двухкаскадного ОУ, представляющие собой интегральные усилители соответственно первого и второго поколений. Структурная схема трехкаскадного ОУ приведена на рис. 2.35, а. Первый каскад обычно выполняется по схеме простого дифференциального усилителя (ДУ), имеющего два входа и два выхода. Второй каскад — усилитель напряжения (УН), также выполнен по схеме дифференциального усилителя и обладает значительным коэффициентом усилителя. В УН осуществляется также сдвиг уровня усиливаемого напряжения с целью согласования выхода этого каскада со входом оконечного усилителя по постоянной составляющей тока. Выходной каскад является усилителем амплитуды (УА) сигнала и состоит из сочетания нескольких каскадов, потребляющих основную часть энергии всего усилителя. Общий коэффициент усиления трехкаскадного ОУ может достигать 100000 и более.

Изменение технологии изготовления интегральных структуру позволило в ОУ второго поколения совместить функции первого и второго каскадов в одном каскаде усиления (ДУ). Промышленная реализация двухкаскадных ОУ (рис. 2.35, 6) с удовлетворительными малосигнальными параметрами и частотными свойствами позволила внедрить сложные дифференциальные каскады, обладающие повышенным коэффициентом усиления. При этом общее усиление двухкаскадных ОУ сохраняется на прежнем уровне.

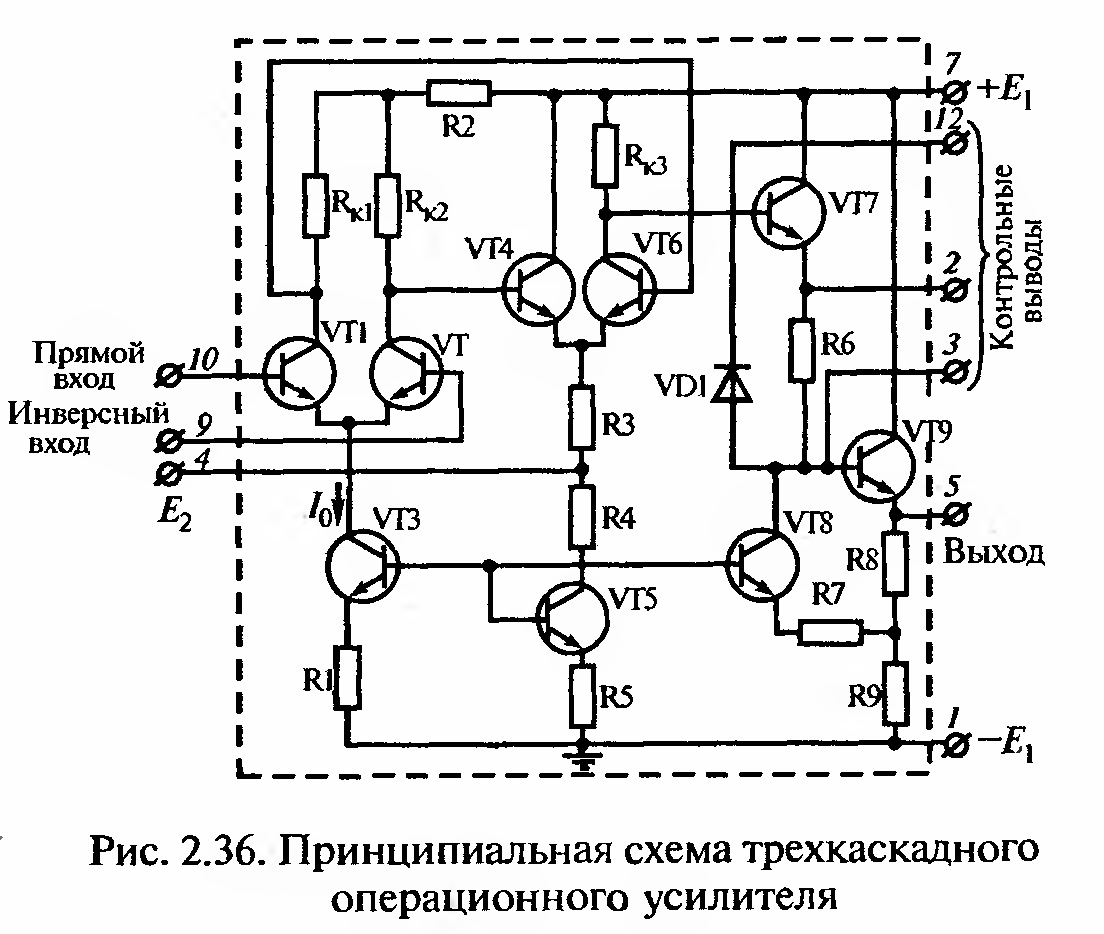

Принципиальная схема одного из интегральных ОУ приведена на рис. 2.36.

Второй каскад на транзисторах VT6 и VT4 также выполнен по схеме дифференциального усилителя с симметричным входом и несимметричным выходом. Вывод 4 служит для подключения источника питания Е2 для цепей эмиттера через резистор R3.

Выходной каскад, является сложным эмиттерным повторителем на транзисторах VT7 и VT9 с генератором стабилизированного тока на транзисторе VT8.

К выводу 5, являющемуся выходом усилителя, подключается внешняя нагрузка в цепи обратной связи, а к выводам 1 и 7— источник питания Е\. Выводы 2, 3, 12 являются контрольными и предназначены для подключения корректирующих цепей.

Значительно лучшие технические параметры имеет двухкаскадный ОУ, схема которого представлена на рис. 2.37. Дифференциальный входной каскад выполнен на транзисторах VT1 и VT2, эмиттерные цепи которых питаются от генератора тока на транзисторе VT7. При идентичности параметров входных транзисторов VT1 и VT2 обеспечивается высокая степень симметрии схемы по обоим входам. «Токовое зеркало» на транзисторах VT11, VT7, VT6 используется в качестве источников тока для дифференциального (VT7) и выходного (VT6) каскадов. Известно, что при постоянном напряжении Uбэ транзистор с заземленным эмиттером имеет строго определенный коллекторный ток. Однако он может сильно меняться при колебании температуры окружающей среды. Для компенсации температурных отклонений коллекторного тока параллельно переходу база-эмиттер включается прямосмещенный диод или транзистор в диодном включении (коллектор VT11 объединен с базой). Если транзисторы VT11, VT7, VT6 строго идентичны, то происходит не только точная компенсация температурных изменений, но и точное задание коллекторных токов VT7 и VT6. Если создать ток смещения Iсм в цепи транзистора VT11, то в коллекторах транзисторов VT7 и VT6 будут такие же токи Iк7 = Iк6 -Iсм (происходит как бы зеркальное отражение тока Iсм в коллекторных токах транзисторов).

Для повышения точности отображения и стабильности в цепи эмиттеров транзисторов иногда дополнительно включают резисторы. Активная нагрузка дифференциального каскада, выполненная на «токовом зеркале» VT12 и VT3, позволяет, с одной стороны, обеспечить в транзисторах VT1 и VT2 постоянные токи, с другой — большее усиление по напряжению выходного каскада ОУ, так как транзистор VT3 имеет значительное входное сопротивление для переменной составляющей сигнала.

Промежуточный усилитель выполнен на составном транзисторе VT4 и VT5. Если на входах ОУ появится дифференциальный сигнал, при котором, например, уменьшится на ∆Iк ток транзистора VT1 и на столько же увеличится ток транзистора VT2, то на Д/к уменьшается также ток в транзисторе диодного включения VT12, в транзисторе источника тока VT3 и, следовательно, в нагрузке (цепь базы VT4) ток увеличивается на 2∆IК.

Выходной каскад выполнен двухтактным на транзисторах разной проводимости VT8 и VT9. Потенциалы баз одинаково смещенных транзисторов VT8 и VT9 должны различаться на 2Uбэ =1,3 ... 1,4 В, это и обеспечивают диоды VD1 и VD2, включенные между базами транзисторов VT8 и VT9. Для увеличения коэффициента усиления по току выходной транзисторный каскад ОУ состоит из транзисторов VT9 и VT10.

Рассмотренный ОУ может работать с очень низким напряжением питания (ЗВ) и обеспечивает при этом усиление примерно в 104 раз по напряжению.

Многие ОУ имеют существенно более сложные схемы, однако, общие принципы построения их сходны с рассмотренными выше.

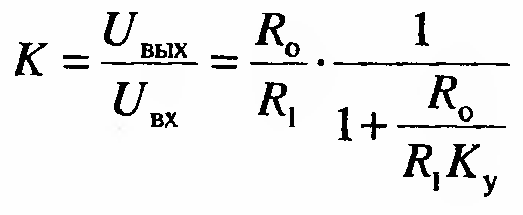

Рассмотрим

некоторые часто встречающиеся на

практике схемы, в которых применяются

операционные усилители. На рис. 2.38

приведены схемы усиления сигналов на

основе ОУ. Инвертирующий усилитель

(рис. 2.38, а)

имеет выходное напряжение, сдвинутое

по фазе относительно входного на 180°.

Коэффициент усиления такой схемы

условно считается отрицательным.

Введение отрицательной обратной связи

(резистор R0)

позволяет

повысить стабильность коэффициента

усиления схемы или расширить ее частотный

диапазон. Если коэффициент усиления Ку

операционного усилителя имеет конечное

значение, то коэффициент

усиления схемы (рис. 2.38, а)

При

![]() получим

получим

![]() тогда

тогда

![]()

Отношение

Отношение

— называется масштабным коэффициентом.

Если соотношение между

Uвых

и Uвх

записать в виде

Отношение

— называется масштабным коэффициентом.

Если соотношение между

Uвых

и Uвх

записать в виде

![]() то получим Uвых=-R0Iвх

.Это

выражение

справедливо

при активных, реактивных и комплексных

сопротивлениях во входной цепи и цепи

обратной связи. Коэффициент

обратной связи неинвертирующего

усилителя (рис. 2.38, б)

β=

-R0

то получим Uвых=-R0Iвх

.Это

выражение

справедливо

при активных, реактивных и комплексных

сопротивлениях во входной цепи и цепи

обратной связи. Коэффициент

обратной связи неинвертирующего

усилителя (рис. 2.38, б)

β=

-R0 , а коэффициент усиления

схемы К =1+

т.е. на единицу больше, чем в схеме

инвертирующего усилителя (рис. 2.38,

а). тобы

выровнять усиление по прямому и инверсному

входам, например, в схеме вычитающего

усилителя (рис. 2.38, в),

необходимо в цепь прямого входа включить

делитель напряжения (резисторы R2

и

R3),

который

уменьшит усиление по прямому входу в

, а коэффициент усиления

схемы К =1+

т.е. на единицу больше, чем в схеме

инвертирующего усилителя (рис. 2.38,

а). тобы

выровнять усиление по прямому и инверсному

входам, например, в схеме вычитающего

усилителя (рис. 2.38, в),

необходимо в цепь прямого входа включить

делитель напряжения (резисторы R2

и

R3),

который

уменьшит усиление по прямому входу в

раз. В простейшем случае для схемы рис.

2.38, в

имеем R2

=

R1

и

Rз

= R0.

раз. В простейшем случае для схемы рис.

2.38, в

имеем R2

=

R1

и

Rз

= R0.

Если в схеме рис. 2.38, б принять R1 = ∞ или Rо = 0, то К= 1, т.е. получится схема повторителя напряжения (рис. 2.38, г).

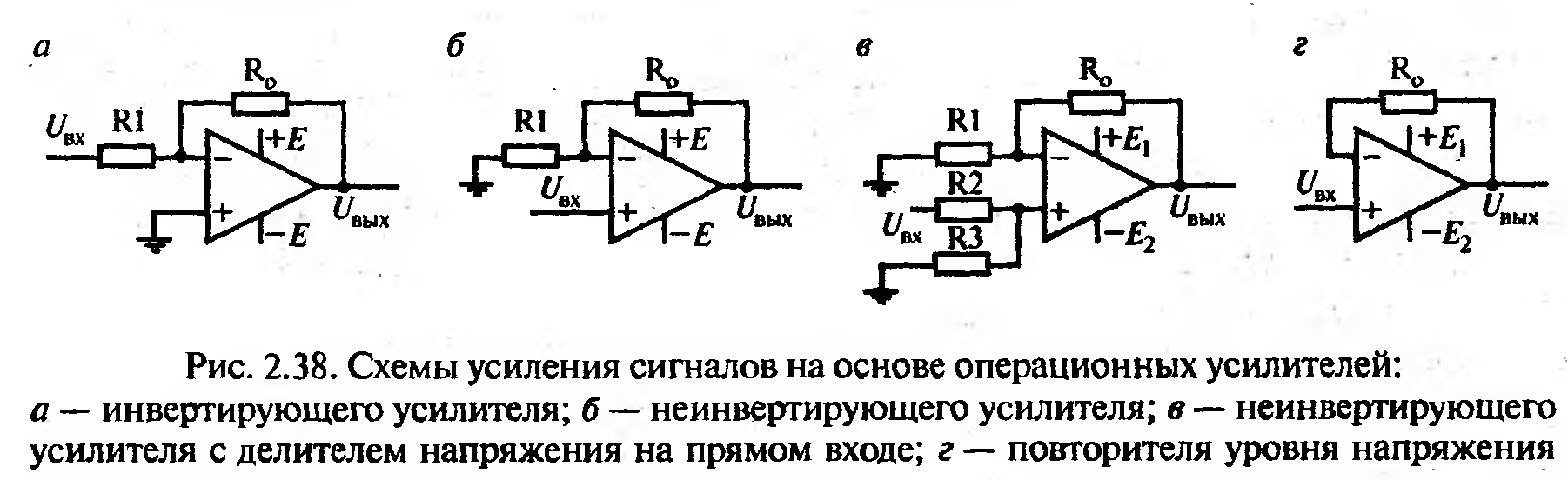

Выполнение

математических операций аналоговым

способом осуществляется с помощью ОУ.

Схема рис. 2.39, а

представляет собой суммирующий усилитель.

Выходное напряжение равно сумме входных

напряжений, каждое из которых умножено

на свой масштабный коэффициент

При

= R1

=

R2=

R3

= R

и

R0

/ R1

= К

получим Uвых∑

= K(Uвх1

+

Uвх2

+ Uвх3),

т.е.

выходное напряжение пропорционально

сумме входных.

При

= R1

=

R2=

R3

= R

и

R0

/ R1

= К

получим Uвых∑

= K(Uвх1

+

Uвх2

+ Uвх3),

т.е.

выходное напряжение пропорционально

сумме входных.

В схеме рис. 2.39, б

выполняется операция интегрирования.

Выходное напряжение определяется из

выражения:

![]()

В схеме рис. 2.39, в

выполняется операция дифференцирования

входного напряжения. Выходное

напряжение определяется из выражения:

![]() На основе ОУ осуществляются и другие

математические операции, например,

возведение в квадрат и т.д.

На основе ОУ осуществляются и другие

математические операции, например,

возведение в квадрат и т.д.