- •Мова опису апаратури ahdl

- •1. Елементи мови

- •1.1. Ключові слова й ідентифікатори

- •1.2. Символи

- •1.3. Імена

- •1.4. Групи

- •1.5. Числа

- •1.6. Вирази

- •1.6.1. Арифметичні вирази

- •1.6.2. Логічні вирази

- •1.7. Оператори

- •1.7.1. Логічні оператори

- •1.7.2. Арифметичні оператори

- •1.7.3. Оператори порівняння

- •1.8. Пріоритет виконання операцій

- •1.9. Примітиви

- •1.9.1. Примітиви буферів

- •1.9.2. Буфер ланцюгового переносу (carry)

- •1.9.3. Буфер каскадного нарощування логічної функції (cascade)

- •1.9.4. Буфер логічного розширювача (ехр)

- •1.9.5. Буфер глобального ланцюга поширення управляючого

- •1.9.6. Буфер розміщення логічного осередку (lcell),

- •1.9.7. Буфер виходу з відкритим колектором (opndrn)

- •1.9.8. Буфер розміщення логічного осередку (soft),

- •1.9.9. Буфер виходу з z станом (tri)

- •1.10. Примітиви тригерів

- •2. Структура текстового опису

- •2.1. Загальна структура

- •Include Statement.

- •2.2. Розділ оголошення операторів

- •2.2.1. Title Statement

- •2.2.2. Parameters Statement

- •2.2.3. Include Statement

- •2.2.4. Constant Statement

- •2.2.5. Define Statement

- •2.2.6. Function Prototype Statement

- •2.2.7. Options Statement

- •2.2.8. Assert Statement

- •2.3. Subdesign Section

- •2.4. Variable Section

- •2.5. Logic Section

- •3. Застосування конструкцій мови

- •3.1. Логічні рівняння

- •3.2. Змінні типу node

- •3.3. Іменовані оператори

- •3.4. Групи

- •3.4.1. Одновимірні й часові групи

- •3.4.2. Двовимірні групи

- •3.5. Таблиця істинності

- •3.6. Оператор if then

- •3.7. Оператор case

- •3.8. Базові значення логічних функцій

- •3.9. Константи

- •3.10. Оператор for generate

- •3.11. Параметри

- •3.12. Оператор if generate

- •3.13. Оператор assert

- •3.14. Примітиви

- •3.15. Прототип модуля

- •Часть 1. Основы языка ahdl. М. 2005.- 50 с.

3.13. Оператор assert

Оператор ASSERT дозволяє контролювати істинність арифметичного виразу, операндами якого є: параметри, числа, позначені арифметичні вирази, а також значення вбудованої в пакет функції USED.

Функція USED застосовується для перевірки виводів модуля. Аргументом функції є ім'я виводу модуля. Значення, що повертається:

FALSE - якщо даний вивід модуля не підключений при використанні модуля як компонента в описі більш високого рівня ієрархії;

TRUE - якщо вивід підключений.

Як ілюстрацію розглянемо наведений нижче текстовий опис, що базується на представленому раніше описі модуля IF_GEN.

PARAMETERS

(

WIDTH = 8,

MODULE_TYPE = "ADD"

);

ASSERT (WIDTH > 0)

REPORT "WIDTH of % must be more then %" Module_Type, WIDTH

SEVERITY ERROR;

SUBDESIGN ASSERT_

(

A[WIDTH..1],B[WIDTH..1] : INPUT;

RESULT[WIDTH..1], Cout : OUTPUT;

)

BEGIN

ASSERT (Module_Type =="ADD") or (Module_Type =="SUB")

REPORT "Module_Type must be ""ADD"" or ""SUB"" but not %" Module_Type

SEVERITY ERROR;

IF Module_Type == "ADD" GENERATE

(Cout,Result[]) = (GND,A[]) + (GND,B[]);

ELSE GENERATE

(Cout,Result[]) = (GND,A[]) - (GND,B[]);

END GENERATE;

END;

У наведеному прикладі оператор ASSERT використовується для контролю значення параметрів WIDTH і Module_Type.

Так, якщо значення параметра Module_Type, задане поза даним текстовим описом, відмінно від ADD і SUB (наприклад, дорівнює MIN), то компілятор сформує наступне повідомлення:

Error: Line 17, File c:\max_work\assert_.tdf:

Module_Type must be "ADD" or "SUB" but not MIN

Оскільки «рівень строгості» даного повідомлення - ERROR, то компілятор припинить роботу.

Відзначимо, що при «рівнях строгості» WARRING і INFO компілятор продовжує роботу.

3.14. Примітиви

Для використання в текстовому описі модуля примітива необхідно звернутися до вбудованого в пакет функціонального опису даного примітива й зіставити його виводам: числа, константи, змінні або виводи модуля.

У мові AHDL визначені два способи звертання до примітива:

безпосереднє звертання (In_line Reference);

присвоєння примітиву символічного імені, тобто оголошення його змінною або звертання до нього як до змінної.

Безпосереднє звертання до примітива здійснюється в такий спосіб:

вказується вихід (або внутрішня змінна) модуля, на який передається сигнал з виходу примітива;

далі ставиться знак рівності й ім'я примітива;

за ім'ям примітива в круглих дужках, через кому перераховуються передані значення:

числа,

константи,

змінні або виводи модуля, що зіставляються входам примітива;

за круглими дужками ставиться крапка з комою.

Зіставлення входів примітива з переданими значеннями може здійснюватися:

позиційно;

за іменами.

При позиційному зіставленні порядок перерахування переданих значень повинен відповідати порядку перерахування входів, використаному в описі прототипу примітива.

Вихід модуля (внутрішня змінна)=

Ім'я примітива (передане значення, передане значення,...);

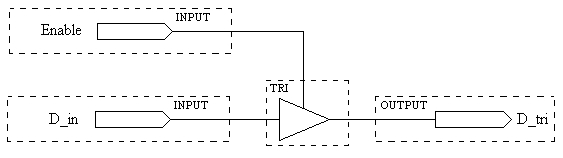

Як приклад розглянемо текстовий опис схеми, представленої на рис.18

Рис. 18

Текстовий опис:

SUBDESIGN Prim_in_line1

(

D_in, Enadle : INPUT;

D_tri : OUTPUT;

)

BEGIN

D_tri = TRI(D_in, Enable);

END;

При описі присвоєння в програмі можливі наступні варіанти, що ілюструють метод присвоєння за іменами.

D_tri = TRI(.IN = D_in, OE = Enable);

D_tri = TRI(OE = Enable,.IN = D_in);

Відзначимо, що прототипи примітивів вбудовані в пакет, і для їхнього підключення до текстового опису, оператор INCLUDE не використовується. Прототип примітива TRI у пакеті MAX+plus II заданий у такий спосіб:

FUNCTION TRI (IN, OE)

RETURNS (OUT);

При звертанні до примітива в списку переданих значень першим зазначений вхід D_in. Тому він буде з'єднаний із входом, зазначеним першим в описі прототипу примітива. Відповідно, вхід Enable модуля буде з'єднаний із входом ОЕ примітива TRI.

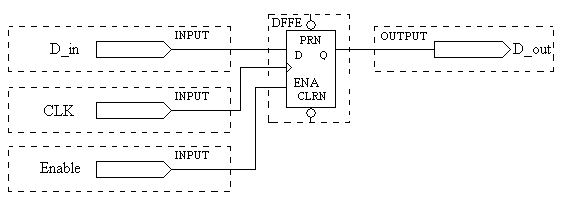

Якщо деякі із входів примітива не використовуються, то відповідні позиції в списку переданих значень повинні бути залишені порожніми. Проілюструємо це на прикладі текстового опису схеми, наведеної на рис.19.

Рис. 19.

Текстовий опис:

SUBDESIGN Prim_in_line2

(

D_in, CLK, Enadle : INPUT;

D_out : OUTPUT;

)

BEGIN

D_out = DFFE(D_in, CLK, , ,Enable);

END;

У даному прикладі використаний примітив DFFE, прототип якого в пакеті MAX+plus II має вигляд:

FUNCTION DFFE (D, CLK, CLRn, PRn, ENA)

RETURNS (Q);

Входи CLRn і PRn примітива в модулі Prim_in_line2 не використовуються, тому їхні позиції виділені в списку переданих значень комами й залишені порожніми.

При зіставленні переданих значень і входів примітива за іменами у списку значень, що передаються, через кому перераховуються: вхід і значення, що передається.

Формат запису:

Вихід модуля (внутрішня змінна) = Ім'я примітива

(ім'я виходу=передане значення, ім'я виходу = передане значення,...);

Пари можуть бути розташовані в довільному порядку, тобто незалежно від того, у якій послідовності перераховані входи в описі прототипу примітива. Невикористані входи примітива в списку переданих значень не вказуються.

Наведений нижче текстовий опис схеми, логічно еквівалентний текстовому опису модуля Prim_in_line2, ілюструє даний спосіб зіставлення.

SUBDESIGN Prim_in_line3

(

D_in, CLK, Enadle : INPUT;

D_out : OUTPUT;

)

BEGIN

D_out = DFFE(.CLK = CLK, .D = D_in, .ENA = Enable);

END;

Інший спосіб звертання до примітива — звертання до нього як до змінної.

При реалізації цього способу, примітив, насамперед, варто оголосити змінною. Для цього в розділі змінних (Variable Section) символічному імені або групі символічних імен зіставляється примітив. Оголошена в такий спосіб змінна, а так само кожна змінна з оголошеної групи змінних, буде мати той же набір виводів, що й примітив.

Звертання до конкретного виводу примітива здійснюється шляхом вказівки імені змінної, розділяючої крапки й імені виводу примітива.

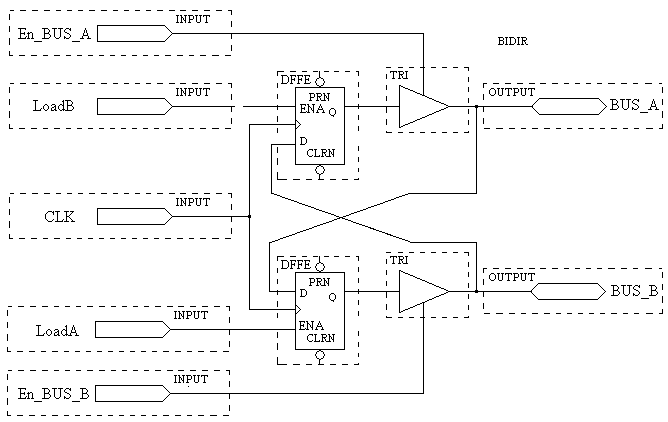

Як приклад, що ілюструє такий спосіб звертання до примітива, розглянемо текстовий опис схеми, наведеної на рис. 20.

Текстовий опис:

SUBDESIGN PRIM_VAR

(

En_BUSA,En_BUSB,Load,Load,CLK : INPUT;

BUS_A, BUS_B : BIDIR;

)

VARIABLE

RG_BUSA, RG_BUSB : DFFE;

BUF_A, BUF_B : TRI;

BEGIN

(RG_BUSA, RG_BUSB).CLK = CLK;

RG_BUSA.(D, ENA) = (BUS_B, Load);

RG_BUSB.(D, ENA) = (BUS_A, Load);

BUF_A.(IN, OE) = (RG_BUSA.Q,En_BUSA);

BUF_B.(IN, OE) = (RG_BUSB.Q,En_BUSB);

BUS_A = BUF_A.OUT;

BUS_B = BUF_B.OUT;

END;

Рис.2.20.

У даному прикладі оголошені чотири змінні. Змінні RG_BUSA і RG_BUSB позначають примітиви тригерів DFFE, а змінні BUF_A і BUF_B - примітиви буферів з Z станом.

Перше логічне рівняння текстового опису задає з'єднання входу CLK модуля із входами CLK двох тригерів. Четверте логічне рівняння визначає зв'язок виходу Q одного із тригерів (тригера, позначеного RG_BUSA) і входу En_BUSA модуля із входами IN і ОЕ буферa TRI (буфера, позначеного BUF_A). Шосте логічне рівняння описує підключення виходу буфера TRI (буфера, позначеного BUF_A) до виводу BUS_A модуля.

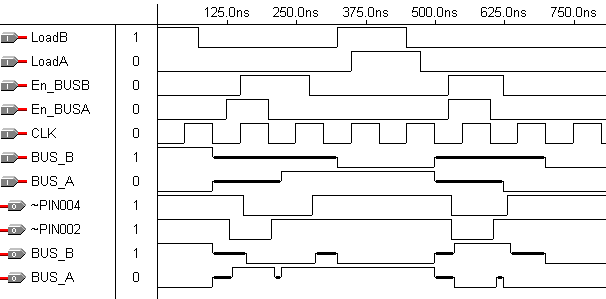

Результати моделювання створеного модуля наведені на рис. 21.

Рис. 21.