- •Мова опису апаратури ahdl

- •1. Елементи мови

- •1.1. Ключові слова й ідентифікатори

- •1.2. Символи

- •1.3. Імена

- •1.4. Групи

- •1.5. Числа

- •1.6. Вирази

- •1.6.1. Арифметичні вирази

- •1.6.2. Логічні вирази

- •1.7. Оператори

- •1.7.1. Логічні оператори

- •1.7.2. Арифметичні оператори

- •1.7.3. Оператори порівняння

- •1.8. Пріоритет виконання операцій

- •1.9. Примітиви

- •1.9.1. Примітиви буферів

- •1.9.2. Буфер ланцюгового переносу (carry)

- •1.9.3. Буфер каскадного нарощування логічної функції (cascade)

- •1.9.4. Буфер логічного розширювача (ехр)

- •1.9.5. Буфер глобального ланцюга поширення управляючого

- •1.9.6. Буфер розміщення логічного осередку (lcell),

- •1.9.7. Буфер виходу з відкритим колектором (opndrn)

- •1.9.8. Буфер розміщення логічного осередку (soft),

- •1.9.9. Буфер виходу з z станом (tri)

- •1.10. Примітиви тригерів

- •2. Структура текстового опису

- •2.1. Загальна структура

- •Include Statement.

- •2.2. Розділ оголошення операторів

- •2.2.1. Title Statement

- •2.2.2. Parameters Statement

- •2.2.3. Include Statement

- •2.2.4. Constant Statement

- •2.2.5. Define Statement

- •2.2.6. Function Prototype Statement

- •2.2.7. Options Statement

- •2.2.8. Assert Statement

- •2.3. Subdesign Section

- •2.4. Variable Section

- •2.5. Logic Section

- •3. Застосування конструкцій мови

- •3.1. Логічні рівняння

- •3.2. Змінні типу node

- •3.3. Іменовані оператори

- •3.4. Групи

- •3.4.1. Одновимірні й часові групи

- •3.4.2. Двовимірні групи

- •3.5. Таблиця істинності

- •3.6. Оператор if then

- •3.7. Оператор case

- •3.8. Базові значення логічних функцій

- •3.9. Константи

- •3.10. Оператор for generate

- •3.11. Параметри

- •3.12. Оператор if generate

- •3.13. Оператор assert

- •3.14. Примітиви

- •3.15. Прототип модуля

- •Часть 1. Основы языка ahdl. М. 2005.- 50 с.

3.9. Константи

Використання в текстовому описі символічних імен замість фіксованих числових значень (тобто використання констант) дозволяє:

зробити текстовий опис більше наочним;

спростити внесення змін, пов'язаних зі зміною фіксованих числових значень.

Нижче представлений опис адресного декодера, у якому базові значення адрес задаються константами.

CONSTANT ADR_WIDTH =8;

CONSTANT NUMBER_IO =16;

CONSTANT IO_ADR =2^ADR_WIDTH-NUMBER_IO;

CONSTANT COMMAND =IO_ADR;

CONSTANT DAC =IO_ADR+1;

CONSTANT ADC =IO_ADR+2;

SUBDESIGN CONSTANT_

(

ADR[ADR_WIDTH..0], READ, WRITE : INPUT;

WR_COMMAND, RD_COMMAND, RD_ADC, WR_DAC : OUTPUT;

)

BEGIN

IF ADR[]==COMMAND

THEN

IF READ==1

THEN RD_COMMAND=VCC;

ELSIF WRITE==1

THEN WR_COMMAND=VCC;

END IF;

ELSIF ADR[]==ADC

THEN

IF READ==1

THEN RD_ADC=VCC;

END IF;

ELSIF ADR[]==DAC

THEN

IF WRITE==1

THEN WR_DAC=VCC;

END IF;

END IF;

END;

У наведеному прикладі базове значення адреси вводу/виводу (IO_ADR) визначено через розрядність шини адреси (ADR_WIDTH) і число адрес, зарезервованих під ввід/вивід (Number_IO). Адреси регістрів: команд (Command), АЦП (ADC), ЦАП (DAC) задані зсувами від базової адреси (IO_ADR).

Результати моделювання адресного декодера наведені на рис. 14.

Рис. 14.

Відмітимо, що для адаптації адресного декодера під іншу ширину адресної шини в текстовому описі досить змінити значення тільки однієї константи - ADR_WIDTH.

3.10. Оператор for generate

Оператор FOR GENERATE (оператор циклу) дозволяє спростити запис послідовності подібних логічних рівнянь і операторів, мови AHDL.

Оператор циклу має вигляд:

FOR __index_variable IN __range GENERATE

__statement;

__statement;

END GENERATE;.

Оператор задається в такий спосіб:

За ключовим словом FOR вказується символічне ім'я внутрішньої змінної оператора. Це ім'я не може збігатися з ім'ям констант, параметрів або змінних, використовуваних у текстовому описі.

Ключові слова IN ... ТО ... визначають границі зміни значень внутрішньої змінної оператора.

Границі задаються арифметичними виразами.

За ключовим словом GENERATE слідують логічні рівняння й оператори мови AHDL.

Оператор кінчається ключовими словами END GENERATE, за яким слідує крапка з комою (;).

Проілюструємо використання оператора FOR GENERATE для опису на вентильному рівні N-розрядного суматора, що має вхід і вихід переносу.

CONSTANT NUM_OF_ADDERS=8;

SUBDESIGN FOR_GEN

(

a[NUM_OF_ADDERS..1], b[NUM_OF_ADDERS..1], cin : INPUT;

c[NUM_OF_ADDERS..1], cout : OUTPUT;

)

VARIABLE

carry_out [(NUM_OF_ADDERS+1)..1] : NODE;

BEGIN

carry_out[1]=cin;

FOR i IN 1 TO NUM_OF_ADDERS GENERATE

c[i]=(a[i] $ b[i]) $ carry_out[i];

carry_out[i+1] = a[i] & b[i] # carry_out[i] & (a[i] $ b[i]);

END GENERATE;

cout = carry_out[NUM_OF_ADDERS+1];

END;

Опис, заданий оператором FOR GENERATE при NUM_OF_ADDERS = 4 відповідає наступним рівнянням:

c[1] = a[1] $ b[1] $ carry_out[1];

carry_out[2] = a[1] & b[1] # carry_out[1] & (a[1] $ b[1]);

с[2] = a[2] $ b[2] $ carry_out[2];

carry _out[3] = a[2] & b[2] # carry_out[2] & (a[2] $ b[2]);

с[3] = a[3] $ b[3] $ carry_out[3];

carry _out[4] = a[3] & b[3] # carry_out[3] & (a[3] $ b[3]);

c[4] = a[4] $ b[4] $ carry_out[4];

carry_out[5] = a[4] & b[4] # carry_out[4] & (a[4] $ b[4]);

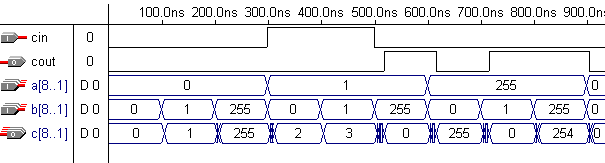

Результати моделювання описаного суматора при NUM_0F_ADDERS=8 наведені на рис. 15

Рис. 15.

Відмітимо, що для зміни розрядності суматора досить у текстовому описі змінити значення константи NUM_OF_ADDERS.