- •Оренбург

- •Содержание

- •1 Задания на курсовое проектирование

- •2 Методические указания по выполнению схемотехнической кд и базы данных для разработки печатной платы

- •3 Методические указания по выполнению разработки кд конструкции узла цифрового автомата

- •3.1 Исходные данные

- •3.2 Методические указания по разработке пп

- •4 Описание методики использования схемного редактора Schematic

- •4.1 Настройка опций p-cad Scphematic

- •4.1.1 Настройка в окне Configure

- •4.1.2 Настройка масштабной сетки

- •4.1.3 Настройка в окне Display

- •4.1.4 Настройка в окнах Current Wire и Current Line

- •4.1.5 Настройка в окне Text Style

- •4.2 Создание принципиальных схем

- •4.2.1 Загрузка библиотек

- •4.2.2 Размещение компонентов на схеме

- •4.2.3 Размещение электрических цепей

- •4.2.4 Редактирование схемы

- •4.2.5 Верификация схемы erc

- •4.3 Оформление схемотехнической кд

- •4.3.1 Создание и заполнение угловых штампов

- •4.3.2 Сохранение проекта

- •4.3.3 Вывод схемы на печать

- •4.3.4 Создание списка соединений

- •5 Описание методики по использованию редактора печатных плат pcb

- •5.1 Настройка опций p-cad рсв

- •5.1.1 Задание глобальных параметров проекта

- •5.1.2 Настройка параметров дисплея

- •5.1.3 Структура слоев печатной платы

- •5.1.4 Ширина проводников

- •5.1.5 Стеки контактных площадок и переходных отверстий

- •5.1.6 Выбор стиля текста

- •5.1.7 Подключение библиотек

- •5.2 Размещение компонентов на пп

- •5.2.1 Упаковка схемы на печатную плату

- •5.2.2 Размещение компонентов на плате

- •5.3 Трассировка соединений

- •5.3.1 Задание правил проектирования

- •5.3.3 Интерактивная трассировка соединений

- •5.3.4 Автоматическая трассировка с применением Quick Route

- •5.3.5 Проверка печатной платы drc

- •5.4 Выполнение и сохранение кд

- •5.4.1 Вывод на принтер и плоттер

- •5.4.2 Сохранение проекта

- •5.4.3 Оформление кд проекта пп

- •6.5 Требования к формированию комплекта кд

- •Список использованных источников

4.2.4 Редактирование схемы

4.2.4.1 Для перемещения компонента или цепи нужно выбрать их щелчком курсора (левая клавиша мыши) и затем перемещать движением мыши. Если одновременно нужно переместить несколько объектов, например, компонент и связанные с ним сегменты цепей, то дополнительные объекты выбирают щелчком курсора с одновременным нажатием и удерживанием клавиши Ctrl. Выделенная группа объектов перемещается как единое целое. Если после перемещения сегментов цепей часть из них будет расположена неаккуратно, щелчком курсора выбирают отдельный сегмент и перемещают его вершину. Выбор для редактирования элемента сложного объекта производится щелчком левой клавиши мыши при одновременном нажатии кнопки Shift.

4.2.4.2 Скопировать выделенную группу объектов можно последовательным выполнением команд Edit>Copy, Edit>Past или, что более удобно, удерживанием клавиши Alt при перемещении мыши. При копировании группы объектов входящие в них глобальные цепи не изменяют своих имен (к глобальным относятся цепи, к которым подключены порты или выводы компонентов, имеющие тип Power), а остальные цепи переименовываются. Компонентам присваиваются новые позиционные обозначения.

4.2.4.3

Все компоненты можно удалять следующим

образом. В режиме команды Options>Block

Select

(или кнопка

![]() ) с помощью мыши встают на удаляемый

элемент и нажатием левой клавиши выделяют

цветом этот элемент и нажимают клавишу

Delete.

Если одновременно

нужно удалить несколько объектов,

например компонент и связанные с ним

сегменты цепей, то дополнительные

объекты выбирают щелчком курсора с

одновременным нажатием и удерживанием

клавиши Ctrl,

а затем

нажать клавишу Delete.

) с помощью мыши встают на удаляемый

элемент и нажатием левой клавиши выделяют

цветом этот элемент и нажимают клавишу

Delete.

Если одновременно

нужно удалить несколько объектов,

например компонент и связанные с ним

сегменты цепей, то дополнительные

объекты выбирают щелчком курсора с

одновременным нажатием и удерживанием

клавиши Ctrl,

а затем

нажать клавишу Delete.

4.2.4.4 Во всех случаях ошибочных действий при редактировании можно сделать «откат», как назад, так и вперед, используя для этого команды соответственно Edit>Undo и Edit>Redo.

4.2.5 Верификация схемы erc

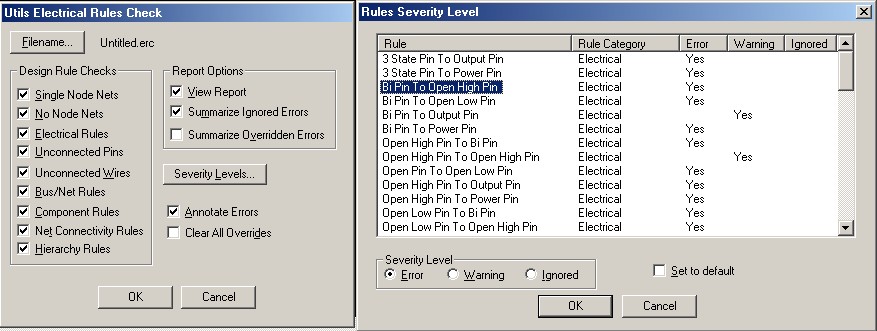

После создания принципиальной электрической схемы целесообразно выявить синтаксические ошибки, исправить их и только после этого перейти к разработке ПП. Проверку схемы выполняют по команде Utils>ERC (Electrical Rules Check). В основном меню этой команды (рисунок 4.11, а) задают перечень проверок, результаты которых приводятся в текстовом отчете:

Single Node Nets — цепи, имеющие единственный узел;

No Node Nets — цепи, не имеющие узлов;

Electrical Rules — электрические ошибки, когда соединяются выводы несовместимых типов (например, соединяются два выходных вывода или выходной вывод подключается к выводу источника питания);

Unconnected Pins — неподключенные выводы компонентов;

Unconnected Wires — неподключенные (плавающие) цепи;

Bus/Net Errors — входящие в состав шины цепи, встречающиеся только один раз (т. е. они входят в шины, но не выходят из них);

Component Rules — компоненты, расположенные поверх других компонентов;

Net Connectivity Rules — неправильное подключение цепей земли и питания, которое может быть вызвано одной их трех причин:

символ источника питания подключен к цепи, имеющей другое имя;

скрытый глобальный вывод компонента подсоединен к цепи, имя которой не совпадает с именем по умолчанию;

две цепи, например, А и В объединены под именем А, в то время как цепь В существует отдельно; при появлении этого предупреждения необходимо с помощью команды Edit>Nets переименовать цепи;

Hierarchy Rules — ошибки иерархической структуры.

Степень серьезности отдельных ошибок (Error, Warning или Ignored) назначается в диалоговом окне (рисунок 4.11, б), открываемом после нажатия на панель Severity Level (только для опытных специалистов). Кроме того, в меню, показанном на рисунке 4.11, а, необходимо включить опции View Report (Просмотр отчета сообщений об ошибках) и Annotate Errors (Индикация ошибок на схеме).

а) б)

Рисунок 4.11 – Настройка конфигурации ERC: выбор перечня (а)

и назначение типов ошибок (б)

Сообщения об ошибках заносятся в файл <имя схемы>.ERC, изменение этого имени производят после выбора панели Filename.

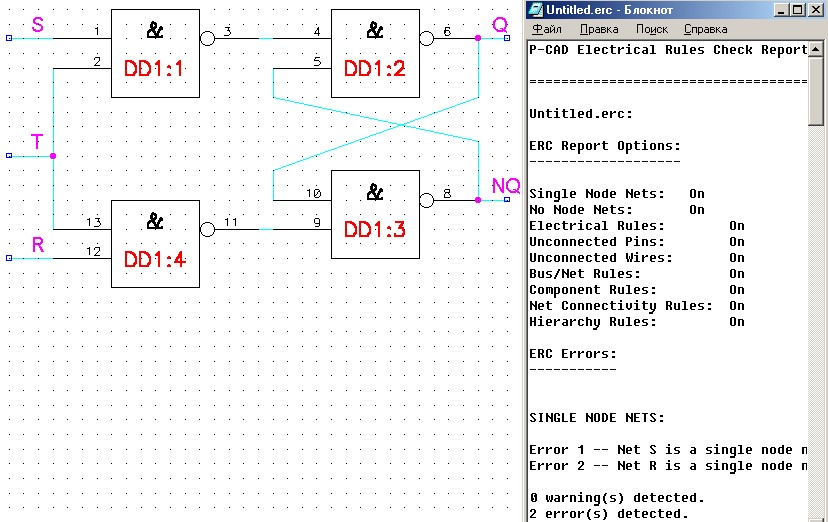

Поиск ошибок в соответствии с заданной конфигурацией начинается после нажатия панели ОК. Информация об ошибках помечается на схеме индикаторами и выводится в текстовый отчет (рисунок 4.12, б).

В текстовом файле с расширением имени *.ERC приводится конфигурация настройки программы ERC, перечень всех ошибок и предупреждений и статистика и координаты ошибок. На рисунке 4.12, б приведен пример такого файла. В частности, несмотря на то, что схема RST-триггера на рисунке 4.11 собрана без ошибок, для нее по входам RS отсутствуют коннекторы (разъемы или контактные площадки), о чем сообщает программа ERC.

Координаты ошибок приводятся в той системе единиц, которая выбрана в меню команды Options>Configure.

а) б)

Рисунок 4.12 – Диагностическое сообщение об ошибках