- •Оренбург

- •Содержание

- •1 Задания на курсовое проектирование

- •2 Методические указания по выполнению схемотехнической кд и базы данных для разработки печатной платы

- •3 Методические указания по выполнению разработки кд конструкции узла цифрового автомата

- •3.1 Исходные данные

- •3.2 Методические указания по разработке пп

- •4 Описание методики использования схемного редактора Schematic

- •4.1 Настройка опций p-cad Scphematic

- •4.1.1 Настройка в окне Configure

- •4.1.2 Настройка масштабной сетки

- •4.1.3 Настройка в окне Display

- •4.1.4 Настройка в окнах Current Wire и Current Line

- •4.1.5 Настройка в окне Text Style

- •4.2 Создание принципиальных схем

- •4.2.1 Загрузка библиотек

- •4.2.2 Размещение компонентов на схеме

- •4.2.3 Размещение электрических цепей

- •4.2.4 Редактирование схемы

- •4.2.5 Верификация схемы erc

- •4.3 Оформление схемотехнической кд

- •4.3.1 Создание и заполнение угловых штампов

- •4.3.2 Сохранение проекта

- •4.3.3 Вывод схемы на печать

- •4.3.4 Создание списка соединений

- •5 Описание методики по использованию редактора печатных плат pcb

- •5.1 Настройка опций p-cad рсв

- •5.1.1 Задание глобальных параметров проекта

- •5.1.2 Настройка параметров дисплея

- •5.1.3 Структура слоев печатной платы

- •5.1.4 Ширина проводников

- •5.1.5 Стеки контактных площадок и переходных отверстий

- •5.1.6 Выбор стиля текста

- •5.1.7 Подключение библиотек

- •5.2 Размещение компонентов на пп

- •5.2.1 Упаковка схемы на печатную плату

- •5.2.2 Размещение компонентов на плате

- •5.3 Трассировка соединений

- •5.3.1 Задание правил проектирования

- •5.3.3 Интерактивная трассировка соединений

- •5.3.4 Автоматическая трассировка с применением Quick Route

- •5.3.5 Проверка печатной платы drc

- •5.4 Выполнение и сохранение кд

- •5.4.1 Вывод на принтер и плоттер

- •5.4.2 Сохранение проекта

- •5.4.3 Оформление кд проекта пп

- •6.5 Требования к формированию комплекта кд

- •Список использованных источников

5.2.2 Размещение компонентов на плате

После загрузки списка соединений (упаковки схемы) на ПП приступают к размещению компонентов внутри контура ПП, площадь которого рассчитывают заранее.

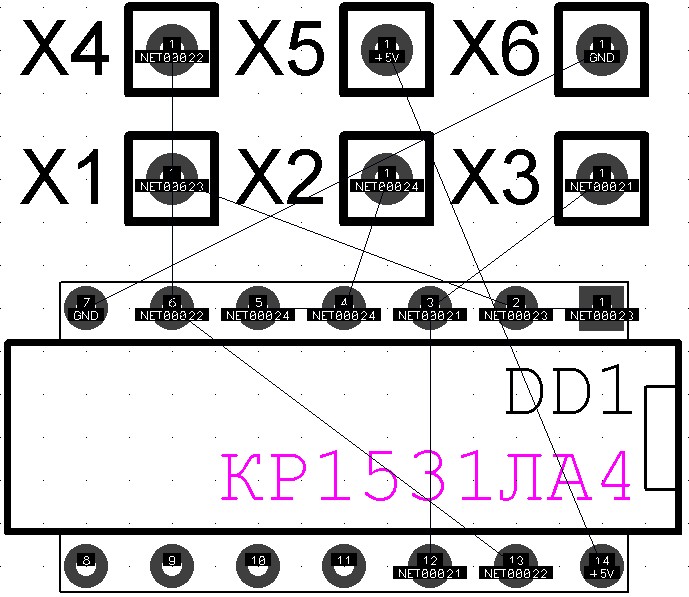

Рисунок 5.10 – Результат упаковки схемы на ПП

5.2.2.1 Нажатие клавиши R поворачивает выбранный объект против часовой стрелки на 90°.

5.2.2.2 Нажатие клавиши F зеркально отображает объекты относительно оси Y и одновременно переносит компоненты на противоположную сторону ПП (первоначально компоненты обычно устанавливаются на верхнюю сторону ПП – Тор); одновременно с этим переносится информация, содержащаяся на парных слоях: Тор и Bottom и т. п.

5.2.2.3 Линии электрических связей, перемещаемые с помощью мыши вместе с выделенными предварительно компонентами, помогают правильно их разместить.

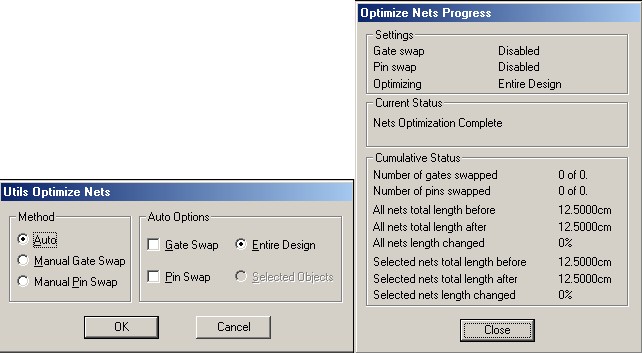

5.2.2.4 После завершения размещения компонентов полезно выполнить минимизацию длин соединений путем перестановки логически эквивалентных секций компонентов и их выводов по команде Utils>Optimize Nets. В меню команды (рисунок 5.11) выбирают метод оптимизации:

Auto — автоматическая оптимизация;

Entire Design — оптимизация всего проекта;

Логически эквивалентные секции переставляются не только в пределах одного корпуса компонента, но и в разных корпусах компонентов (ИС, резисторы, конденсаторы), имеющих одинаковый корпус и одинаковое значение параметра Value. Перестановка в отдельных компонентах запрещается с помощью атрибута NoSwap (Yes). Результаты перестановок, выполненных в автоматическом режиме, отражаются в отчете (рисунок 5.12 – отчет о минимизации схемы, представленной на рисунке 5.10).

Рисунок 5.11 – Окно оптимизации Рисунок 5.12 – Отчет автоматической

соединений оптимизации соединений

5.3 Трассировка соединений

5.3.1 Задание правил проектирования

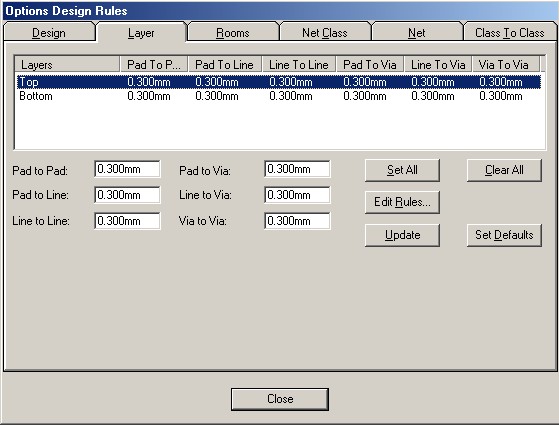

5.3.1.1 Перед началом трассировки в меню Options>Grids задают необходимый шаг трассировочной сетки – желательно кратным 2,5 мм: 2.5 мм; 1.25 мм; 0,625 мм.

5.3.1.2 В заключение подготовки к трассировке по команде Options>Design Rules на закладке Layers устанавливают глобальные допустимые зазоры для каждого слоя трассировки, как показано на рисунке 5.13 (если совпадают с рисунком, то не редактировать):

Line to Line — проводникпроводник;

Pad to Via — КППО;

Line to Via — проводникПО;

Via to Via — ПОПО.

Значения зазоров вводят в соответствующие графы и затем нажатием клавиши Update они переносятся на выбранные слои.

Выбор закладок Design, Net Class, Rooms. Net и Class To Class позволяет задать остальные правила трассировки.

Примечание. Для простоты и надежности трассировок соединений при необходимости рекомендуется обходиться только глобальными настройками, вводимыми на закладке Layers (рисунок 5.13); настройки остальных закладок оставить по умолчанию.

Рисунок 5.13 – Задание допустимых зазоров трассировки

5.3.3 Интерактивная трассировка соединений

По

команде Route>Interactive

(кнопка

![]() ) выполняется

интерактивная трассировка проводников.

) выполняется

интерактивная трассировка проводников.

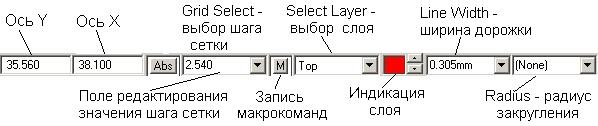

Перед началом трассировки какого-нибудь проводника задают его ширину (п. 5.1.4) и выбирают нужный слой (п. 5.1.3). Причем делать это удобнее всего с помощью нижней линейки инструментов (рисунок 5.14).

Рисунок 5.14 – Нижняя линейка инструментов редактора ПП P-CAD PCB

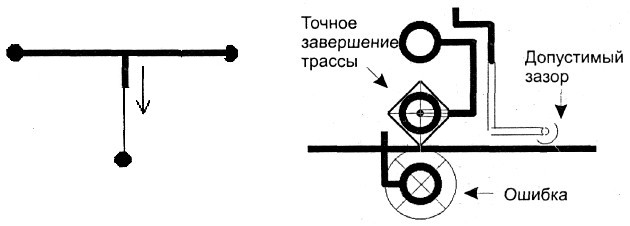

Трассу начинают щелчком курсора на КП компонента, имеющую электрическую связь (в любой ее точке, необязательно в центре), или в любой точке ранее проложенной трассы. Трассу прокладывают движением курсора при нажатой левой клавише мыши, при этом автоматически огибаются препятствия (проводники, КП, ПО и области металлизации), соблюдаются допустимые зазоры (рисунок 5.15, б).

Отпустив

левую кнопку мыши, фиксируют проложенный

сегмент трассы. При этом рекомендуется

включить режим Push

Traces

(кнопка

![]() ) — режим отталкивания мешающих

проводников;

) — режим отталкивания мешающих

проводников;

а) б)

Рисунок 5.15 – Образование Т-образных проводников (а)

и индикация результатов трассировки (б)

При смене в процессе прокладки трассы текущего слоя нажатием клавиш L (или Shift+L) или с помощью строки состояний (рисунок 5.14) трасса продолжается на другом слое, при этом автоматически вставляется ПО текущего типа, заданное заранее по команде Options>Via Style.

Не прерывая прокладку трассы, можно изменить ширину проводника по команде Options>Current Line или в строке состояний (рисунок 5.14).

Нарушение

зазора между трассой проводника и

выводом компонента, ПО или трассой

другой цепи отмечается как ошибка в

виде круга с перекрестием (рисунок 5.15,

б),

если включен режим Online

DRC

(кнопка

![]() ).

).

Нажимая

клавишу Backspace,

можно последовательно стереть проложенные

сегменты трассы одновременно с

индикаторами ошибок. По команде

Edit>Undo

(«откат» – кнопка

![]() ) можно стереть целиком всю последнюю

трассу после завершения ее прокладки.

По команде Edit>Redo

(«откат отката» – кнопка

) можно стереть целиком всю последнюю

трассу после завершения ее прокладки.

По команде Edit>Redo

(«откат отката» – кнопка

![]() )

можно восстановить ошибочно стертую

последнюю трассу.

)

можно восстановить ошибочно стертую

последнюю трассу.

Нажатием косой черты «/» или «\» прекращают прокладку трассы без ее завершения.

Когда в процессе прокладки трассы левую кнопку мыши отпускают в точке окончания линии электрической связи, прокладка трассы завершается и можно переходить к прокладке следующей. Завершение трассы точно на контактной площадке пункта назначения обозначается ромбом с перекрестьем (рисунок 5.15, б).