- •Лекція №1. Імпульсна техніка.

- •Iмпульси характеризуються слiдуючими параметрами:

- •Ключовий режим праці біполярних транзисторів.

- •Лекція №2. Можливості цифрової техніки. Загальна характеристика цифрових логічних інтегральних мікросхем.

- •Основні логічні функції.

- •Лекція №3. Схеми цифрових (логічних) елементів

- •Елементи інтегральної інжекційної логіки і2л.

- •Елементи емітерно (езл).-зв’язаної логіки.

- •Типова схема або-ні на мдп - транзисторах.

- •Лекція №5. Тригери

- •Симетричні тригери на біполярних транзисторах.

- •Робота схеми.

- •Несиметричні тригери на біполярних транзисторах. Тригер Шмітта.

- •Тригери на польових транзисторах.

- •Тригери на цифрових інтегральних схемах.

- •Лекція №7.

- •Функціональна схема rs - тригера на двохвхідних логічних елементах або-ні.

- •Синхронні тригери.

- •Лекція №9. Лічильники.

- •Двійково-десяткові лічильники.

- •Дешифратори.

- •Лекція №11

- •Автоколивальні мультивібратори.

- •Симетричний мультивібратор в інтегральному виконані.

- •Мультивібратори на польових транзисторах

- •Мал. 154. Мультивібратор на

- •Мультивібратори на операційних підсилювачах.

- •Несиметричний мультивібратор на оп

- •Лекція №12

- •Мультивібратор на логічних елементах або–ні.

- •Мультивібратори на логічних елементах і – ні.

- •Одновібратори.

- •Одновібратор в інтегральному виконанні

- •Можливо створити автоколивальні мультивібратори з колекторно - базовим позитивним зворотним зв’язком, якщо його примусово закрити в одному з тимчасово стійких станів та перетворити в стійке.

- •Мал. 162. Часові діаграми роботи

- •Одновібратор на логічних елементах і – ні

- •Лекція №13.

- •II частина. Мікропроцесори.

- •Структура мікро - еом і її інформаційне забезпечення.

- •Лекція №14 іі частина.

- •Іі частина.

- •Лекція № 17.

- •II частина.

Основні логічні функції.

НІ - логічне заперечення або інверсія.

![]()

АБО - диз’юнкція (логічне складання). Умовне позначення:

![]()

І - кон’юнкція (логічне помноження)

умовне позначення

![]()

На основі цих функцій можна реалізувати будь-яку функцію.

І-НІ - заперечення кон’юнкції (штрих Шеффера).

умовне позначення

![]()

Сигнал на виході відсутній тільки тоді, коли сигнали одночасно поступають на всі входи.

АБО-НІ заперечення логічної суми вхідних сигналів (заперечення диз’юнкції).

Працює як НІ з декількома входами.

Умовне позначення

Лекція №3. Схеми цифрових (логічних) елементів

Логічні елементи служать для виконання найпростіших логічних операцій над цифровою інформацією.

Існують 4 типи логічних елементів:

з діодно-транзисторною логікою (ДТЛ);

з транзисторною логікою і резистивним зв’язком (РТЛ);

з транзисторно-транзисторною логікою (ТТЛ);

з транзисторною логікою (ТЛ).

Схема НІ. Звичайно будують на основі транзисторних інвертуючих підсилювачів.

а) б)

Мал. 98. Схема “НІ” на логіки

ТЛ (а) та її часова (б) діаграма.

Схема ТЛ. Працює як звичайний ключ.

При відсутності вхідного сигналу транзистор закритий від’ємним зміщенням на базу від джерела Uд.ж.2.

При подачі на схему додатного (високий рівень1) імпульсу транзистор відкривається і на виході з’являється від’ємний імпульс (низький рівень - 0).

-

x

y

0

1

1

0

Таким чином виконується операція інверсії (логічного заперечення), тому НІ називають інвертором.

Схема АБО - частіше в інтегральному виконанні виконується на транзисторах (ТЛ).

VT1 та VT2 вмикаються паралельно на загальне емітерне навантаження.

Використовується в мікросхемах 137 та 138 серії.

Мал. 99. Схема АБО на логіці ТЛ.

В початковому стані обидва транзистори закриті від’ємним зміщенням на базі від ЕБ. Оскільки емітерний повторювач не підсилює напругу і не повертає фази вхідних сигналів, то при надходженні додатного сигналу (1) на будь-який вхід - відповідний транзистор відкривається, та на виході отримуємо такий же додатний потенціал (1) того же рівня.

Схема АБО може бути представлена діодною логікою.

Мал. 100. Схема АБО на ДЛ.

Логічний елемент приєднаний до від’ємного полюсу джерела живлення -ЕК.

Діоди відмикаються при більш від’ємних потенціалах на їх катодах.

Тому -ЕК зручно прийняти за 0, а більш від’ємні потенціали входів

за 1.

Схема І. Логічну схему І в інтегральному виконанні звичайно виконують на діодах.

а) б)

Мал. 101. Схема І на ТЛ (а),

її часова діаграма (б).

Імпульси на входи поступають в різному сполученні.

R- струмообмежуючий опір.

R - oбирається достатньо великим, щоб джерело живлення ЕК працювало в режимі джерела струму.

В цьому випадку незалежно від числа діодів, що відкриваються, крізь R проходить один і той же струм.

Будь який з діодів відкривається, коли потенціал на його аноді більш додатній, ніж -ЕК.

В цьому випадку за 1 приймається -EK, а більш додатні потенціали відповідно 0.

Для компенсації послаблення сигналу, або для розв’язки з навантаженням, на виході такої схеми вмикається транзистор (ДТЛ). При низькому потенціалі на всіх входах (0) всі діоди відкриті. При цьому крізь всі резистори R1 та R2 та діоди протікає струм від джерела живлення Uд.ж., замикаючись крізь входи джерел вхідних сигналів.

Мал. 102. Схема І-НІ на ДТЛ.

Так як сумарний опір R1+R2 набагато більше опору діодів, зміщених в прямому напрямку, напруга на виході діодів (вивід бази транзистора), а також на виході транзистора (вивід емітера) близька до 0. При надходженні на один із входів потенціалу U > Uд.ж. (1), відповідний діод закривається, проте інші діоди відкриті, а тому коли на виході зберігається 0.

Тільки коли на всіх входах з’явиться 1, всі діоди закриються, струми діодів крізь R1 та R2 дорівнюватимуть 0 і напруга на виході діодів (тобто виході схеми) стрибком досягне значення +Uд.ж. (1). Якщо логічний елемент І має більше входів, ніж сигналів, то входи, що не використовуються, з’єднують з “плюсом” джерела живлення. Ці діоди будуть завжди закриті, що зменшує кількість завад на виході схеми.

Схема І-НІ. В цій схемі сигнал на виході відсутній тільки тоді (0), коли сигнали одночасно надходять на всі входи. В інших випадках на виході сигнал відповідає 1. Звичайно виконуються за типом ДТЛ та ТТЛ.

В першій схемі з трьома входами з розширенням по І (мікросхема К1ЛБ091А-Г) операцію І здійснює діодна частина (VD1-VD3) з резисторами R1, R2 та транзистором VT1.

Підсилювальний каскад-інвертор на транзисторі VT2 виконує операцію НІ.

Мал. 103. Схема І-НІ на ДТЛ.

Діод VD5, що зв’язує діодну частину з інвертором, служить для надійного запирання транзистору VT2, потенціал бази якого нижче потенціалу точки А на величину прямого падіння напруги на діоді.

При низькому потенціалі на всіх входах (0) діоди VD1-VD3 відкриті, забезпечуючи потенціал точки А близьким до 0. Транзистор VT2 завдяки наявності діоду VD5 надійно закритий і потенціал колектора (на виході схеми) практично дорівнює Uд.ж.2 (1). 1 на виході буде існувати до тих пір, доки на всі входи не надійдуть сигнали високого рівня (1). При цьому діоди VD1-VD3 закриються , потенціал точки А підвищиться до +Uд.ж.1, а транзистор ввійде в режим насичення з низьким потенціалом колектора (0), що відповідає логічній операції І-НІ.

Схема ТТЛ. (мікросхема 134ЛА2А-Б) характеризується більш високою швидкодією.

Мал. 104. Схема І-НІ на ТТЛ.

В цій схемі операцію І реалізує багатоемітерний транзистор VT1, а операцію НІ - складний інвертор на транзисторах VT2-VT4. Якщо на всі емітери транзистора VT1 надходить високий потенціал (1), то всі переходи емітер-база зміщуються в зворотному напрямку (закриті), а перехід база-колектор за рахунок напруги джерела Uд.ж. - в прямому. Струм колекторного переходу VT1, який протікає крізь перехід емітер-база транзистора VT2, введе останній в режим насичення. Завдяки цьому транзистор VT3 закритий низьким потенціалом колектора насиченого транзистора VT2, а транзистор VT4 - насичений через наявність високого потенціалу в т. А (на його вході). Це забезпечує майже 0 потенціал на виході схеми (0).

Якщо хоча б на один вхід схеми поступає сигнал логічного 0, то транзистор VT2 ввійде в режим відсічки, забезпечує відкривання високим потенціалом колектора транзистора VT3, який в цьому випадку працює як емітерний повторювач.

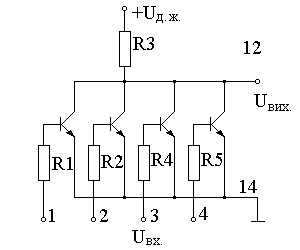

Схема АБО-НІ.

Мал. 105. Схема АБО-НІ на ТЛ.

Транзисторний варіант схеми АБО-НІ на 4 входи (один елемент мікросхеми 115ЛЕ2), виконаний за типом ТЛ. Схема працює як елемент НІ з кількома входами. При низькому потенціалі на входах (0) транзистори закриті і на виході маємо 1 (напруга +Uд.ж.). Якщо хоча б до одного з входів прикласти високий потенціал (1), то відповідний цьому входу транзистор ввійде в режим насичення, і потенціал колекторів всіх транзисторів (вихід схеми) знизиться до 0 (0). Таким чином реалізується логічна операція АБО-НІ.

В цій схемі операцію І реалізує багатоемітерний транзистор VT1, а операцію НІ - складний інвертор на транзисторах VT2-VT4. Якщо на всі емітери транзистора VT1 надходить високий потенціал (1), то всі переходи емітер-база зміщуються в зворотному напрямку (закриті), а перехід база-колектор за рахунок напруги джерела Uд.ж. - в прямому. Струм колекторного переходу VT1, який протікає крізь перехід емітер-база транзистора VT2, введе останній в режим насичення. Завдяки цьому транзистор VT3 закритий низьким потенціалом колектора насиченого транзистора VT2, а транзистор VT4 - насичений через наявність високого потенціалу в т. А (на його вході). Це забезпечує майже 0 потенціал на виході схеми (0).

Якщо хоча б на один вхід схеми поступає сигнал логічного 0, то транзистор VT2 ввійде в режим відсічки, забезпечує відкривання високим потенціалом колектора транзистора VT3, який в цьому випадку працює як емітерний повторювач.

Схема АБО-НІ.

Мал. 105. Схема АБО-НІ на ТЛ.

Транзисторний варіант схеми АБО-НІ на 4 входи (один елемент мікросхеми 115ЛЕ2), виконаний за типом ТЛ. Схема працює як елемент НІ з кількома входами. При низькому потенціалі на входах (0) транзистори закриті і на виході маємо 1 (напруга +Uд.ж.). Якщо хоча б до одного з входів прикласти високий потенціал (1), то відповідний цьому входу транзистор ввійде в режим насичення, і потенціал колекторів всіх транзисторів (вихід схеми) знизиться до 0 (0). Таким чином реалізується логічна операція АБО-НІ.

Лекція №4.

Елементарна база статичних цифрових мікросхем.

Елементи ТТЛ:

ТТЛ з простим інвертором.

Мал. 106. Схема І-НІ на ТТЛ.

Схема елемента складається з багатоемітерного транзистора VT1, виконуючого логічну операцію І, та транзисторного ключа-інвертора VT2.

На виході елемента реалізується функція І-НІ.

ТТЛ з складним інвертором.

Використання в елементах ТТЛ складного інвертора дозволяє значною мірою підвищити завадостійкість, а також збільшити швидкодію схеми при роботі на значне ємнісне навантаження.

Мал. 107. Схема І-НІ на ТТЛ з складним інвертором.

Складний інвертор складається з фазорозщеплюючого (VT1, VT4, R1, R2,R4), та вихідного (VT2, VT3, R3, VD1) каскадів.

Фазорозщеплюючий каскад забезпечує керуючі сигнали для противофазного переключення вихідних транзисторів. Резистор R3 використовується для обмеження струму у вихідному каскаді під час вимикання схеми, коли транзистор VT2 ще знаходиться в режимі насичення, а транзистор VT3 вже відімкнувся.