- •Триггер rs-типа. Принцип работы. Временные диаграммы. Функциональная схема. Параметры. Примеры использования.

- •Триггер d-типа. Принцип работы. Временная диаграмма. Функциональная схема. Параметры. Примеры использования.

- •Триггер jk- типа. Принцип работы. Временная диаграмма. Функциональная схема. Параметры. П римеры использования.

- •Тактируемые триггеры. Особенности. Параметры. Временные диаграммы.

- •Параллельные регистры. Функциональная схема. Установка нулевого состояния. Сигналы управления.

- •Параллельные регистры сдвига

- •Последовательные (сдвигающие) регистры. Функциональные схемы. Временная диаграмма. Сигналы управления. Быстродействие.

- •Счетчики на счетных триггерах. Назначение. Параметры. Функциональные схемы.

- •Дешифраторы. Назначение. Таблица состояний. Функциональная схема. Параметры. Примеры использования.

- •Шифраторы. Назначение. Таблица состояний. Функциональная схема. Параметры. Примеры использования.

- •Мультиплексоры. Принципы работы мультиплексора. Таблица состояния. Функциональная схема мультиплексора 4 – 1. Параметры.

- •Демультиплексоры. Принцип работы. Таблица состояний. Функциональные схемы. Параметры. Примеры использования.

- •Основные понятия в виде запоминающихся устройств.

- •Статическое озу. Функциональная схема. Однокоординатная матрица. Схема запоминающей ячейки.

- •Динамическое озу. Структура запоминающей ячейки.

- •Общие сведения структуры пзу. Масочные пзу.

Последовательные (сдвигающие) регистры. Функциональные схемы. Временная диаграмма. Сигналы управления. Быстродействие.

П оследовательные

регистры

оследовательные

регистры

Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов.

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

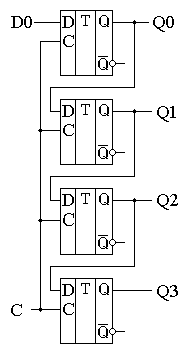

Принципиальная схема последовательного регистра, собранного на основе D‑триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 3.

В

Рисунок

3. Схема последовательного регистра.

В ходы

синхронизации в последовательных

регистрах, как и в параллельных,

объединяются. Это обеспечивает

одновременность смены состояния всех

триггеров, входящих в состав

последовательного регистра.

ходы

синхронизации в последовательных

регистрах, как и в параллельных,

объединяются. Это обеспечивает

одновременность смены состояния всех

триггеров, входящих в состав

последовательного регистра.

Преобразование последовательного кода в параллельный производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход D0. Каждый бит сопровождается отдельным тактовым импульсом, который поступает на вход синхронизации C.

П

Рисунок

4. Обозначение последовательного

регистра на принципиальных схемах.

После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит запоминается в первом триггере.

После поступления четвертого тактового импульса в триггерах регистра будут записаны уровни бит, которые последовательно присутствовали на входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах.

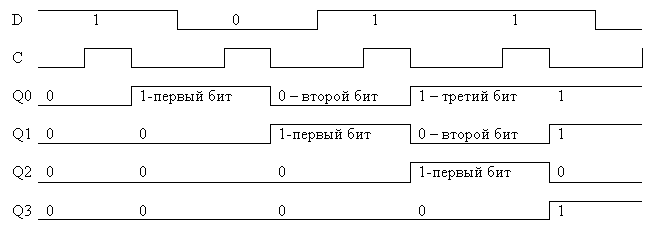

Пусть на вход регистра поступает сигнал, временная диаграмма которого изображена на рисунке 5, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 4.

Рисунок 5. Временная диаграмма работы сдвигового регистра.

№ такта |

1 |

2 |

3 |

1 |

Q0 |

1 |

0 |

1 |

1 |

Q1 |

X |

1 |

0 |

1 |

Q2 |

X |

X |

1 |

0 |

Q3 |

X |

X |

X |

1 |