- •Міністерство освіти і науки України

- •Урок № 3

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 6

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 11

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 13

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 14

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 15

- •Елементи ттлш серії к530, к531

- •Елементи ттлш серій к533, к535

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 16

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 17

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 18

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 19

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 22

- •Пріоритетний шифратор клавіатури

- •Література:

- •Урок № 23

- •Урок № 26

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 27

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 28

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 29

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 31

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 33

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 38

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 46

- •Питання для контролю вивченого матеріалу:

- •Література:

Питання для контролю вивченого матеріалу:

За якою структурою будуються прямокутні дешифратори?

Які дешифратори називаються матричними або прямокутними?

Назвіть переваги прямокутних дешифраторів.

Література:

М.П.Бабич, І.А.Жуков., «Комп’ютерна схемотехніка», 2004 р.

В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко, «Микросхемы и их применение», 2003 р.

Урок № 29

(згідно робочої навчальної програми)

Тема: Багатоступеневі дешифратори. Каскадування дешифраторів

Питання: 1. Принцип побудови багатоступеневих дешифраторів.

2. Каскадування дешифраторів.

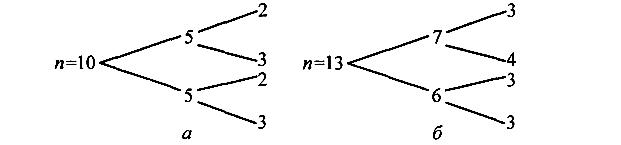

Принцип побудови багатоступеневих дешифраторів полягає у послідовному розбитті вхідного багаторозрядного коду до отримання у кожній групі двох-трьох розрядів. Як приклад на рис. 1 показано розбиття коду, який дешифрується для n= 10 й n = 13. Після цього багатоступенева схема дешифратора зображується у вигляді з'єднання ряду лінійних схем.

Рис. 1. Розбиття вхідного коду, який дешифрується на групи: а — при п = 10; б — при п = 13

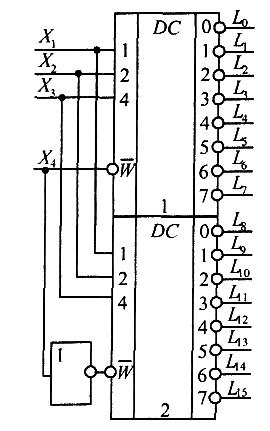

Під каскадуванням (нарощуванням) розуміють спосіб з'єднання дешифраторів у вигляді мікросхем середнього ступеня інтеграції для одержання більшої розрядності вхідного коду. З'єднання двох трирозрядних дешифраторів для декодування чотирирозрядного коду показано на рис. 2.

Рис 2. Каскадування дешифраторів

Вхідні змінні Х1, Х2 і Х3 подаються паралельно на входи обох дешифраторів: змінна X4 подається безпосередньо на вхід стробування першого дешифратора, через інвертор — на вхід стробування другого дешифратора.

Ця каскадна схема працює так. Якщо значення старшого розряду вхідного коду Х4 = 0, то в роботу включається перший дешифратор з інверсними вісьмома виходами L0, ..., L7, при цьому другий дешифратор блокований (вимкнений) і на його виходах L8, ..., L15 встановлюються високі рівні. При Х4 = 1 блокується перший дешифратор і включається в роботу друга мікросхема.

Таким чином, через наявність стробуючого входу два трирозрядних дешифратори утворюють схему дешифрації чотирирозрядного коду.

Питання для контролю вивченого матеріалу:

Поясніть принцип побудови багатоступеневих дешифраторів.

Що таке каскадування дешифраторів?

Література:

М.П.Бабич, І.А.Жуков., «Комп’ютерна схемотехніка», 2004 р.

В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко, «Микросхемы и их применение», 2003 р.

Урок № 31

(згідно робочої навчальної програми)

Тема: Каскадування мультиплексорів

Питання: 1. Приклад побудови схеми мультиплексора.

В інтегральному виконанні мультиплексори випускають на чотири, вісім або шістнадцять входів. Каскадування дозволяє реалізувати комутацію довільного числа вхідних ліній на базі серійних мікросхем мультиплексорів меншої розрядності.

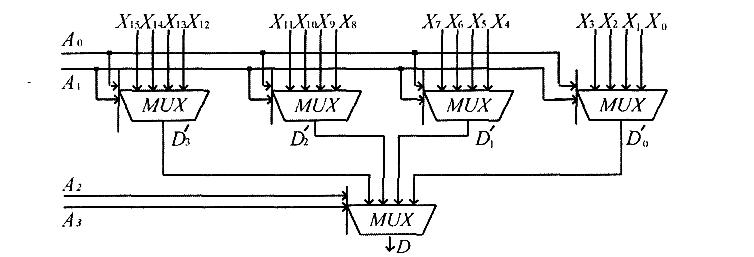

Приклад побудови схеми мультиплексора на 16 входів на основі типових чотиривходових мультиплексорів показаний на рис. 1.

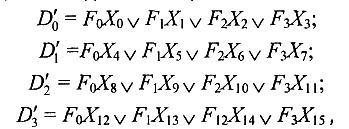

Молодші розряди адреси А1, А0 підключаються до адресних входів усіх мультиплексорів першого рівня, на виходах яких виробляються такі функції:

де

F0

– F3

—

виходи внутрішніх дешифраторів: F0=![]()

![]() ;

F1

=

А0;

F2=

А1

;

Fз=

А1

А0;

ХІ5

-Х0

—

вхідні змінні.

;

F1

=

А0;

F2=

А1

;

Fз=

А1

А0;

ХІ5

-Х0

—

вхідні змінні.

Старші розряди адреси A3, А2 подаються на адресні входи мультиплексора другого рівня, на виході якого формується остаточна функція

D = F0'D0' v F1' D1' v F2' D2' v F3' D3',

де

внутрішні виходи дешифратора визначаються

такими мінтермами: F'0=![]()

![]() ;

F'1

=

А2;

F'2=А3

;

F'3=А3А2.

;

F'1

=

А2;

F'2=А3

;

F'3=А3А2.

Нехай, наприклад, значення адреси А3А2А1А0= 10112 = 1110. При цьому функція молодшої частини адреси приймає значення F3 = А1 А0 = 1 і на виходах мультиплексорів першого рівня одночасно формуються сигнали D'0 = F3 Х1, D'1 = F3 Х7, D'2 = F3 Х11, D'3 = F3 Х15. Функція старшої частини адреси F'2 = А3 = 1 забезпечує передачу на вихід значення сигналу D'2, тобто

D = F'2 D'2= F'2F3Х11=А3 А1А0Х11.