- •Міністерство освіти і науки України

- •Урок № 3

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 6

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 11

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 13

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 14

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 15

- •Елементи ттлш серії к530, к531

- •Елементи ттлш серій к533, к535

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 16

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 17

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 18

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 19

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 22

- •Пріоритетний шифратор клавіатури

- •Література:

- •Урок № 23

- •Урок № 26

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 27

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 28

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 29

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 31

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 33

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 38

- •Питання для контролю вивченого матеріалу:

- •Література:

- •Урок № 46

- •Питання для контролю вивченого матеріалу:

- •Література:

Література:

М.П.Бабич, І.А.Жуков., «Комп’ютерна схемотехніка», 2004 р.

В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко, «Микросхемы и их применение», 2003 р.

Урок № 23

(згідно робочої навчальної програми)

Тема: Каскадування шифраторів

Питання: 1. Каскадування двох восьмивходових пріоритетних шифраторів

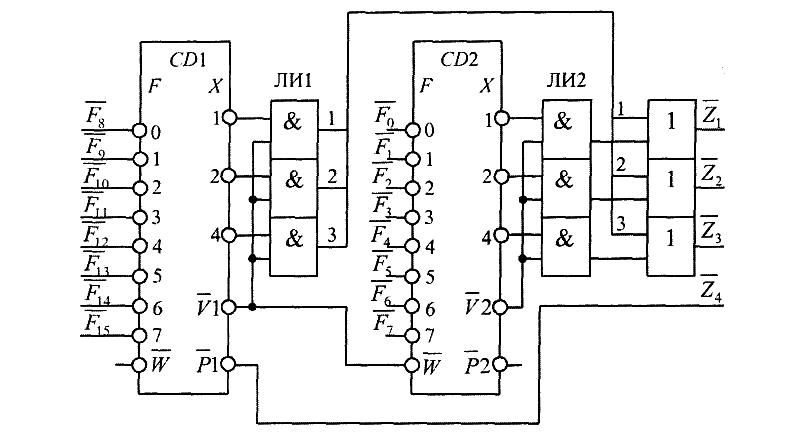

Каскадування

шифраторів використовується для

збільшення розрядності вхідного

слова. Схема каскадування двох

восьмивходових шифраторів К555ИВ1 для

пріоритетного

обслуговування 16-розрядного слова

![]() -

показана

на рис. 1.

-

показана

на рис. 1.

Розряди

-![]() старшого

байта вхідного слова поступають на

перший шифратор

СD1,

а

розряди

-

молодшого

байта подаються на другий шифратор

СD2.

старшого

байта вхідного слова поступають на

перший шифратор

СD1,

а

розряди

-

молодшого

байта подаються на другий шифратор

СD2.

Вхід

має

найвищий пріоритет, а

—

найнижчий. Інформаційні виходи обох

шифраторів об'єднуються за допомогою

логічних елементів ЧИ, утворюючи

трирозрядний інверсний код

![]()

![]()

![]() .

Значення

старшого розряду

.

Значення

старшого розряду

![]() забезпечується безпосередньо

сигналом

забезпечується безпосередньо

сигналом

![]() .

.

.

Рис. 1. Каскадування двох восьмивходових пріоритетних шифраторів

Інформація з виходів першого шифратора подається на входи елементів ЧИ за допомогою схем збігу ЛИ1 при 1= 1 (мікросхема CD1 сприймає вхідні дані, а CD2— блокована). Інформація з виходів другого шифратора подається на входи елементів ЧИ за допомогою схем збігу ЛИ2 при V2 = 1 (мікросхема CD2 сприймає вхідні дані, CD1 — блокується).

Схема

працює так: коли на вході є активний

сигнал із старшого байта вхідного

слова,

наприклад,

![]() =0

(

1

= 0

1=1),

то

працює шифратор CD1

і на виходах

елементів

ЧИ формується інверсний код

=

0001,

що відповідає прямому значенню

Z4Z3Z2Z1

=

1110 = 1410.

Якщо активний вхідний сигнал відноситься

до молодшого

байта слова, наприклад,

=0

(

1

= 0

1=1),

то

працює шифратор CD1

і на виходах

елементів

ЧИ формується інверсний код

=

0001,

що відповідає прямому значенню

Z4Z3Z2Z1

=

1110 = 1410.

Якщо активний вхідний сигнал відноситься

до молодшого

байта слова, наприклад,

![]() 6

=0,

то працює шифратор CD2

(

1

= 1

1=0

2

=

1)

і

на інверсних виходах формується код

=1001,

що відповідає прямому

числу Z4Z3Z2Z1

=

0110

= 610.

6

=0,

то працює шифратор CD2

(

1

= 1

1=0

2

=

1)

і

на інверсних виходах формується код

=1001,

що відповідає прямому

числу Z4Z3Z2Z1

=

0110

= 610.

Питання для контролю вивченого матеріалу:

Поясніть мету каскадування шифраторів.

Поясніть принцип дії схеми каскадування двох восьмивходових пріоритетних шифраторів

Література:

М.П.Бабич, І.А.Жуков., «Комп’ютерна схемотехніка», 2004 р.

В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко, «Микросхемы и их применение», 2003 р.

Урок № 26

(згідно робочої навчальної програми)

Тема: Лінійні дешифратори на два входи і чотири виходи

Питання: 1. Схема лінійного дешифратора на елементах І.

2. Схема лінійного дешифратора на елементах ЧИ

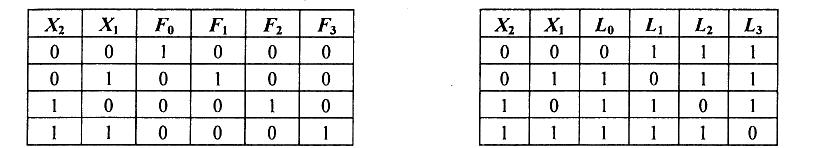

У лінійному дешифраторі "з n в m" кожна вихідна функція Fi реалізується повністю окремим n-вхідним логічним елементом при використанні парафазного вхідного коду. Логіка роботи повних дешифраторів на два входи Х1, Х2 і чотири прямих виходи F0, F1, F2, F3 і чотири інверсних виходи L0, L1, L2, L3 наведена в табл. 1 й 2 відповідно.

Таблиця 1 Таблиця 2

За даними табл. 1 отримують систему логічних функцій в ДДНФ:

F0 = ; F1= Х1; F2 = Х2 ; F3 = Х1Х2. (1)

Для лінійного дешифратора зі стробуючим входом W система рівнянь (1) набуває вигляду:

F0 = W; F1= Х1W; F2 = Х2 W; F0 = Х2Х1W. (2)

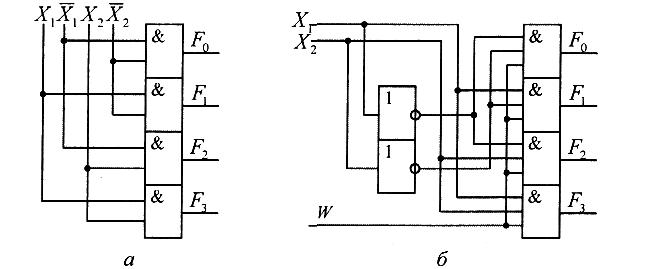

Схеми лінійних дешифраторів на основі рівнянь (1) й (2) показані на рис. 1.

Рис. 1. Схеми лінійних дешифраторів на елементах І:

а — з парафазними входами; б — з однофазними входами і стробуванням

У схемі, зображеній на рис. 1, б використовується однофазний вхідний код, оскільки інверсії змінних утворюються елементами НЕ. Якщо сигнал на стробуючому вході W = 0, то робота дешифратора блокується — на всіх виходах установлюються логічні нулі незалежно від значень вхідних змінних. При W = 1 дешифратор функціонує згідно з табл. 1.

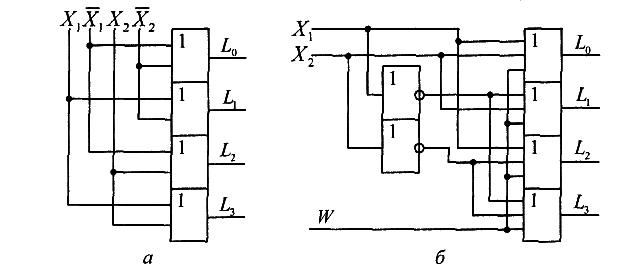

За даними табл. 2 записується система логічних функцій в ДКНФ:

L0 = Х2 v Х1, L1 =Х2 v , L2= v Х1, L3 = = v (3)

Схема лінійного дешифратора з парафазним вхідним кодом та інверсними виходами, побудована згідно з рівнянням (3) на елементах ЧИ, показана на рис. 2, а.

Для лінійного дешифратора із стробуючим W входом система керування (3) набуває вигляду:

L0 = Х2 v Х v W, L1 =Х2 v v W,

L2= v Х1 v W, L3 = = v v W. (4)

Схема лінійного дешифратора на основі рівнянь (4) показана на рис. 2, б.

Рис 2. Схема лінійних дешифраторів на елементах ЧИ:

а — з парафазними входами; б — з однофазними входами і стробуванням

Тут використовується однофазний вхідний код, оскільки інверсії змінних утворюються елементами НЕ. Якщо сигнал на стробуючому вході W = 1, то робота дешифратора блокується — на всіх виходах встановлюються лог. 1 незалежно від значень вхідних змінних. При W = 0 дешифратор функціонує згідно з табл. 2.