- •3.2.7. Датчики температуры 64

- •3.2.7.1. Общие сведения 64

- •3.2.8. Сети датчиков, интеллектуальные датчики 84

- •Глава 1. Микропроцессорная техника

- •1.1. Общие понятия

- •1.1.1. Уровни интеграции микросхем, выполненных по различным технологиям

- •Типы логики [вики]

- •1.1.2. Определения и особенности микропроцессора, микропроцессорной системы и микроконтроллера

- •1.2. Структура типичной микроэвм

- •1.2.1. Система шин микроЭвм

- •1.2.2. Микропроцессор

- •1.2.3. Память

- •1.2.4. Порты

- •1.3. Формирование сигналов на системной магистрали

- •1.3.1. Основные управляющие сигналы

- •1.3.2. Чтение данных из памяти

- •1.3.3. Запись данных в память

- •1.3.4. Чтение данных из порта ввода

- •1.3.5. Запись данных в порт вывода

- •1.4.1. Структура микропроцессора кр580вм80

- •1.4.2. Выполнение команд в микропроцессоре

- •1.5. Система команд микропроцессора кр580вм80

- •1.5.1. Команды пересылки

- •1.5.2. Арифметические команды

- •1.5.3. Логические команды

- •1.5.4. Формирование и работа стека

- •1.5.5. Команды перехода

- •1.5.6. Команды вызова подпрограмм и возврата из них

- •1.5.7. Команды сдвига

- •1.5.8. Команды ввода/вывода

- •1.6. Микросхемы шинных формирователей

- •1.6.1. Элементы с тремя состояниями

- •1.6.2. Шинные формирователи

- •1.6.3. Буферный регистр

- •1.7. Микросхемы дешифраторов и демультиплексоров

- •1.7.1. Назначение дешифраторов

- •1.7.2. Микросхемы дешифраторов

- •1.7.3. Структура дешифратора

- •1.7.4. Микросхемы демультиплексоров

- •1.8. Микросхемы памяти

- •1.8.1. Классификация запоминающих устройств

- •1.8.2. Параметры микросхем памяти

- •1.8.3. Микросхемы постоянных запоминающих устройств

- •1.8.3.1. Масочные микросхемы пзу

- •1.8.3.2. Программируемые микросхемы пзу

- •1.8.3.3. Многократно программируемые микросхемы пзу

- •1.8.4. Микросхемы оперативных запоминающих устройств

- •1.8.4.1. Микросхемы статических озу

- •1.8.4.2. Микросхемы динамических озу

- •1.9. Подсистемы памяти

- •1.9.1. Увеличение разрядности

- •1.9.2. Увеличение количества ячеек

- •1.10. Параллельный интерфейс

- •1.10.1. Назначение и структура микросхемы кр580вв55

- •1.10.2. Условное обозначение и назначение выводов микросхемы кр580вв55

- •1.11. Подсистемы ввода/вывода

- •1.11.1. Ввод данных в микроЭвм

- •1.11.2. Вывод данных из микроЭвм

- •1.12. Последовательный интерфейс

- •1.12.1. Асинхронный обмен

- •1.12.2. Синхронный обмен

- •1.12.3. Программируемый связной адаптер

- •1.12.3.1. Условное обозначение и назначение выводов адаптера

- •1.12.3.2. Программирование и работа с адаптером

- •1.13. Обмен данными по прерываниям

- •1.13.1. Понятие прерывания

- •1.13.1.1. Многоуровневые прерывания

- •1.13.1.2. Приоритетные прерывания

- •1.13.2. Идентификация источника прерывания

- •1.13.2.1. Программный поллинг

- •1.12.2.2. Аппаратный поллинг

- •1.13.3. Программируемый контроллер прерываний

- •1.13.3.1. Общая характеристика контроллера

- •1.13.3.2. Выводы контроллера

- •1.13.3.3. Принцип работы контроллера прерываний

- •1.13.3.4. Каскадирование контроллеров

- •1.13.3.5. Порядок работы с контроллером

- •1.14. Прямой доступ к памяти

- •1.15. Программируемый таймер

- •1.15.1. Назначение таймеров

- •1.15.2. Микросхема пит кр580ви53/54

- •1.15.3. Назначение выводов пит

- •1.15.4. Программирование и работа пит

- •1.15.5. Режимы работы пит

- •1.16. История развития и современное состояние средств микропроцессорной техники

- •1.16.1. История развития микропроцессорной техники

- •1.16.2. Современное состояние средств микропроцессорной техники

- •Глава 2. Микропроцессорные системы

- •2.1. Основы микропроцессора

- •2.2. Основные исторические сведения о развитии микропроцессоров

- •2.3. Микропроцессор - основа эвм

- •2.4. Микропроцессорные системы

- •2.4.1. Классификация микропроцессоров. Понятие о разрядности и системе команд

- •2.4.2. Основные характеристики и критерии производительности микропроцессора

- •2.4.3. Архитектура простейших микропроцессорных систем

- •2.4.4. Архитектуры многопроцессорных вычислительных систем. Принципы построения mpp- и smp-систем

- •2.5. Структура однокристального мп, состав и назначение элементов

- •2.6. Многоядерные микропроцессорные системы

- •2.7. Управляющий автомат простейшей микропроцессорной системы

- •2.7.1. Алгоритм управляющего автомата

- •2.7.2. Цикл команды в мпс

- •2.7.3. Тактирование мп и синхронизация мпс

- •2.7.4. Слово состояния мп как средство управления системой

- •2.7.5. Управляющее устройство мп. Мпс под управлением первичного автомата

- •2.7.6. Работа первичного управляющего автомата в режиме прерывания

- •2.7.7. Работа первичного управляющего автомата в режиме захвата шин

- •2.8. Методы и способы организации памяти

- •2.9. Принципы действия ячеек памяти

- •2.9.1. Динамическая память

- •2.9.2. Статическая память

- •2.9.3. Энергонезависимая память

- •2.10. Кэширование

- •2.11. Карта памяти. Критерии и способы распределения адресного пространства

- •Глава 3. Микропроцессорные системы и управление

- •3.2. Микропроцессорные системы с датчиками

- •3.2.1. Общие сведения

- •3.2.2. Резистивные датчики

- •3.2.3. Тензометрические датчики

- •3.2.4. Применение тензодатчиков для измерения силы

- •3. 2.5. Измерение потоков жидкостей и газов

- •3.2.6. Измерение деформации

- •3.2.7. Датчики температуры

- •3.2.7.1. Общие сведения

- •3.2.7.2. Термопары и компенсация холодного спая

- •3.2.7.3. Резистивные датчики температуры

- •3.2.7.4. Термисторы

- •2.7.5. Полупроводниковые датчики температуры

- •3.2.7.6. Датчики температуры с цифровым выходом

- •3.2.7.7. Термореле и регуляторы с установкой температуры

- •3.2.7.8. Аналого-цифровые преобразователи с датчиком температуры на одном кристалле

- •3.2.8. Сети датчиков, интеллектуальные датчики

- •3.2.8.1. Токовая петля

- •3.2.8.2. Объединение датчиков в сеть

- •3.3.Развитие систем управления

- •3.3.1. Контур управления

- •3.3.2. Компьютерная регистрация данных

- •3.3.3.Машинное диспетчерское управление (мду)

- •3.3.4.Прямое цифровое управление (пцу)

- •Глава 4. Распределенные системы управления

- •4.1.Элементы системы

- •4.1.1. Принципы распределенного управления

- •4.1.2. Конечные элементы системы управления

- •4.1.3. Другие элементы

- •4.1.4. Распределенное управление

- •4.2.Передача данных

- •4.2.1.Информационная магистраль

- •4.2.2. Формат данных

- •4.2.3. Командные слова

- •4.2.4.Информационные слова

- •4.2.5.Модули информационной магистрали

- •4.2.6.Предпочтительный доступ

- •4.2.7.Последовательный опрос

- •4.2.8.Контроллер связи

- •4.2.9.Контроль ошибок

- •4.3.Базовый контроллер

- •4.3.1.Настраиваемые параметры

- •4.3.2.Аппаратная конфигурация контроллера

- •4.3.3.Центральный процессор (цп)

- •4.3.4.Магистральный интерфейс

- •4.3.5.Блок удержания выходных сигналов

- •4.3.6.Память

- •4.3.7.Шина данных

- •4.3.8.Назначение адресов

- •4.3.9.Обобщение по работе контроллера

- •4.4. Настройка базового контроллера рсу

- •4.4.1. Настройка контроллера

- •4.4.2.Режимы управления

- •4.4.3. Конфигурационные слова

- •4.4.4.Метод конфигурирования

- •4.4.5.Диагностика

- •4.4.6.Алгоритмы

- •4.5. Бесперебойное автоматическое управление (бау)

- •4.5.1.Необходимость резервирования

- •4.5.2.Работа системы

- •4.5.3.Реальная система

- •Дополнения к системе бау

- •Порядок работы бау

- •4.6. Блоки обработки

- •Устройство блока обработки

- •Конструкция блока обработки

- •Функции обработки данных

- •Принцип работы

- •Пульт оператора

- •Оборудование, входящее в состав пульта оператора

- •Блок плат пульта оператора

- •Эргономика

- •Дисплеи на пульте оператора

- •4.7.5. Усовершенствованные распределенные системы управления

- •4.7.5.1. Ограничение систем с информационной магистралью

- •4.7.5.2. Усовершенствованная рсу

- •4.7.5.3. Локальная вычислительная сеть (лвс)

- •Шлюзовый модуль (шм)

- •Структура системы

- •Система высокого уровня (лвс)

- •Обмен данными

- •Модули лвс

- •Отчеты в среде рсу

- •Обработка данных в усовершенствованнной рсу.

- •Настройка рсу

- •4.9.1.Конфигурационные данные

- •Конфигурационные данные системы (кдс)

- •Конфигурационные данные процесса

- •Зональная база данных

- •Организация базы данных элементов техпроцесса

- •Принципы усовершествованного управления

- •Уровни управления

- •Управление первого уровния от устройства им

- •Управление второго уровня от миникомпьютера

- •Управление 3-го уровня от центральной эвм

- •Вопросы техобслуживания

- •Техобслуживание конечных элементов

- •Проверка калибровки контура управления

- •Техобслуживание блока информационной магистрали

- •Источники питания

- •Системы бесперебойного питания (ups)

- •Глава 5. Примеры распределенных систем управления

4.5. Бесперебойное автоматическое управление (бау)

В современной распределенной системе управления, управляющей технологической установкой с одного пульта оператора, базовые и усовершенствованные контроллеры обрабатывают большой объем данных, связанных с процессом. При отказе одного из этих устройств и отсутствии средств резервирования вся установка может остановиться. Чтобы избежать такой ситуации, используется система Бесперебойного Автоматического Управления (БАУ).

4.5.1.Необходимость резервирования

Два основных блока на ИМ – это базовый и усовершенствованный контроллеры. Базовый контроллер может одновременно управлять 8 контурами, а усовершенствованная версия может работать с 16 контурами, программами последовательности, логическими блоками, а также аналоговыми и цифровыми данными. В случае отказа этих устройств по любой причине, для поддержания непрерывности процесса обязательно наличие резервного устройства, который примет на себя управление без прерывания техпроцесса.

С этой целью предусмотрено БЕСПЕРЕБОЙНОЕ АВТОМАТИЧЕСКОЕ УПРАВЛЕНИЕ (БАУ) процессом при отказе контроллера на ИМ, запасной или РЕЗЕРВНЫЙ КОНТРОЛЛЕР (RC) вместе с БЛОКОМ УПРАВЛЕНИЯ РЕЗЕРВНЫМ КОНТРОЛЛЕРОМ (RCD), для принятия управления. Один резервный контроллер может с помощью своего блока управления следить за 8 контроллерами на магистрали. При отказе одного из них, блок управления резервным контроллером даст указание резервному контроллеру заменить неисправное устройство и выполнять его функции.

Операциям, выполняемым в каждом контроллере, подключенному к RC и RCD, необходимо назначить приоритет. Приоритеты можно настроить в RCD таким образом, чтобы при отказе одного блока контроллера резервный контроллер принимал на себя его функции. При отказе следующего контроллера, перед окончанием ремонта первого неисправного блока, RCD может определить, какой неисправный блок можно заменить резервным контроллером согласно назначенному приоритету. Таким образом обеспечивается постоянная работа даже при отказе более одного устройства.

Необходимо отметить, что при существующей надежности электронных узлов, печатных плат, интегральных схем и т.д., вероятность отказа второго устройства до окончания ремонта первого чрезвычайно мала.

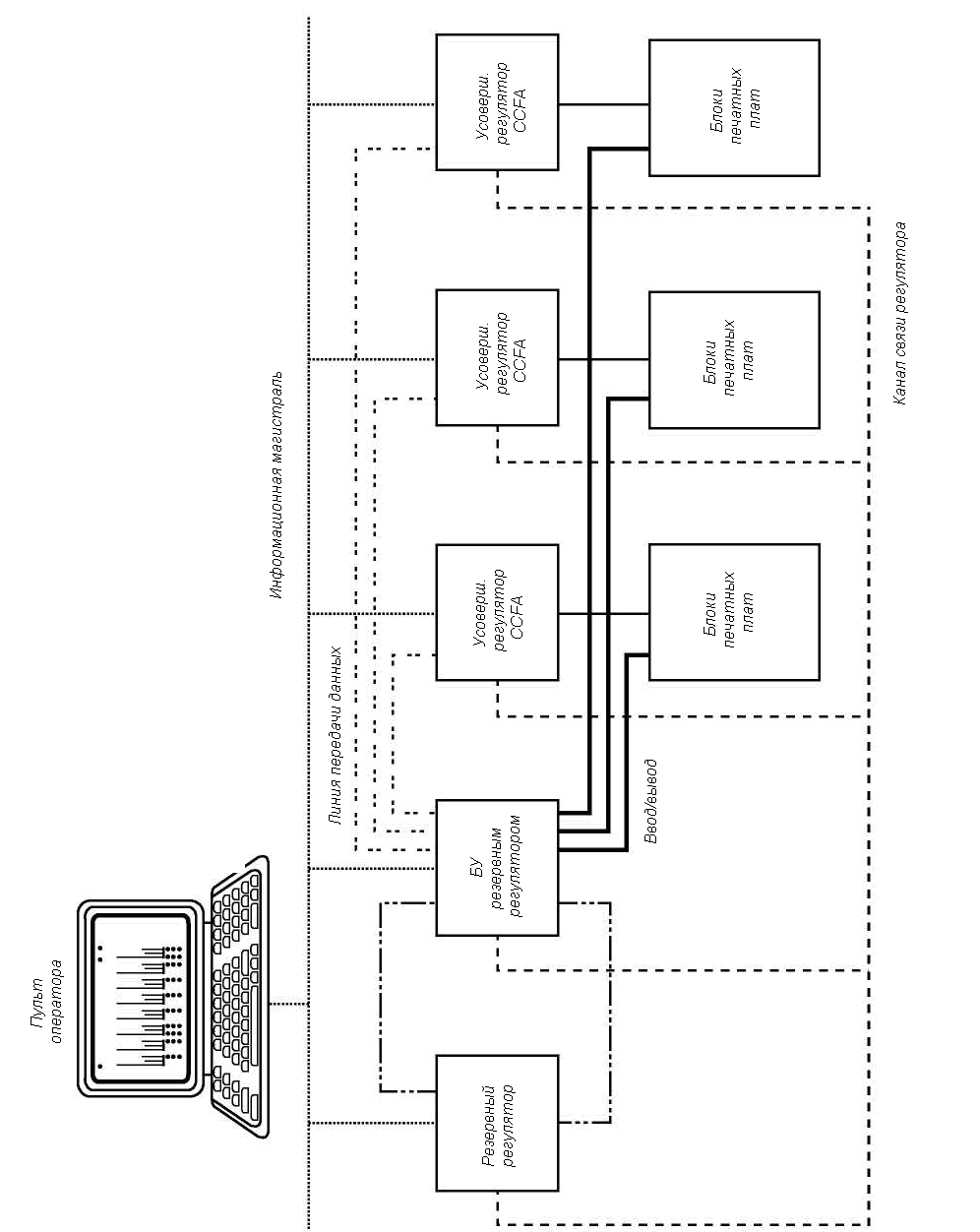

Р ИС.

7.1 Бесперебойное

автоматическое управление (БАУ)

ИС.

7.1 Бесперебойное

автоматическое управление (БАУ)

На РИС. 7.1 в схематичной форме показан общий план системы БАУ с тремя усовершенствованными контроллерами одним резервным контроллером и блоком управления (БУ) резервного контроллера. Этот же принцип аналогичен и для базовых контроллеров. Однако у базовых контроллеров резервируются только их 8 регулирующих контуров. У усовершенствованных контроллеров, кроме этого, резервируются и связанные с ними блоки плат PCFA.

Резервный контроллер и его БУ подключаются к ИМ через кабели 'A' и 'B', так же как основные контроллеры.

Если усовершенствованные контроллеры соединены между собой каналом связи для взаимного обмена информации или программами, такие же кабели необходимо подключить и к резервному контроллеру через специальную плату. При необходимости, приняв на себя функции неисправного блока, резервный контроллер будет иметь доступ через канал связи к другим контроллерам. Канал связи подключается и к RCD.

В общий блок плат (CCFA) каждого резервируемого контроллера устанавливается специальная плата БАУ, которая имеет проводное соединение с БУ резервного контроллера. Плата БАУ позволяет передавать данные из ОЗУ с батарейной памятью контроллера на ОЗУ RCD и на RC.

Блоки PCFA контроллеров имеют линии шины ввода-вывода, подключенные к RCD так, чтобы эти блоки были доступны для RCD и RC в случае необходимости резервирования.