- •3.2.7. Датчики температуры 64

- •3.2.7.1. Общие сведения 64

- •3.2.8. Сети датчиков, интеллектуальные датчики 84

- •Глава 1. Микропроцессорная техника

- •1.1. Общие понятия

- •1.1.1. Уровни интеграции микросхем, выполненных по различным технологиям

- •Типы логики [вики]

- •1.1.2. Определения и особенности микропроцессора, микропроцессорной системы и микроконтроллера

- •1.2. Структура типичной микроэвм

- •1.2.1. Система шин микроЭвм

- •1.2.2. Микропроцессор

- •1.2.3. Память

- •1.2.4. Порты

- •1.3. Формирование сигналов на системной магистрали

- •1.3.1. Основные управляющие сигналы

- •1.3.2. Чтение данных из памяти

- •1.3.3. Запись данных в память

- •1.3.4. Чтение данных из порта ввода

- •1.3.5. Запись данных в порт вывода

- •1.4.1. Структура микропроцессора кр580вм80

- •1.4.2. Выполнение команд в микропроцессоре

- •1.5. Система команд микропроцессора кр580вм80

- •1.5.1. Команды пересылки

- •1.5.2. Арифметические команды

- •1.5.3. Логические команды

- •1.5.4. Формирование и работа стека

- •1.5.5. Команды перехода

- •1.5.6. Команды вызова подпрограмм и возврата из них

- •1.5.7. Команды сдвига

- •1.5.8. Команды ввода/вывода

- •1.6. Микросхемы шинных формирователей

- •1.6.1. Элементы с тремя состояниями

- •1.6.2. Шинные формирователи

- •1.6.3. Буферный регистр

- •1.7. Микросхемы дешифраторов и демультиплексоров

- •1.7.1. Назначение дешифраторов

- •1.7.2. Микросхемы дешифраторов

- •1.7.3. Структура дешифратора

- •1.7.4. Микросхемы демультиплексоров

- •1.8. Микросхемы памяти

- •1.8.1. Классификация запоминающих устройств

- •1.8.2. Параметры микросхем памяти

- •1.8.3. Микросхемы постоянных запоминающих устройств

- •1.8.3.1. Масочные микросхемы пзу

- •1.8.3.2. Программируемые микросхемы пзу

- •1.8.3.3. Многократно программируемые микросхемы пзу

- •1.8.4. Микросхемы оперативных запоминающих устройств

- •1.8.4.1. Микросхемы статических озу

- •1.8.4.2. Микросхемы динамических озу

- •1.9. Подсистемы памяти

- •1.9.1. Увеличение разрядности

- •1.9.2. Увеличение количества ячеек

- •1.10. Параллельный интерфейс

- •1.10.1. Назначение и структура микросхемы кр580вв55

- •1.10.2. Условное обозначение и назначение выводов микросхемы кр580вв55

- •1.11. Подсистемы ввода/вывода

- •1.11.1. Ввод данных в микроЭвм

- •1.11.2. Вывод данных из микроЭвм

- •1.12. Последовательный интерфейс

- •1.12.1. Асинхронный обмен

- •1.12.2. Синхронный обмен

- •1.12.3. Программируемый связной адаптер

- •1.12.3.1. Условное обозначение и назначение выводов адаптера

- •1.12.3.2. Программирование и работа с адаптером

- •1.13. Обмен данными по прерываниям

- •1.13.1. Понятие прерывания

- •1.13.1.1. Многоуровневые прерывания

- •1.13.1.2. Приоритетные прерывания

- •1.13.2. Идентификация источника прерывания

- •1.13.2.1. Программный поллинг

- •1.12.2.2. Аппаратный поллинг

- •1.13.3. Программируемый контроллер прерываний

- •1.13.3.1. Общая характеристика контроллера

- •1.13.3.2. Выводы контроллера

- •1.13.3.3. Принцип работы контроллера прерываний

- •1.13.3.4. Каскадирование контроллеров

- •1.13.3.5. Порядок работы с контроллером

- •1.14. Прямой доступ к памяти

- •1.15. Программируемый таймер

- •1.15.1. Назначение таймеров

- •1.15.2. Микросхема пит кр580ви53/54

- •1.15.3. Назначение выводов пит

- •1.15.4. Программирование и работа пит

- •1.15.5. Режимы работы пит

- •1.16. История развития и современное состояние средств микропроцессорной техники

- •1.16.1. История развития микропроцессорной техники

- •1.16.2. Современное состояние средств микропроцессорной техники

- •Глава 2. Микропроцессорные системы

- •2.1. Основы микропроцессора

- •2.2. Основные исторические сведения о развитии микропроцессоров

- •2.3. Микропроцессор - основа эвм

- •2.4. Микропроцессорные системы

- •2.4.1. Классификация микропроцессоров. Понятие о разрядности и системе команд

- •2.4.2. Основные характеристики и критерии производительности микропроцессора

- •2.4.3. Архитектура простейших микропроцессорных систем

- •2.4.4. Архитектуры многопроцессорных вычислительных систем. Принципы построения mpp- и smp-систем

- •2.5. Структура однокристального мп, состав и назначение элементов

- •2.6. Многоядерные микропроцессорные системы

- •2.7. Управляющий автомат простейшей микропроцессорной системы

- •2.7.1. Алгоритм управляющего автомата

- •2.7.2. Цикл команды в мпс

- •2.7.3. Тактирование мп и синхронизация мпс

- •2.7.4. Слово состояния мп как средство управления системой

- •2.7.5. Управляющее устройство мп. Мпс под управлением первичного автомата

- •2.7.6. Работа первичного управляющего автомата в режиме прерывания

- •2.7.7. Работа первичного управляющего автомата в режиме захвата шин

- •2.8. Методы и способы организации памяти

- •2.9. Принципы действия ячеек памяти

- •2.9.1. Динамическая память

- •2.9.2. Статическая память

- •2.9.3. Энергонезависимая память

- •2.10. Кэширование

- •2.11. Карта памяти. Критерии и способы распределения адресного пространства

- •Глава 3. Микропроцессорные системы и управление

- •3.2. Микропроцессорные системы с датчиками

- •3.2.1. Общие сведения

- •3.2.2. Резистивные датчики

- •3.2.3. Тензометрические датчики

- •3.2.4. Применение тензодатчиков для измерения силы

- •3. 2.5. Измерение потоков жидкостей и газов

- •3.2.6. Измерение деформации

- •3.2.7. Датчики температуры

- •3.2.7.1. Общие сведения

- •3.2.7.2. Термопары и компенсация холодного спая

- •3.2.7.3. Резистивные датчики температуры

- •3.2.7.4. Термисторы

- •2.7.5. Полупроводниковые датчики температуры

- •3.2.7.6. Датчики температуры с цифровым выходом

- •3.2.7.7. Термореле и регуляторы с установкой температуры

- •3.2.7.8. Аналого-цифровые преобразователи с датчиком температуры на одном кристалле

- •3.2.8. Сети датчиков, интеллектуальные датчики

- •3.2.8.1. Токовая петля

- •3.2.8.2. Объединение датчиков в сеть

- •3.3.Развитие систем управления

- •3.3.1. Контур управления

- •3.3.2. Компьютерная регистрация данных

- •3.3.3.Машинное диспетчерское управление (мду)

- •3.3.4.Прямое цифровое управление (пцу)

- •Глава 4. Распределенные системы управления

- •4.1.Элементы системы

- •4.1.1. Принципы распределенного управления

- •4.1.2. Конечные элементы системы управления

- •4.1.3. Другие элементы

- •4.1.4. Распределенное управление

- •4.2.Передача данных

- •4.2.1.Информационная магистраль

- •4.2.2. Формат данных

- •4.2.3. Командные слова

- •4.2.4.Информационные слова

- •4.2.5.Модули информационной магистрали

- •4.2.6.Предпочтительный доступ

- •4.2.7.Последовательный опрос

- •4.2.8.Контроллер связи

- •4.2.9.Контроль ошибок

- •4.3.Базовый контроллер

- •4.3.1.Настраиваемые параметры

- •4.3.2.Аппаратная конфигурация контроллера

- •4.3.3.Центральный процессор (цп)

- •4.3.4.Магистральный интерфейс

- •4.3.5.Блок удержания выходных сигналов

- •4.3.6.Память

- •4.3.7.Шина данных

- •4.3.8.Назначение адресов

- •4.3.9.Обобщение по работе контроллера

- •4.4. Настройка базового контроллера рсу

- •4.4.1. Настройка контроллера

- •4.4.2.Режимы управления

- •4.4.3. Конфигурационные слова

- •4.4.4.Метод конфигурирования

- •4.4.5.Диагностика

- •4.4.6.Алгоритмы

- •4.5. Бесперебойное автоматическое управление (бау)

- •4.5.1.Необходимость резервирования

- •4.5.2.Работа системы

- •4.5.3.Реальная система

- •Дополнения к системе бау

- •Порядок работы бау

- •4.6. Блоки обработки

- •Устройство блока обработки

- •Конструкция блока обработки

- •Функции обработки данных

- •Принцип работы

- •Пульт оператора

- •Оборудование, входящее в состав пульта оператора

- •Блок плат пульта оператора

- •Эргономика

- •Дисплеи на пульте оператора

- •4.7.5. Усовершенствованные распределенные системы управления

- •4.7.5.1. Ограничение систем с информационной магистралью

- •4.7.5.2. Усовершенствованная рсу

- •4.7.5.3. Локальная вычислительная сеть (лвс)

- •Шлюзовый модуль (шм)

- •Структура системы

- •Система высокого уровня (лвс)

- •Обмен данными

- •Модули лвс

- •Отчеты в среде рсу

- •Обработка данных в усовершенствованнной рсу.

- •Настройка рсу

- •4.9.1.Конфигурационные данные

- •Конфигурационные данные системы (кдс)

- •Конфигурационные данные процесса

- •Зональная база данных

- •Организация базы данных элементов техпроцесса

- •Принципы усовершествованного управления

- •Уровни управления

- •Управление первого уровния от устройства им

- •Управление второго уровня от миникомпьютера

- •Управление 3-го уровня от центральной эвм

- •Вопросы техобслуживания

- •Техобслуживание конечных элементов

- •Проверка калибровки контура управления

- •Техобслуживание блока информационной магистрали

- •Источники питания

- •Системы бесперебойного питания (ups)

- •Глава 5. Примеры распределенных систем управления

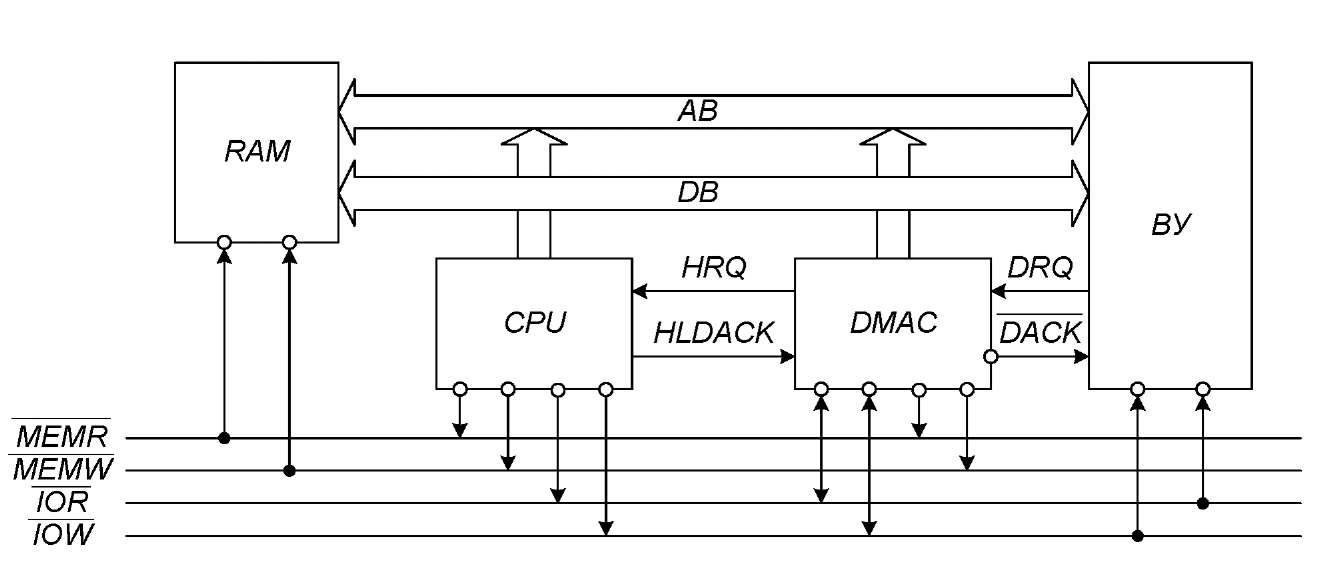

1.14. Прямой доступ к памяти

Обслуживание внешних устройств по прерываниям может замедлить работу микроЭВМ, если главное назначение прерываний заключается в передаче большого количества данных от внешнего устройства в ОЗУ или наоборот. Причина заключается в том, что для передачи одного слова данных требуется передача кода вызова подпрограммы обслуживания прерываний, и двухбайтного адреса источника прерываний, а это занимает машинное время. Это особенно существенно при передаче большого массива данных от жесткого диска. Для решения этой проблемы используется прямой доступ к памяти, суть которого в том, что в обмене данными не принимает участия микропроцессор (рис. 14.1).

Его управляющие функции берет на себя контроллер прямого доступа к памяти. Во избежание конфликтов CPU во время прямого доступа к памяти отключается от системных шин за счет наличия схем с тремя состояниями.

Схема работы канала прямого доступа к памяти следующая:

Внешнее устройство генерирует запрос прямого доступа к памяти (Direct Request).

DAMC передает его центральному процессору (HoldRequest).

CPU приостанавливает выполняемую программу и разрешает прямой доступ сигналом HLDACK.

DAMC генерирует адрес ячейки памяти для обмена и подтверждает сеанс прямого доступа для внешнего устройства выдачей сигнала DACK.

DMAC генерирует сигналы MEMR или MEMW, показывающие направление обмена данными.

Рис. 14.1

Выделяют различные разновидности прямого доступа к памяти:

Блокировка центрального процессора на время передачи всего пакета данных. В этом случае прекращается работа выполняемой программы.

Захват цикла. Используется в тех циклах работы микропроцессора, когда не происходит его обращение к памяти.

Можно сказать, что контроллер прямого доступа к памяти представляет собой специализированный процессор для быстрой передачи данных между внешним устройством и памятью, который на время обмена данными берет на себя обязанности центрального процессора.

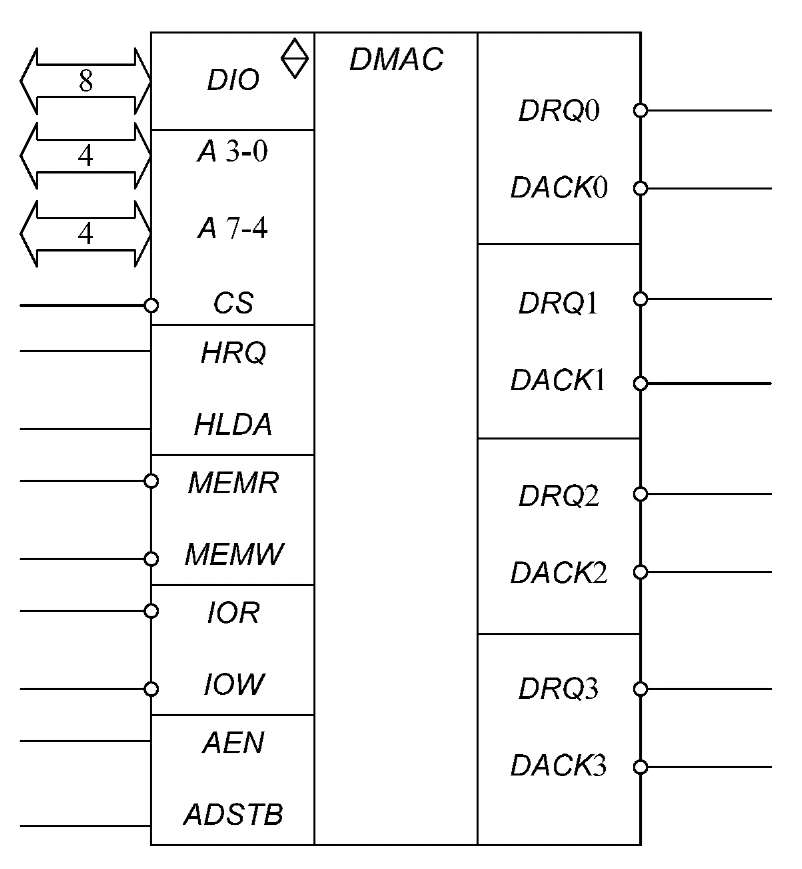

Микросхема контроллера прямого доступа к памяти

Контроллер прямого доступа к памяти управляет работой четырех независимых каналов прямого доступа к памяти с учетом приоритетов внешних устройств. Подобно контроллеру прерываний эти приоритеты могут быть циклически изменяемы.

Назначение выводов

На рис. 14.2 представлено условное изображение микросхемы контроллера прямого доступа к памяти.

Рис. 14.2

На рис. 14.2 использованы следующие условные обозначения:

D(7-0) - вход/выход данных, присоединяется к шине данных для обмена с микропроцессором.

IOR - чтение ввода/вывода - двунаправленный трехстабильный вход/выход, входной сигнал высокого уровня разрешает чтение информации из внутреннего регистра контроллера в микропроцессор. Выходной сигнал высокого уровня разрешает чтение из внешнего устройства.

IOW - запись ввода/вывода - двунаправленный трехстабильный вход/выход, входной сигнал низкого уровня разрешает программирование контроллера, входной сигнал высокого уровня разрешает запись во внешнее устройство.

А (3-0) - двунаправленные трехстабильные адресные выводы младшего полубайта адреса памяти.

А(7-4) - двунаправленные трехстабильные адресные выходы старшего полубайта адреса памяти.

HRQ - запрос захвата - выходной сигнал высоко уровня указывает на запрос о доступе контроллера к системным шинам.

HLDA - подтверждение захвата - входной сигнал высокого уровня указывает на возможность доступа к системным шинам.

MEMW - запись в память - трехстабильный выход, выходной сигнал низкого уровня разрешает запись в ячейку, адресуемую контроллером.

MEMR - чтение из памяти - трехстабильный выход, выходной сигнал низкого уровня разрешает чтение из ячейки, адресуемой из контроллера.

AEN - разрешение адреса - сигнал высокого уровня используется для блокировки некоторых шин адреса и данных.

ADSTB - строб адреса - сигнал высокого уровня указывает на нахождение на шине D(7-0) старшего байта адреса памяти.

CS - выбор микросхемы.

DRQ3-DRQ0 - запросы прямого доступа к памяти внешних устройств, сигнал высокого уровня указывает на запрос.

DACK3-DACK0 - подтверждение запросов прямого доступа к памяти внешних устройств, сигнал высокого уровня указывает на разрешение обмена.

Порядок работы с контроллером

Перед работой КПДП его необходимо запрограммировать (инициализировать). Инициализация контроллера прямого доступа к памяти осуществляется загрузкой исходных данных (начальные адреса областей ОЗУ, размер блоков данных и коды режимов) в адресуемые регистры и слова управления в регистр режима КПДП. Содержимое любого регистра и счетчика, кроме регистра режима, управляющего передачей данных из МП в ВУ и обратно, можно считать. После чего можно осуществить передачу данных по выбранному каналу в нужном направлении.

Инициализация контроллера

Для инициализации контроллера необходимо записать соответствующую информацию:

в 16-разрядный регистр адреса канала;

16-разрядный счетчик циклов канала;

8-разрядный регистр режима, общий для всех каналов.

Причем если программируется несколько каналов, то сначала записывается регистр адреса и счетчик циклов для каждого канала, а затем регистр режима, общий для всех каналов.

Запись осуществляется строго в указанной последовательности в соответствии с таблицей истинности (табл. 14.1), в которой приведены коды адресных выводов для адресации внутренних регистров КПДП.

Таблица 14.1

Регистр |

Адресные сигналы |

||||

CS |

A3 |

A2 |

A1 |

A0 |

|

Регистр адреса канала СН0 |

0 |

0 |

0 |

0 |

0 |

Счетчик циклов канала СН0 |

0 |

0 |

0 |

0 |

1 |

Регистр адреса канала СН1 |

0 |

0 |

0 |

1 |

0 |

Счетчик циклов канала СН1 |

0 |

0 |

0 |

1 |

1 |

Регистр адреса канала СН2 |

0 |

0 |

1 |

0 |

0 |

Счетчик циклов канала СН2 |

0 |

0 |

1 |

0 |

1 |

Регистр адреса канала СН3 |

0 |

0 |

1 |

1 |

0 |

Счетчик циклов канала СН3 |

0 |

0 |

1 |

1 |

1 |

Регистр режима (запись) |

0 |

1 |

0 |

0 |

0 |

Регистр режима (чтение) |

0 |

1 |

0 |

0 |

0 |

Отключение КПДП от шины данных |

1 |

X |

X |

X |

X |

В 16-разрядные регистры каналов запись производится в два этапа - сначала загружается младший байт регистра, затем старший.

Два старших разряда счетчика циклов каждого из каналов определяют коды режимов, задающих направление обмена следующим образом:

запись в память - 01;

чтение из памяти - 10;

контроль - 00.

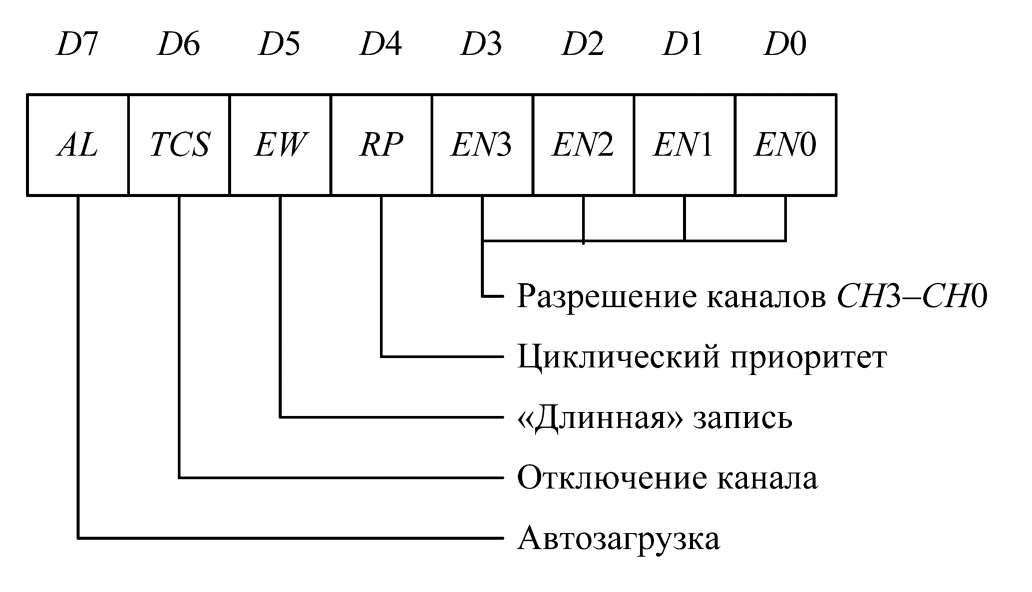

После настройки требуемых каналов в регистр режима КПДП записывается слово управления (рис. 14.3).

Рис. 14.3

Разряды D3-D0 (EN3-EN0) задают разрешение обмена по каналам CH3-CH0 соответственно, запись нуля в разряд запрещает обмен. Остальные разряды определяют режим работы каналов.

Разряд D4 (RP) устанавливает порядок обслуживания запросов от каналов. При RP = 0 задается фиксированный приоритет каналов и канал CH0 имеет высший приоритет. В режиме циклического приоритета RP = 1 после обслуживания канала ему присваивается низший приоритет, а следующий за ним по номеру - высший, и так по кругу: CH0 ^ CH1 ^ CH2 ^ ^ CH3 ^ CH0. Причем циклический сдвиг приоритетов производится после каждого цикла прямого доступа.

Режим расширенной записи (EW = 1) увеличивает за счет смещения переднего фронта длительность сигналов I/OR и I/OW, генерируемых КПДП, что позволяет обеспечить временное согласование с памятью без использования сигнала готовности READY и увеличить скорость обмена.

Разряд D6 (TCS) управляет отключением канала (запретом по концу блока). При TCS = 1 появление сигнала TC в одном из каналов сбрасывает соответствующий разряд D3-D0, в результате чего после передачи только одного блока данных канал отключается. Дальнейшая работа этого канала возможна только после перезагрузки регистра режима. Если TCS = 0, то появление сигнала ТС не воздействует на разряд разрешения работы канала и заканчивать передачу должно ВУ за счет прекращения выработки сигнала DRQ.

В режиме автозагрузки (AL = 1) может работать только второй канал, используя содержимое своих внутренних регистров и регистров третьего канала. После передачи данных в соответствии с параметрами регистров второго канала и появления сигнала TC параметры из регистров третьего канала автоматически загружаются в регистры второго канала; флаг обновления (UF) в регистре состояния каналов устанавливается в 1. Затем передача данных продолжается в соответствии с новыми параметрами регистров второго канала, а в конце первого же цикла прямого доступа с новыми параметрами флаг UF сбрасывается. Режим автозагрузки позволяет организовать повторяющиеся пересылки блоков данных с одинаковыми параметрами или соединять несколько блоков данных с разными параметрами.

При программировании КПДП операции записи информации или чтения состояний внутренних регистров определяются также значениями сигналов I/OR и I/OW: канальные регистры могут работать в режиме записи и считывания; в регистр режима можно только записать байт данных; из регистра состояния можно только считать байт данных.

После инициализации контроллер прямого доступа к памяти готов к работе.