- •1. Обобщенная структурная схема компьютера

- •2. Понятие архитектуры.

- •3. Оценка производительности компьютеров.

- •4. Классификация и краткий обзор современных компьютеров

- •5. Элементная база компьютеров: шифратор, дешифратор, мультиплексор и демультиплексор

- •6. Элементная база компьютеров: триггеры и их классификация

- •7. Эбк: регистры и их классификация

- •8. Эбк: счетчики и их классификация

- •10. Характеристики запоминающих устройств и их условные обозначения

- •11. Размещение зу на системной плате (нету)

- •12. Принцип сегментирования основной памяти компьютера и формирование физического адреса

- •13. Принципы организации современных озу

- •14. Способы адресации информации в компьютере

- •1 5. Архитектура системной платы современного пк

- •16. Структура базового процессора семейства х86 и назначение его выводов

- •17. Регистровая архитектура базового процессора семейства х86

- •18. Регистр флагов базового процессора семейства х86 и функциональное назначение его битов

- •19. Принцип демультиплексирования шины адресов и данных в мп i8086/88

- •20. Системы счисления, используемые в компьютерах и алгоритмы приеобразования из одной сс в другую

- •21. Прямые, обратные, дополнительные коды чисел и их использование в компьютерах

- •22. Представление целых чисел без знака и со знаком

- •23. Представление вещественных чисел

- •24. Представление алфавитно-цифровой информации

- •25. Представление звуковой информации

- •26. Представление визуальной информации

- •27. Форматы кодов информации (чисел и символов), используемые в пк семейства х86

- •28. Алгоритмы сложения и вычитания в комптьютерах целых двоичных чисел без знака и со знаком.

- •29. Алгоритмы слож-я и выч-я двоично-десятичных чисел

- •30. Алгоритмы сл-я и в-я вещественных чисел

- •31. Принципы осуществления в компьютерах операций умножения и деления

- •32. Назначение, определения и характеристики систем прерывания компьютеров

- •33. Классификация запросов прерывания в компьютерах

- •34. Режимы работы систем прерывания современных комптютеров и принципы их реализации

- •35. Особенности и принципы организации обмена информацей с периферийными устройствами

- •36. Принцип организации программно-управляемого ввода/вывода с активным ожиданием

- •37. Принцип организации в компьютерах ввода/вывода по прерыванию

- •38. Принцип организации ввода/вывода через каналы прямого доступа к памяти

- •39. Типовые шины соединения компонентов, используемые в современных компьютерах

- •40. Типовые устройства ввода

- •1. Клавиатура

- •2. Мышь.

- •41. Структура и назначение блоков типового видеоадаптера

- •42. Структура и назначение блоков типовой аудиосистемы

5. Элементная база компьютеров: шифратор, дешифратор, мультиплексор и демультиплексор

Шифратором (Coder) – называется комбинационное устройство, формирующее на своем выходе двоичный код номера входа, на который подано активное воздействие (сигнал).

Активным сигналом называется сигнал, который приводит к некоторым заданным изменениям в выходном сигнале (или памяти устройства). Обычно реализуют, так называемые, приоритетные шифраторы, входам которых присваивают определенные приоритеты, и поэтому на приоритетные шифраторы можно подавать активные сигналы одновременно на несколько входов. В любом случае, на выходе приоритетного шифратора всегда появится код номера наиболее приоритетного входа из тех, на которых поданы активные сигналы.

З аметим,

что шифраторы можно рассматривать как

преобразователи унитарного кода числа

в его двоичный код.

аметим,

что шифраторы можно рассматривать как

преобразователи унитарного кода числа

в его двоичный код.

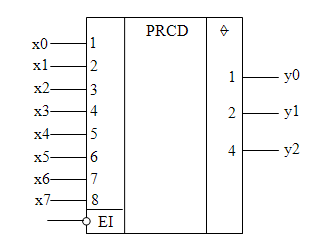

Условное графическое обозначение на функциональных схемах приоритетного шифратора, в общем случае, будет иметь вид, изображенный на рис.

Здесь: PRCD (Priority Coder) – приоритетный шифратор;

EI (Enable Input) – разрешение входа;

xi – входные сигналы;

yi – разряды выходного кода.

Приоритетные шифраторы используются, например, в АЦП параллельного преобразования для кодирования результатов, или в компьютерных системах для кодирования номера подключаемого регистра периферийного устройства.

Дешифратором (Decoder) – называется комбинационное устройство, преобразующее двоичный входной код в активный (управляющий) сигнал на одном из его выходов, номер которого соответствует входному коду.

В общем случае, дешифратор, имеющий n-двоичных разрядов, имеет 2n выходов, так как n-разрядный двоичный код может принимать 2n различных значений и каждому из них должен соответствовать активный управляющий сигнал на своем выходе. Однако на практике часто используют дешифраторы с числом выходов меньшим, чем 2n, например, дешифраторы, преобразующие двоично-десятичные коды десятичных тетрад в сигналы управления цифровыми газоразрядными индикаторами. Эти дешифраторы имеют не 16, а 10 выходов.

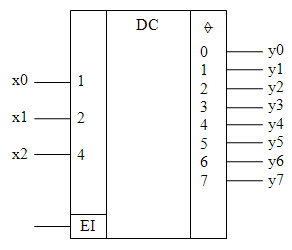

Пример условного графического обозначения на функциональных схемах дешифратора с тремя входами приведен на рис.

Здесь: DC (Decoder) – дешифратор;

xi – разряды входного двоичного кода;

yi – выходные управляющие сигналы.

EI (Enable Input) – разрешение входа;

В компьютерах дешифраторы широко используются, например, в блоках управления, в которых двоичный код операции микрокоманды преобразуется в управляющие сигналы.

Мультиплексором (Multiplexer) – называется устройство, предназначенное для управляемого переключения одного из N входных цифровых информационных каналов к одному выходному каналу.

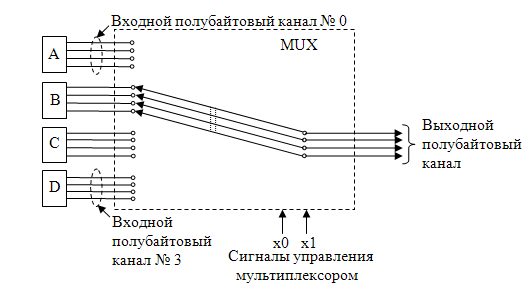

Таким образом, мультиплексор является коммутатором цифровых каналов или просто цифровым коммутатором. Цифровые информационные каналы могут быть как одноразрядные (состоящие из одной линии), так и многоразрядные, состоящие из многих линий. Так, в вычислительной технике широко используются мультиплексоры, переключающие каналы полубайтовые (4-х разрядные), байтовые (8-ми разрядные), двухбайтовые (16-ти разрядные), и другой разрядности. Сам принцип управляемой передачи цифровой информации от нескольких источников в один канал называется мультиплексированием. Принцип мультиплексирования цифровой информации иллюстрирован на рис.

Здесь: A, B, C, D – источники цифровой информации;

MUX – условное обозначение мультиплексора на схемах.

На рисунке изображено два входа управляющих сигналов х0 и х1, на которые подаются двухразрядный двоичный код управления мультиплексором, позволяющий подключать к выходному каналу один из четырех источников цифровой информации, которая передается в виде последовательности четырехразрядных двоичных кодов.

Демультиплексором (Demultiplexer) – называется устройство, осуществляющее управляемое переключение входного цифрового канала к одному из N выходных каналов.

Демультиплексор, также как и мультиплексор, относится к устройствам коммутации каналов данных, но осуществляет обратную коммутацию цифровой информации. Сам принцип управляемой передачи цифровой информации от одного входного источника к одному из нескольких возможных приемников носит название демультиплексирования.

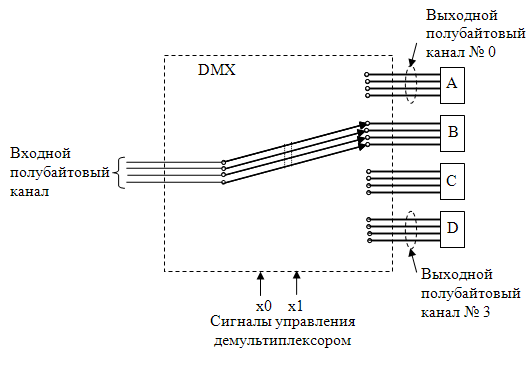

Принцип демультиплексирования иллюстрирован на рис.

З десь:

A, B, C, D – приемники цифровой информации.

десь:

A, B, C, D – приемники цифровой информации.

DMX – условное обозначение демультиплексора на схемах.

На рисунке изображены два входа управления х0 и х1. Двухразрядный двоичный управляющий код, подаваемый на эти входы, позволяет переключать цифровую информацию с входного канала на один из четырех выходных каналов.

Мультиплексирование и демультиплексирование каналов очень широко используется в компьютерной технике, например, при совмещении использования каналов передачи и приема адресов и данных, при организации связи между запоминающей матрицей и системной шиной в современных модулях оперативной памяти, таких как DDR, DDR2, DDR3 и т.д., а также при создании многопроцессорных систем.