- •1. Обобщенная структурная схема компьютера

- •2. Понятие архитектуры.

- •3. Оценка производительности компьютеров.

- •4. Классификация и краткий обзор современных компьютеров

- •5. Элементная база компьютеров: шифратор, дешифратор, мультиплексор и демультиплексор

- •6. Элементная база компьютеров: триггеры и их классификация

- •7. Эбк: регистры и их классификация

- •8. Эбк: счетчики и их классификация

- •10. Характеристики запоминающих устройств и их условные обозначения

- •11. Размещение зу на системной плате (нету)

- •12. Принцип сегментирования основной памяти компьютера и формирование физического адреса

- •13. Принципы организации современных озу

- •14. Способы адресации информации в компьютере

- •1 5. Архитектура системной платы современного пк

- •16. Структура базового процессора семейства х86 и назначение его выводов

- •17. Регистровая архитектура базового процессора семейства х86

- •18. Регистр флагов базового процессора семейства х86 и функциональное назначение его битов

- •19. Принцип демультиплексирования шины адресов и данных в мп i8086/88

- •20. Системы счисления, используемые в компьютерах и алгоритмы приеобразования из одной сс в другую

- •21. Прямые, обратные, дополнительные коды чисел и их использование в компьютерах

- •22. Представление целых чисел без знака и со знаком

- •23. Представление вещественных чисел

- •24. Представление алфавитно-цифровой информации

- •25. Представление звуковой информации

- •26. Представление визуальной информации

- •27. Форматы кодов информации (чисел и символов), используемые в пк семейства х86

- •28. Алгоритмы сложения и вычитания в комптьютерах целых двоичных чисел без знака и со знаком.

- •29. Алгоритмы слож-я и выч-я двоично-десятичных чисел

- •30. Алгоритмы сл-я и в-я вещественных чисел

- •31. Принципы осуществления в компьютерах операций умножения и деления

- •32. Назначение, определения и характеристики систем прерывания компьютеров

- •33. Классификация запросов прерывания в компьютерах

- •34. Режимы работы систем прерывания современных комптютеров и принципы их реализации

- •35. Особенности и принципы организации обмена информацей с периферийными устройствами

- •36. Принцип организации программно-управляемого ввода/вывода с активным ожиданием

- •37. Принцип организации в компьютерах ввода/вывода по прерыванию

- •38. Принцип организации ввода/вывода через каналы прямого доступа к памяти

- •39. Типовые шины соединения компонентов, используемые в современных компьютерах

- •40. Типовые устройства ввода

- •1. Клавиатура

- •2. Мышь.

- •41. Структура и назначение блоков типового видеоадаптера

- •42. Структура и назначение блоков типовой аудиосистемы

37. Принцип организации в компьютерах ввода/вывода по прерыванию

Напомним основные принципы обслуживания запросов прерывания от периферийных устройств

Периферийные устройства, при необходимости передачи информации в память компьютера, или ее приема от него, посылают в контроллер прерывания запрос прерывания в виде электрического сигнала. Эти запросы фиксируются в регистре запросов прерываний контроллера, а в процессор посылается общий запрос прерывания – сигнал INTR, который определяет наличие в данный момент хотя бы одного незамаскированного запроса прерывания от периферийных устройств. Процессор, в конце цикла выполнения каждой очередной команды опрашивает этот бит INTR и, в случае наличия разрешения приема запросов прерывания (IF = 1), приостанавливает процесс выполнения текущей программы и запоминает состояние процессора на данный момент времени (как минимум содержимое регистров CS, IP и регистра флагов Flags). После этого процессор посылает контроллеру прерывания сигнал готовности выполнять процесс обслуживания прерывания – INTA (Interrupt Acknowledge). Получив этот сигнал, контроллер прерываний выдает процессору код типа прерывания от источника, который имеет наивысший приоритет изо всех принятых к этому времени запросов на прерывания. Этот код представляет собой 8-ми разрядное слово, определяющее логический адрес (вектор) процедуры обработки данного прерывания, хранящийся в таблице векторов прерывания, расположенной в первом килобайте адресного пространства оперативной памяти.

Получив код типа прерывания, процессор по указанному коду извлекает логический адрес процедуры, формирует из него физический адрес и передает управление процедуре обслуживания данного прерывания. А эта процедура заключается в передаче в периферийное устройство, запросившее прерывание, или приеме из периферийного устройства адресуемых данных. Таким образом, ввод/вывод по прерываниям позволяет существенно сократить непроизводительное время процессора, затрачиваемое на опрос и ожидание готовности периферийных устройств к приему или выдачи информации. Однако сам процесс ввода или вывода происходит под управлением процессора и, следовательно, при операциях ввода/вывода процессор все равно отвлекается от своей основной обязанности – обработки информации. Поэтому, когда приходится вводить или выводить большие объемы данных, например, при обмене информации с дисками при свопинге, или при одновременном вводе больших объемов данных при проведении научно-технических экспериментов, то отвлечение процессора от вычислительных задач, особенно при мультипрограммном режиме работы процессора, крайне нежелательно. При этом следует учитывать, что обмен большими объемами информации осуществляется всегда блоками между периферийными устройствами и оперативной памятью компьютера.

Поэтому, в таких случаях используется более эффективная система ввода/вывода информации путем прямого доступа к памяти.

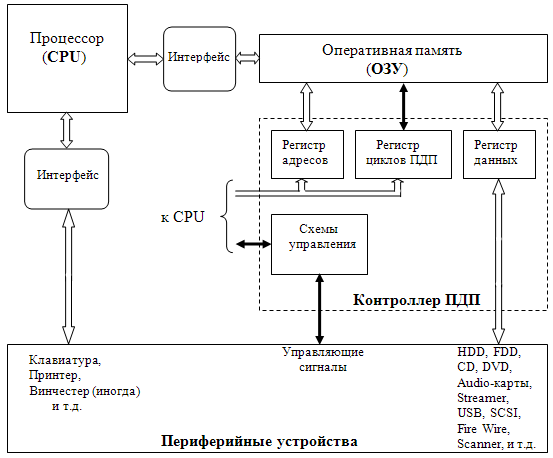

38. Принцип организации ввода/вывода через каналы прямого доступа к памяти

Прямым доступом к памяти (ПДП) называют процесс обмена информацией между периферийными устройствами (ПУ) и памятью, или между двумя областями памяти, непосредственно, минуя процессор.

Прямой доступ к памяти называют также обменом информацией по каналам DMA (Direct Memory Access).

Напомним, что пересылка слова информации между периферийным устройством и памятью, или между двумя областями памяти в предыдущих описанных способах обмена проходит в два этапа. На первом этапе процессор получает это слово из памяти или периферийного устройства и записывает в свой регистр (AL, AX, EAX). На втором этапе он записывает этот байт в место назначения. Этот способ, характерный как для программно-управляемого обмена, так и при обмене по прерыванию, имеет два недостатка:

- во время перемещения слова процессор не может заниматься ничем другим;

- на перемещение слова требуется два шага.

Это кажется мелочью, но если нужно переместить не одно слово, а целый блок это становится существенным. А обмен информацией с такими периферийными устройствами как HDD, FDD, CD и DVD – накопителями, а также Streamer’ами, осуществляется, как правило, большими массивами данных (блоками) и с большой скоростью. Звуковые карты также очень интенсивно пересылают блоки байт, и в настоящее время широко используются такие периферийные интерфейсы, как USB, Fire Wire и др. Кроме того, следует учесть, что большой объем пересылок информации необходим и при осуществлении регенерации оперативной памяти.

Поэтому, в таких случаях, используют так называемый способ прямого доступа к памяти. Для организации прямого доступа к памяти используется контроллер прямого доступа к памяти, так называемый контроллер ПДП (контроллер DMA). Раньше в компьютерах он представлял собой отдельную интегральную схему, распаянную на материнской плате, но в последних моделях компьютеров контроллер DMA, как и контроллер прерываний, входит в микросхему южного моста Chipset.

И нициализация

процесса прямого доступа к памяти

осуществляется процессором. Он настраивает

контроллер DMA на определенный режим

работы (передача память – память, память

– ПУ или ПУ – память), заносит в него

начальные адреса блоков памяти, подлежащих

обмену, а также количество передаваемых

байт в блоке. Сам процесс DMA может быть

инициирован как процессором (при передаче

память – память), так и ПУ. Запрос ПУ на

передачу DMA передается контроллеру DMA

через соответствующий вход запроса в

контроллере. После этого контроллер

DMA, который в этом случае имеет больший

уровень приоритета, чем процессор,

предлагает процессору, чтобы тот

отключился от внешних шин и передал

управление шинами контроллеру DMA.

Процессор отключается, переводя свои

выводы в третье, высокоомное состояние,

и информирует об этом контроллер DMA.

После получения этой информации

контроллер DMA берет требуемый процесс

обмена информацией полностью в свои

руки. Процессор в это время может

заниматься своими делами, продолжать

выполнение своей текущей программы,

если это не связано с обращением к

внешней шине.

нициализация

процесса прямого доступа к памяти

осуществляется процессором. Он настраивает

контроллер DMA на определенный режим

работы (передача память – память, память

– ПУ или ПУ – память), заносит в него

начальные адреса блоков памяти, подлежащих

обмену, а также количество передаваемых

байт в блоке. Сам процесс DMA может быть

инициирован как процессором (при передаче

память – память), так и ПУ. Запрос ПУ на

передачу DMA передается контроллеру DMA

через соответствующий вход запроса в

контроллере. После этого контроллер

DMA, который в этом случае имеет больший

уровень приоритета, чем процессор,

предлагает процессору, чтобы тот

отключился от внешних шин и передал

управление шинами контроллеру DMA.

Процессор отключается, переводя свои

выводы в третье, высокоомное состояние,

и информирует об этом контроллер DMA.

После получения этой информации

контроллер DMA берет требуемый процесс

обмена информацией полностью в свои

руки. Процессор в это время может

заниматься своими делами, продолжать

выполнение своей текущей программы,

если это не связано с обращением к

внешней шине.

Контроллер DMA, таким образом, при обмене информацией берет на себя целый ряд вспомогательных операций, таких как:

- буферизация данных;

- преобразование форматов данных;

- формирование очередного адреса в памяти;

- подсчет количества слов переданных данных; и т.п.

После окончания пересылки блока данных, контроллер DMA сообщает об этом процессору, который снова подключается к системным шинам и берет управление системой на себя.

Принцип организации системы прямого доступа к памяти иллюстрирован на рис.XIII.2.

В заключение следует, однако, напомнить, что программно-управляемый ввод/вывод, выполняемый командами REP INS/OUTS, может иметь производительность почти в 2 раза выше, чем обмен по каналам DMA. Поэтому часто обмен информацией с жесткими дисками (винчестерами) выполняется с помощью этих команд, несмотря на то, что процессор, при этом, будет занят.