- •1. Обобщенная структурная схема компьютера

- •2. Понятие архитектуры.

- •3. Оценка производительности компьютеров.

- •4. Классификация и краткий обзор современных компьютеров

- •5. Элементная база компьютеров: шифратор, дешифратор, мультиплексор и демультиплексор

- •6. Элементная база компьютеров: триггеры и их классификация

- •7. Эбк: регистры и их классификация

- •8. Эбк: счетчики и их классификация

- •10. Характеристики запоминающих устройств и их условные обозначения

- •11. Размещение зу на системной плате (нету)

- •12. Принцип сегментирования основной памяти компьютера и формирование физического адреса

- •13. Принципы организации современных озу

- •14. Способы адресации информации в компьютере

- •1 5. Архитектура системной платы современного пк

- •16. Структура базового процессора семейства х86 и назначение его выводов

- •17. Регистровая архитектура базового процессора семейства х86

- •18. Регистр флагов базового процессора семейства х86 и функциональное назначение его битов

- •19. Принцип демультиплексирования шины адресов и данных в мп i8086/88

- •20. Системы счисления, используемые в компьютерах и алгоритмы приеобразования из одной сс в другую

- •21. Прямые, обратные, дополнительные коды чисел и их использование в компьютерах

- •22. Представление целых чисел без знака и со знаком

- •23. Представление вещественных чисел

- •24. Представление алфавитно-цифровой информации

- •25. Представление звуковой информации

- •26. Представление визуальной информации

- •27. Форматы кодов информации (чисел и символов), используемые в пк семейства х86

- •28. Алгоритмы сложения и вычитания в комптьютерах целых двоичных чисел без знака и со знаком.

- •29. Алгоритмы слож-я и выч-я двоично-десятичных чисел

- •30. Алгоритмы сл-я и в-я вещественных чисел

- •31. Принципы осуществления в компьютерах операций умножения и деления

- •32. Назначение, определения и характеристики систем прерывания компьютеров

- •33. Классификация запросов прерывания в компьютерах

- •34. Режимы работы систем прерывания современных комптютеров и принципы их реализации

- •35. Особенности и принципы организации обмена информацей с периферийными устройствами

- •36. Принцип организации программно-управляемого ввода/вывода с активным ожиданием

- •37. Принцип организации в компьютерах ввода/вывода по прерыванию

- •38. Принцип организации ввода/вывода через каналы прямого доступа к памяти

- •39. Типовые шины соединения компонентов, используемые в современных компьютерах

- •40. Типовые устройства ввода

- •1. Клавиатура

- •2. Мышь.

- •41. Структура и назначение блоков типового видеоадаптера

- •42. Структура и назначение блоков типовой аудиосистемы

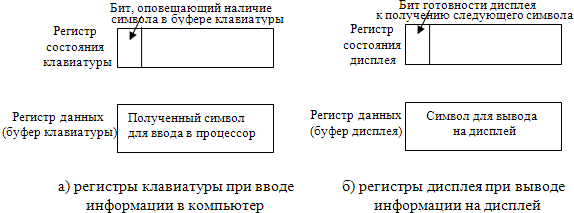

36. Принцип организации программно-управляемого ввода/вывода с активным ожиданием

Программно-управляемый ввод/вывод с активным ожиданием является самым простым и исторически самым первым методом ввода и вывода информации от внешних устройств.

При программно-управляемом вводе/выводе с активным ожиданием ввод и вывод информации в компьютере осуществляется по специальным командам ввода (IN) и вывода (OUT) c адресацией специальных регистров в периферийных устройствах. Прямая адресация с помощью этих команд позволяет адресовать не более 256 объектов, в связи с тем, что при прямой адресации под адрес выделен 1 байт кода команды. При необходимости увеличения адресного пространства периферийных устройств прибегают к косвенной адресации через регистр DX. В этом случае, адресное пространство ввода/вывода расширяется до 65536 адресов. Отметим, что одно периферийное устройство, как правило, использует несколько портов (адресов) ввода/вывода. А иногда их количество может достигать нескольких десятков. Поэтому дополнительно вводится понятие базового адреса данного периферийного устройства, который является младшим адресом группы портов, принадлежащих этому периферийному устройству (обычно адресу порта регистра данных). Это облегчает процесс программирования, поскольку адреса других портов этого устройства осуществляется путем задания смещения (целое число) относительно базового адреса.

Заметим, что в ряде компьютеров (например, в компьютерах «Macintosh», использующих микропроцессоры фирмы Motorola), не предусматривается отдельного адресного пространства периферийных устройств и, следовательно, их система команд не имеет специальных команд ввода/вывода. Обращение же к регистрам ПУ осуществляется обычными командами пересылки MOV. Таким образом, адреса этих регистров являются частью общего адресного пространства компьютера. Этот способ часто называют «распространением адресов ввода/вывода на память». Он делает адресацию устройств ввода/вывода более гибкой, поскольку позволяет использовать все возможные разновидности адресации: базовой, индексной, базово-индексной и базово-индексной со смещением. Однако, с другой стороны, такие команды обращения к внешним устройствам будут сложнее, и выполняться дольше, чем команды IN и OUT, при которых адреса ПУ образуют отдельное адресное пространство

Рассмотрим пример обращения к двум типам периферийных устройств, клавиатуре и дисплею, как простейшим устройствами с которыми связывается процессор в процессе своего функционирования (см. рис XIII.1). Вначале рассмотрим работу регистров клавиатуры.

К ак

только клавиатура, после нажатия

пользователем клавиши, сформирует и

занесет очередной код символа в свой

буферный регистр данных, аппаратно

(автоматически) заносится единица в бит

регистра состояния клавиатуры, оповещающий

о наличии символа в ее регистре данных.

ак

только клавиатура, после нажатия

пользователем клавиши, сформирует и

занесет очередной код символа в свой

буферный регистр данных, аппаратно

(автоматически) заносится единица в бит

регистра состояния клавиатуры, оповещающий

о наличии символа в ее регистре данных.

При выполнении команды IN, процессор обращается к адресуемому в команде регистру состояния и считывает этот бит наличия символа. Если этот бит равен 0, процессор зацикливается, и непрерывно опрашивает регистр состояния клавиатуры до тех пор, пока там не появится 1. После появления 1 в этом бите, процессор считывает байт символа с регистра данных клавиатуры, одновременно сбрасывая бит наличия символа в регистре состояния в 0.

Вывод информации на дисплей осуществляется аналогичным образом. Чтобы вывести символ на экран, программное обеспечение при появлении команды OUT, сначала считывает содержимое регистра состояния дисплея, чтобы узнать, установлен ли бит готовности в 1. Если он не установлен, программное обеспечение осуществляет цикл считывания снова и снова до тех пор, пока данный бит не примет значение 1. Это означает, что дисплей готов принять сигнал. Как только дисплей придет в состояние готовности, программное обеспечение заносит символ в буферный регистр данных дисплея, который переносит символ на экран и дает сигнал устройству сбросить бит готовности в регистре состояния в нулевое состояние. Когда символ уже отображен на экране, а устройство управления дисплея готово к обработке следующего символа, бит готовности снова устанавливается в состояние 1.

Основным недостатком программно-управляемого ввода/вывода с активным ожиданием является то, что процессор проводит большую часть времени в цикле опроса регистров состояния, ожидая готовности периферийного устройства к обмену информацией. Если процессору в это время все равно нечего делать, например, при управлении стиральными машинами, в этом ничего страшного нет (хотя и простейшему микрокомпьютеру часто нужно контролировать несколько параллельных процессов). Но если процессор управляет более сложными процессами, он во время активного ожидания готовности периферийных устройств мог бы эффективно выполнять в фоновом режиме и другие задачи. Поэтому, в большинстве практических случаев требуется использовать какие-то другие методы осуществления обмена информацией с периферийными устройствами.

Разновидностью программно-управляемого ввода/вывода является ввод/вывод с использованием цепочечных команд, или блочный ввод/вывод. Этот способ используется в случаях ввода или вывода цепочек данных, которые часто называют строками символов. Разница в этих названиях заключается только в том, что под строкой понимается обычно строка байт (поскольку каждый символ кодируется одним байтом). В то же время, в понятие цепочки данных включаются как последовательность символов, так и последовательность слов или даже двойных слов. При этом, байты, слова и двойные слова, которые составляют цепочку, называют элементами цепочки.

Рассматриваемый метод ввода/вывода данных основан на том, что любой однородный массив данных может быть представлен в виде цепочки соответствующих элементов. Естественно, что буферный регистр данных периферийного устройства, по своей емкости, должен всегда соответствовать размеру элемента цепочки (т.е. быть 8-ми, 16-ти или 32 разрядным). Командами, которые используются при блочном вводе/выводе, являются соответственно команды INS (IN String): - INSB, INSW, INSD, и команды OUTS (OUT String): - OUTSB, OUTSW, OUTSD, применяемые с соответствующими префиксами повторения REP. В случае необходимости переопределения сегмента источника при выводе, следует использовать полный формат цепочечных команд с операндами, т.е. OUTS DX, r/m.

Особенностями применения этих команд для ввода/вывода данных является то, что перед их исполнением в программе должно быть предусмотрено занесение в соответствующие регистры следующей предварительной информации:

- длина цепочки, (количество байт, слов или двойных слов в массиве данных, подлежащих передаче);

- место ее занесения в память компьютера (или извлечения из памяти), т.е. начальный адрес размещения цепочки;

- направление считывания (или занесения) элементов цепочки в процессе передачи (от элементов с младшими адресами к старшим, или наоборот);

- номер порта, откуда (или куда) передаются данные.

Длина цепочки (число ее элементов) заносится в регистр-счетчик процессора (CX). Номер порта заносится в регистр DX. Направление считывания (или занесения) элементов цепочки в память определяется состоянием флага DF в регистре флагов Flags. При этом, сброс этого флага в 0 командой CLD, определяет передачу начиная от элементов с младшими адресами в сторону увеличения адресов элементов, а установка этого флага в состояние 1 командой STD, определяет передачу в направление от элементов со старшими адресами к младшим.

Начальный адрес размещения массива данных при вводе задается содержимым регистра DI (EDI), при этом он будет передаваться обязательно в сегмент ES. Выводимая цепочка данных, по умолчанию, должна находиться в сегменте DS. Начальный адрес передаваемой цепочки при этом задается содержимым регистра SI (ESI). Однако выводимая цепочка данных может находиться и в другом сегменте, но для этого сегмент выводимой цепочки должен быть переопределен соответствующим префиксом переопределения.

Особенностью работы цепочечных команд является то, что они автоматически выполняют приращение (инкремент) или уменьшение (декремент) содержимого регистров SI (ESI) и DI (EDI) в зависимости от используемой цепочечной команды. При цепочках байт, изменение этих регистров происходит на 1, при цепочках слов – на 2, а при цепочках двойных слов – на 4. Инкремент регистров происходит при флаге DF = 0, а декремент – при флаге DF = 1.

При блочном программно-управляемом вводе/выводе с помощью цепочечных команд скорость передачи информации в пределах одной цепочки получается максимальной из всех возможных.

Однако, зацикливание процессора при опросе битов разрешения в регистрах состояния периферийных устройств, и при методе ввода/вывода данных с помощью организации цепочек, все равно имеет место.

От этого зацикливания можно избавиться путем организации ввода/вывода с помощью системы прерывания.