- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

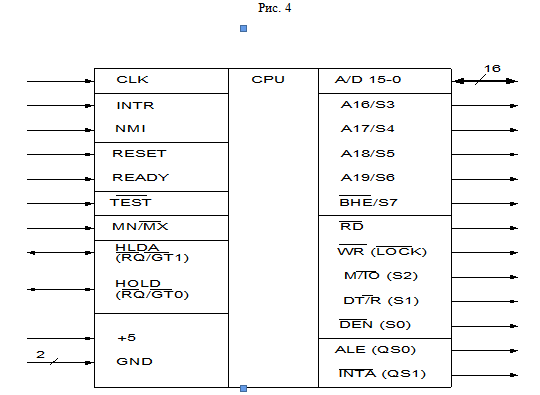

Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

Микропроцессор К1810ВМ86.

Зарубежный аналог этой микросхемы имеет обозначение i8086.

Данный микропроцессор (МП) относится к CISC типу. Он имеет 20 адресных линий (то есть может адресовать 220 =1 Мбайт ячеек ОП) и 16 линий данных. МП может работать в двух режимах: минимальном и максимальном.

Минимальный режим используется, когда на основе МП реализуется несложная однопроцес-сорная система. Для сложных однопроцессорных и многопроцессорных систем используется макси-мальный режим.

Назначение входов/выходов ВМ86 в минимальном режиме.

Обозначение МП ВМ86 на функциональных схемах приведено на рис.4. Рассмотрим назначе-ние входов-выходов МП в минимальном режиме.

CLK (clock – частота) – вход тактовых импульсов. Синхросерия на этот вход обычно подает-ся с микросхемы генератора К1810ГФ84 (i8284).

INTR (interrupt request – запрос на прерывание) – маскируемый вход запросов на прерывание. Все запросы на прерывание от внешних устройств заводятся на этот вход через схему ИЛИ. Внутри процессора имеется флаг if. Если этот флаг установлен в единицу, МП воспринимает запросы на вхо-де INTR, если установлен в ноль – игнорирует. Вход INTR называют статическим. Процессор опра-шивает сигнал на этом входе на границах команд. Поэтому сигнал на этом входе должен иметь дос-таточную длительность, иначе процессор может его «не заметить». Эту ситуацию должен учитывать разработчик аппаратуры.

INTA (interrupt acknowledge – прерывание подтверждаю) – выход подтверждения прерывания. Если МП воспринял запрос на входе INTR, он вырабатывает два сигнала на выходе INTA, подтверждая тем самым прерывание. Эти сигналы предназначены для контроллера прерываний К1810ВН59 (i8259).

NMI (non-maskable interrupt - немаскируемое прерывание) – немаскируемый вход запросов на прерывание. МП всегда воспринимает запросы, поступающие на этот вход, независимо от состояния флага if. Сигналы подтверждения прерывания при этом не вырабатываются. Этот вход называют динамическим. Внутри процессора стоит триггер, срабатывающий по переднему фронту сигнала на входе NMI. На границах команд процессор опрашивает состояние этого триггера. Таким образом требования к длительности сигнала на входе NMI существенно ниже чем к длительности сигнала на входе INTR.

RESET – сброс микропроцессора. Сигнал на этот вход подается при включении питания или при нажатии кнопки RESET. Обычно этот сигнал формируется генератором ГФ84. По этому сигналу происходит сброс в ноль всех флагов (то есть внешние прерывания запрещаются), в регистры ip, es, ds и ss загружаются нули, а в регистр cs – единицы. Так как МП всегда формирует адрес следующей команды по формуле A = (cs)×16 + (ip), то нетрудно видеть, что после сброса МП всегда стартует с адреса A = ffff0h + 0000h = ffff0h.

READY – вход готовности. При обращении к памяти или порту внешнего устройства МП все-гда выполняет так называемый цикл шины. Этот цикл состоит из четырех тактов (Т1, Т2, Т3 и Т4). Вначале такта Т4 происходит обмен информацией между МП и ОП или ВУ. Однако если в системе стоит медленная память, она может к этому моменту оказаться не готовой к обмену. В этом случае внешние схемы должны сформировать нулевой сигнал на входе READY, означающий, что устройст-во к обмену не готово. В такте Т3 МП проверяет вход READY и, если на нем единица, переходит к такту Т4. В противном случае МП вводит между тактами Т3 и Т4 такты ожидания. В каждом такте ожидания МП опрашивает вход READY и так до тех пор, пока на READY не появится единица.

TEST – МП проверяет сигнал на входе TEST, только когда он выполняет команду wait. Если при этом на входе TEST стоит ноль, МП переходит к следующей команде. В противном случае МП вводит «холостые» такты и через каждые пять тактов снова опрашивает вход TEST. Обычно этот вход используется при стандартном подключении арифметического сопроцессора К1810ВМ87 (i8087).

MN/MX (minimum/maximum) – если на этот вход «запаяна» единица, МП работает в минималь-ном режиме, если ноль – в максимальном.

HOLD – захват. В минимальном режиме это вход. Если на этот вход приходит единица, МП прекращает выполнение текущей команды и отключается от шин. После этого МП находится в со-стоянии «спячки» до тех пор, пока на HOLD не появится ноль. Обычно сигнал на вход HOLD фор-мирует контроллер прямого доступа к памяти.

HLDA (hold acknowledge) – подтверждение захвата. В минимальном режиме это выход. Этот сигнал обычно заводится на контроллер прямого доступа к памяти и сообщает последнему, что он может брать управление системной шиной на себя.

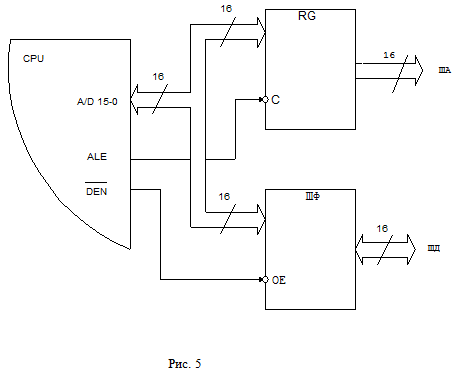

A/D 15-0 (address/data) –16-ти разрядная мультиплексная шина адрес/данные. По этим линиям передается как адрес, так и данные, конечно в разные моменты времени. На эти линии МП выставля-ет 16 младших разрядов адреса при обращении к ОП, и весь адрес при обращении к порту ВУ. Адрес на эти линии выставляется в такте Т1 в сопровождении стробирующего сигнала на выходе ALE. В такте Т2 адрес снимается и далее по этим линиям происходит передача данных в сопровождении сигнала на выходе DEN. Поскольку адрес необходим нам до конца цикла шины (до такта Т4), его необходимо запоминать во внешнем регистре. Кроме того, для правильной работы системы шину адрес/данные демультиплексируют, то есть разделяют на шину адреса (ША) и шину данных (ШД), как показано на рис. 5. Здесь ШФ – шинные формирователи.

А16 – А19 – при обращении к ОП на эти линии МП выставляет старшие четыре разряда адреса. В такте Т2 адрес с этих линий снимается (то есть его также надо запоминать во внешнем регистре) и на эти линии МП выставляет сигналы состояния S3 – S6 (state). Последние обычно используются только при отладке системы.

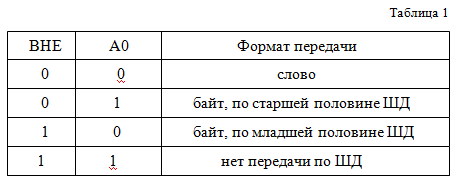

BHE (bus high enable)– разрешение старшей половины шины данных. МП может производить обмен по ШД как словами (2 байта), так и отдельными байтами. В последнем случае байт может пе-редаваться по старшей или по младшей половине ШД. Для решения этой проблемы и предназначен сигнал BHE. Если на BHE стоит ноль, то в данном цикле шины по старшей половине ШД будут пере-даваться данные. Совместно с сигналом на линии А0 сигнал BHE задает формат передачи информа-ции по шине данных (смотри табл. 1).В такте Т2 сигнал BHE снимается и, следовательно, его надо запоминать во внешнем регистре. Далее на эту линию выставляется зарезервированный фирмой сиг-нал состояния S7.

RD (read)– чтение. Сигнал вырабатывается, когда МП выполняет операцию считывания ин-формации из ОП или порта ВУ.

WR (write) – запись. Сигнал вырабатывается, когда МП выполняет операцию записи информа-ции в ОП или порт ВУ.

M/IO (memory/input-output)– память/ВУ. Если МП обращается к ОП, на этот выход выставля-ется единица, если к ВУ – ноль. Данный сигнал позволяет разделить адресное пространство портов и адресное пространство памяти.

Сигналы RD, WR и M/IO подаются на внешние логические схемы, которые формируют сис-темные управляющие сигналы MR («читаю память»), MW («пишу в память»), IOR («читаю порт») и IOW (« пишу в порт»).

DT/R (data transmit/receive –отправка/получение информации) – сигнал, дублирующий пару сигналов RD и WR. Если на выходе DT/R стоит единица, МП выдает информацию, если ноль – при-нимает. Сигнал используется для управления шинными формирователями, стоящими на ШД, задавая направление передачи информации, он более удобен для этой цели чем RD и WR, поскольку имеет большую длительность.

DEN (data enable – информация доступна) – сигнал, стробирующий передачу информации по ШД.

ALE (address latch enable – разрешено защелкнуть адрес)– сигнал, стробирующий выдачу ад-реса.