- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

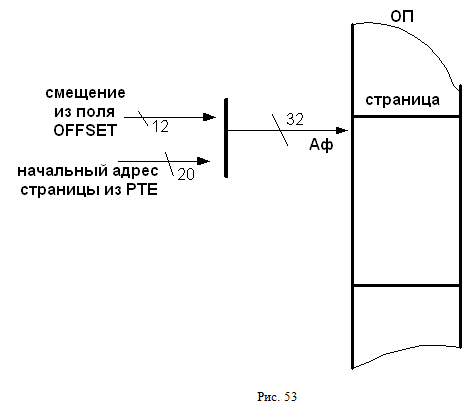

Форматы машинных команд.

Машинной командой называется двоичное слово, содержащее всю информацию, необходи-мую процессору для выполнения заданной операции. А именно:

тип операции;

адреса операндов;

адрес приемника результата.

Для фиксации этой информации в машинной команде выделяются группы разрядов, называемые по-лями. Любая машинная команда состоит из поля кода операций (КОП) и ряда адресных полей. Фор-матом машинной команды называется заранее оговоренная структура ее полей.

В наиболее общем случае машинная команда должна иметь формат, представленный на рис.3.

Здесь А1 – поле адреса первого операнда, А2 – поле адреса второго операнда, А3– поле адреса приемника результата, А4 – поле адреса следующей машинной команды. Это, так называемая, четырехадресная машинная команда.

Очевидно, что чем больше в команде полей, тем больше места занимает команда в оперативной памяти (ОП). Это в свою очередь приводит к непроизводительному расходу памяти и снижению общего быстродействия ЭВМ, так как считывание таких команд из ОП требует больших временных затрат.

На практике четырехадресные машинные команды никогда не использовались. Действительно, машинные команды любой программы располагаются в ОП не хаотично, а последовательно, одна за другой. Поэтому в состав процессора вводится специальный регистр, называемый программным счетчиком. Перед началом выполнения программы, в него заносится адрес первой команды программы. После считывания очередной машинной команды из ОП содержимое программного счетчика автоматически увеличивается на число считанных байт. Таким образом в программном счетчике автоматически формируется адрес следующей машинной команды программы. При таком подходе поле А4 становится ненужным и команда становится трехадресной.

Договоримся теперь, что результат операции мы всегда будем помещать на место одного из операндов, например первого. При этом отпадает необходимость в поле А3 и команда становится двухадресной. Хотя при таком подходе команды несколько теряют в гибкости и создаются определенные неудобства при программировании, практика показала, что выйгрыш здесь значительно превышает пройгрыш.

Иногда в состав процессора вводят специальный регистр, называемый аккумулятором, и оговаривают, что один из операндов всегда берется из аккумулятора и в него же загружается результат операции. При такой ситуации команды становятся одноадресными.

Существуют и безадресные команды, например команды, реализующие стековые операции.

В современных процессорах используются, как правило двух-, одно- и безадресные команды. Например команды микропроцессора К1810ВМ86:

add dx, [234h] – двухадресная

inc byte ptr [40h] – одноадресная

push bx – безадресная.

Описание страничного механизма.

Этот механизм, в отличие от сегментного мы можем включать и выключать по своему жела-нию. Правда эта задача относится к прерогативе системного программиста, а не пользователя. Для того чтобы включить страничный механизм достаточно установить в единицу бит PG в регистре cr0. Это старший (31-й) бит этого регистра. Сделать это можно только командой mov cr0 , r 32 . Ко-манда lmsw r 16 / m 16 здесь не годится, так как она загружает только младшую половину cr0. При попытке включить страничный механизм в реальном режиме будет прерывание.

К серьезным недостатком сегментного механизма относится трудность организации подкачки сегментов с диска, поскольку сегменты имеют разные размеры и могут быть очень большими по объ-ему. В отличие от сегментов страницы имеют фиксированный размер 4 Кбайта и располагаются в строго определенных местах ОП. Нулевая страница располагается в адресах 00000000h - 00000fffh, первая - в адресах 00001000h - 00001fffh и. т. д. Пересекаться страницы не могут. Отметим, что в Pen-tium используются страницы размером 4 Кбайта и 4 Мбайта, а в Р6 – 4 Кбайта, 4 Мбайта и 2 Мбайта. В дальнейшем будем называть страницы объемом 4 Кбайта обычными, а 4 Мбайта и 2 Мбайта – большими. В данном разделе речь пойдет только об обычных страницах.

Двенадцать младших разрядов начального адреса любой обычной страницы всегда равны ну-лю. Поэтому любой объект в памяти, имеющий подобный начальный адрес, называется выровнен-ным по границе страницы.

Нетрудно видеть что всего в ОП может быть создано 220 страниц (4 Гбайта делить на 4 Кбай-та). Все страницы объединяются в блоки. В один блок может входить до 210 страниц, при этом совсем необязательно подряд идущих. Иначе говоря в блок могут входить 100-я страница, 5-я страница, 346-я страница и. т. д. Для каждого блока создается так называемая таблица страниц. Каждый эле-мент этой таблицы описывает одну из входящих в блок страниц. Элемент таблицы страниц занимает в памяти 4 байта и называется элементом PTE (page table entry). Элемент PTE содержит начальный адрес (вернее 20 старших разрядов этого адреса, поскольку 12 младших все равно равны нулю) и атрибуты страницы, которую это элемент описывает. Нетрудно видеть что одна таблица страниц занимает в памяти ровно одну страницу ( 210 × 4 байта = 4 Кбайта). Соответственно любая таблица страниц выровнена по границе страницы, то есть 12 младших разрядов ее начального адреса равны нулю. Так же легко видеть что блоков, а следовательно и таблиц страниц может быть создано до 210.

Для всех таблиц страниц в памяти создается каталог таблиц. Он также занимает в памяти ровно одну страницу и выровнен по ее границе. Элементы каталога (они называются PDE (page directory entry)) аналогичны элементам PTE, только описывают они не страницы, а таблицы страниц. Начальный адрес ( вернее его 20 старших разрядов) каталога задаются МП в регистре cr3. При вклю-ченном страничном механизме каталог всегда должен находиться в ОП, а таблицы и страницы могут находиться как в памяти, так и на диске. Если идет обращение к странице (или таблице), которая на-ходится на диске происходит прерывание. Обработчик этого прерывания должен подкачать страницу с диска после чего производится рестарт команды.

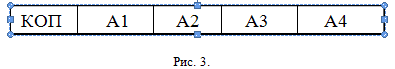

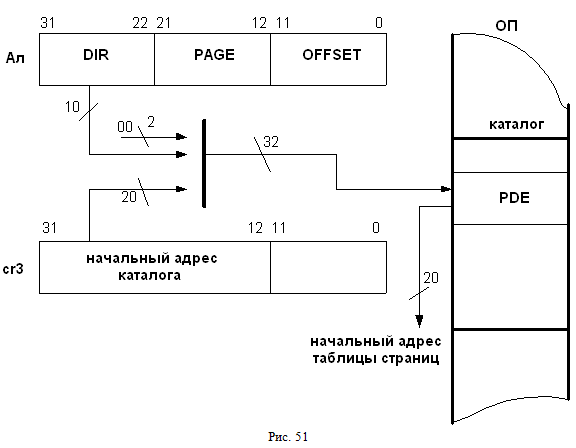

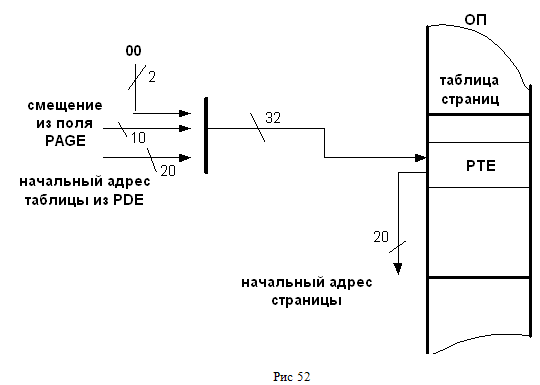

При включенном страничном механизме адрес, вырабатываемый сегментным механизмом (раньше мы его все время называли физическим), еще не является физическим адресом. Этот адрес принято называть линейным ( Ал). Линейный адрес условно разбивается на три части (поля). Поле DIR задает смещение в каталоге, поле PAGE - смещение в таблице, а поле OFFSET - смещение в самой странице. Далее на трех рисунках (рис 51-53) приводится графическая интерпретация работы страничного механизма с соответствующими пояснениями.

Итак вначале у нас работает сегментный механизм, который формирует линейный адрес Ал. Затем начинает работать страничный механизм. МП берет из регистра CR3 20 старших разрядов начального адреса каталога, «пристыковывает» к ним 10-ть разрядов из поля DIR линейного адреса и в младшие разряды добавляет два нуля (рис. 51). Тем самым МП формирует адрес элемента PDE. Элемент PDE занимает в памяти 4 байта и всегда выровнен по границе двойного слова, именно поэтому два младших разряда его адреса берутся равными нулю. Из найденного в памяти элемента PDE процессор извлекает начальный адрес таблицы страниц (вернее 20 старших разрядов этого адреса) и переходит к следующему этапу (рисю 52).

Собственно этот этап очень похож на предыдущий. К 20 старшим разрядам начального ад-реса страницы, взятым из PDE, МП «пристыковывает» 10 разрядное смещение из поля PAGE линей-ного адреса Ал и в младшие разряды дописывает два нуля. Таким образом МП формирует адрес эле-мента PTE, из которого он извлекает начальный адрес страницы ( вернее опять таки 20 старших разрядов этого адреса). Затем МП переходит к последнему этапу формирования физического адреса (рис. 53).

На этом этапе к 20 старшим разрядам начального адреса страницы, взятым из PTE, «пристыковывается» 12 разрядное внутристраничное смещение из поля OFFSET линейного адреса Ал. В результате получается «долгожданный!» физический адрес Аф.

Как видно страничный механизм весьма громоздкий и требует только для формирования физи-ческого адреса двух обращений в память. Если это механизм будет всегда работать ожидать от МП высокого быстродействия не приходится. Поэтому для повышения быстродействия в состав МП вве-дена кэш-память страниц (буфер TLB (translation lookaside buffer – «буфер предыстории трансля-ции»)). В этом буфере хранятся начальные адреса 32-х страниц, к которым были последние обраще-ния процессора. После того как сегментный механизм выработал Ал, МП прежде всего ищет началь-ный адрес нужной страницы в буфере TLB и только если его там не окажется (а это бывает крайне редко так как процент кэш-попаданий в буфер составляет 95%) включается рассмотренный выше страничный механизм. Работа буфера TLB будет рассмотрена далее.

Страничный механизм предоставляет программисту (системному) следующие возможности:

дает возможность упростить алгоритмы подкачки информации с диска, поскольку обмен информацией с диском ведется страницами, имеющими одинаковый небольшой размер;

устраняет возможность возникновения фрагментации памяти ( при обмене с диском разно-размерными сегментами в памяти неизбежно возникают «дыры»);

позволяет «транслировать» вырабатываемые процессором линейные адреса в другие области ОП. Когда программист пишет команду, адресующую ОП он задает в этой команде адрес. Сегментный механизм преобразует этот адрес в Ал, а страничный механизм преобразует Ал в Аф. При этом как правило Аф совсем «не похож» на Ал. Поэтому и говорят что процессор транслирует Ал в другое место ОП. Например, пусть сегментный механизм выработал Ал = 00000008h, а в элементе PTE, к которому мы обратимся по ходу работы страничного механизма (кстати из Ал видно что этот PTE будет 0-м элементом соответствующей таблицы страниц) в поле «начальный адрес страницы» задано 777ffh. Тогда Аф будет равен 777ff008h. Не трудно создать страницу для которой линейные адреса будут совпадать с физическими, для этого надо записать соответствующую информацию в соответствующие элементы PDE и PTE. Такие страницы называются страницами с прямым отображением в память. Возможность трансляции адресов является важным свойством страничного механизма и широко используется на практике. Приведем наиболее простой пример. Если какую-то страницу мы из ОП сбросили на диск, а потом вернули обратно в память эта страница скорее всего окажется совсем в другом месте ОП. Ничего страшного, достаточно изменить информацию в соответствующем PTE и вырабатываемые при обращении к этой странице адреса будут транслироваться в новое место ОП.