- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

Данная микросхема включает в себя четыре независимых канала ПДП: соответственно канал 0, канал1, канал 2 и канал 3. Каждый канал может находится в двух основных режимах: режиме программирования и режиме ПДП. В процессе программирования канал может быть настроен на работу в следующих режимах:

Режим одиночной передачи. В этом режиме канал осуществляет передачу байта информации между ОП и портом ВУ, после чего КПДП возвращает шину МП. В этом режиме можно задавать блок информации, но передаваться он будет побайтно.

Режим блоковой передачи. В этом режиме канал производит передачу блока информации. КПДП не возвращает шину МП до тех пор, пока не будет передан весь блок.

Режим передачи по требованию. По смыслу это та же блоковая передача, однако, после передачи каждого байта КПДП проверяет вход запроса на ПДП (DREQ) канала. Если на нем стоит активный сигнал, значит ВУ готово к дальнейшему обмену и передача продолжается. Если на DREQ стоит пассивный сигнал, значит ВУ к дальнейшему обмену не готово, передача прекращается (до нового запроса от этого ВУ) и шина возвращается МП.

Каскадный режим. В системе может стоять несколько КПДП, но при этом они соединяются каскадно (один ведущий, остальные ведомые). Сигнал с выхода HRQ ведомого заводится не на вход HOLD МП, а на вход DREQ одного из каналов ведущего. Если какой-либо канал КПДП настроен на каскадный режим, значит к входу DREQ этого канала подключен ведомый контроллер.

Существует специфический вид передачи, который называется «память – память». Как следует из названия, обмен здесь идет не между ОП и ВУ, а между двумя областями ОП. Для такой передачи используются два фиксированных канала: канал 0 и канал 1. В канале 0 задается начальный адрес области ОП, откуда будет передаваться информация. В канале 1 – начальный адрес области ОП, куда будет передаваться информация, и размер передаваемого блока. Запрос на передачу «память – память» подается на канал 0. Получив этот запрос КПДП за один цикл шины считывает из ОП байт, адрес которого он берет из канала 0, и помещает его в свой внутренний регистр временного хранения. Затем КПДП формирует второй цикл шины, в котором этот байт записывается в ОП, по адресу, взятому из канала 1. После этого производится автодекремент счетчика байт и автоинкремент (или автодекремент) адресов в каналах 0 и 1. И так далее.

При передаче «память – память» можно использовать режим автофиксации, при котором в процессе передачи адрес в канале 0 не меняется. То есть этот режим позволяет заполнять заданную область памяти константой.

Режим «память – память» используется, например, для регенерации динамического ОЗУ.

Обычно по окончании передачи блока канал надо перепрограммировать. Однако, если канал настроен на автоинициализацию, перенастройка канала не требуется, поскольку канал автоматически перезагружается исходными данными.

Во избежание конфликтных ситуаций, всем каналам КПДП присваивается приоритет. По умолчанию старший приоритет имеет канал 0, однако мы можем программно изменять приоритеты каналов.

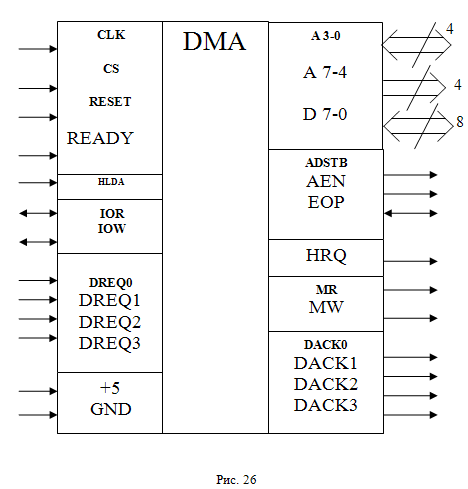

На рис. 26 приведено обозначение ВТ37 на функциональных схемах.

Рассмотрим вкратце назначение входов/выходов ВТ37.

CLK – вход синхроимпульсов, синхросерия подается с генератора ГФ84, КПДП использует эту синхросерию, находясь в режиме ПДП, для формирования циклов шины.

CS – выбор кристалла, нужен в режиме программирования, активный сигнал на этом входе означает что процессор обращается к одному из внутренних регистров КПДП. В режиме ПДП вход CS блокируется.

RESET – сброс. По этому сигналу все каналы переводятся в режим программирования. Все каналы при этом маскируются, то есть запрещается восприятие запросов от ВУ по линиям DREQ 3-0. Поэтому после программирования канала последний надо демаскировать.

READY – готовность. Аналогичен одноименному входу ВМ86. Используется в режиме ПДП. С помощью этого входа синхронизируется работ КПДП и медленнодействующих ОП и или ВУ.

HLDA – подтверждение захвата. Сигнал на этот вход заводится с одноименного выхода МП. Когда на HLDA приходит активный сигнал, КПДП берет управление системной шиной на себя.

IOR и IOW – в режиме программирования это входы. Сигналы на них задают КПДП вид операции, с которой обращается к нему МП. В режиме ПДП это выходы. На них КПДП выставляет сигналы, задающие вид операции порту ВУ.

DREQ 3-0 (DMA request) – входы запросов на ПДП для каналов 3-0. Активный уровень этих сигналов задается при программировании.

А3-0 и А7-4 – на этих линиях в режиме ПДП контроллер формирует младший байт адреса ОП. Адрес на этих линиях стоит до конца цикла шины и его не надо запоминать во внешнем регистре. В остальное время линии А3-0 являются входами. Комбинация сигналов на этих входах задает внутренний регистр КПДП. То есть внутри КПДП имеется шестнадцать адресуемых устройств.

D 7-0 – линии адрес/данные. В режиме ПДП в такте Т1 контроллер выставляет на эти линии старший байт адреса ОП. В такте Т2 адрес с этих линий снимается, поэтому его надо фиксировать во внешнем регистре. В остальное время эти линии представляют собой двунаправленную шину данных.

Из вышеизложенного следует, что ВТ37 вырабатывает 16-ти разрядный адрес и может адресовать только 64 Кбайт памяти. Для того, чтобы КПДП мог адресовать 1 Мбайт, в систему вводят страничные регистры (по одному на каждый используемый канал). В эти регистры программист заранее загружает четыре старших разряда адреса. Чтобы обратиться к другой области памяти, надо сменить содержимое страничного регистра.

ADSTB – сигнал, сопровождающий выдачу адреса. Используется для фиксации старшего байта адреса, формируемого на линиях D 7-0 во внешнем регистре.

AEN (address enable) – активный сигнал на этот выход выставляется в режиме ПДП. Обычно этот сигнал используется для блокирования доступа к шине со стороны других устройств системы.

EOP (end of process) – конец операции. Активный сигнал на этом выходе устанавливается, когда счетчик байт канала переходит через ноль. Этот сигнал может оповещать ВУ об окончании передачи. Линия EOP может использоваться и как вход. Если в режиме ПДП внешним образом сформировать на этой линии активный (нулевой) сигнал, передача прекращается.

HRQ (hold request) – запрос на захват. Подается на вход HOLD МП, отключая последний от системной шины.

MR и MW – сигналы на этих выходах в режиме ПДП задают вид операции для ОП.

DACK 3-0 (DMA acknowledge) – подтверждение ПДП для каналов 3-0. Используются для подключения портов ВУ к шине данных. Активный уровень сигнала на этих выходах задается при программировании контроллера.

В IBM PC/XT стоит один КПДП ВТ37. Его регистрам присвоены системные адреса 00h –0fh. Страничные регистры (порты) в ХТ имеют системные адреса:

81h - для канала 2;

82h – для канала 3;

83h – для канала 1;

87h – для канала 0.

Начиная с PC/AT, в системе стоят два ВТ37, соединенных каскадно.