- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

Билет №8 Программируемый адаптер к1810вв55 (i8255)

Эта микросхема наиболее часто используется для организации параллельных портов ввода-вывода в системах, построенных на базе МП фирмы Intel.

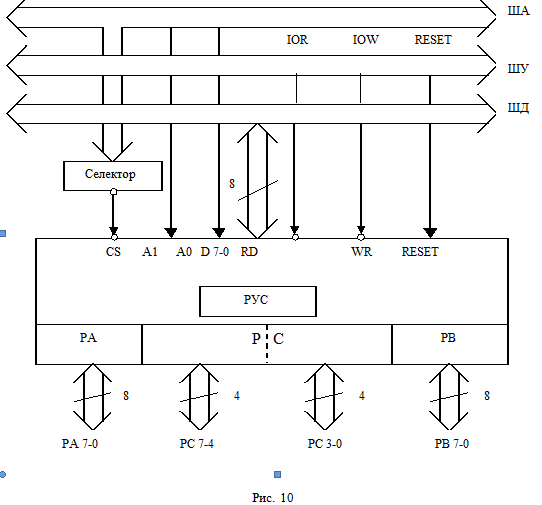

Схема подключения адаптера к СШ представлена на рис.10. Рассмотрим назначение вхо-дов/выходов адаптера.

CS (chip select – «выбор кристалла»). На этот вход через схему селектора (дешифратора) фор-мируется активный (нулевой) сигнал, когда МП выставляет на ША адрес одного из внутренних реги-стров адаптера. Сложность схемы селектора сильно зависит от организации системы. В простых сис-темах с малым числом портов селектор может вообще отсутствовать. Активный сигнал на CS под-ключает адаптер к ШД.

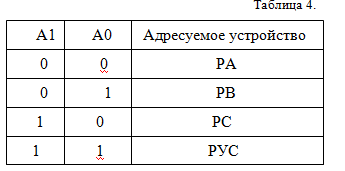

С точки зрения программиста внутри адаптера имеются четыре адресуемых устройства: порт A (PA), порт B (PB), порт С (РС) и регистр управляющего слова (РУС). К какому из четырех внутрен-них устройств обращается МП, когда на CS приходит активный сигнал, определяет информация на входах А1 и А0 (табл. 4).

D 7-0 – восьмиразрядная шина данных. По ней производится обмен информацией, в том числе и управляющей, между МП и внутренними устройствами адаптера.

Вход RD – «чтение». Задает вид операции. На этот вход заводится системный управляющий сигнал IOR.

Вход WR – «запись». На этот вход заводится системный управляющий сигнал IOW.

RESET – сброс. По этому сигналу все порты адаптера настраиваются на ввод в режиме 0. Как правило, этот вход на практике не используется.

РА – восьмиразрядный порт, который может быть настроен на ввод или на вывод в одном из трех режимов: режиме 0, режиме 1 или режиме 2.

РВ – восьмиразрядный порт, который может быть настроен на ввод или на вывод в одном из двух режимах: режиме 0 или режиме1.

РС – восьмиразрядный порт, который можно настроить на ввод или на вывод в режиме 0. В от-личие от РА и РВ порт С разбит на две половины: старшую и младшую, каждую из которых можно независимо настроить на ввод или на вывод.

Режимы 1 и 2 на практике используются редко, поэтому мы здесь ограничимся рассмотрением режима 0.

Пусть, например, порт А настроен на ввод в режиме 0. Когда МП обращается к этому порту командой in al, port_A информация с внешних линий РА попадает на ШД. То есть в этом случае порт работает как коммутатор и передаваемая информация внутри адаптера не фиксируется.

Пусть РА настроен на вывод в режиме 0. По команде out port_A, al информация с ШД поступит в РА и там защелкнется. Естественно, что эта информация появится при этом и на внешних линиях РА.

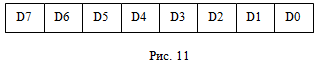

Перед началом работы все порты адаптера должны быть настроены. Для этого достаточно пе-редать в РУС настроечное слово, формат которого приведен на рис. 11.

Здесь D7 = 1. Эта единица и означает, что передается настроечное слово. При D7 = 0 передается специальная команда, которая здесь рассматриваться не будет.

D6, D5 – определяют режим работы РА:

00 – режим 0;

01 – режим 1;

10 – режим 2;

11 – тоже режим 2.

D4 = 1 – РА настраивается на ввод.

= 0 – РА настраивается на вывод.

D3 = 1 –старшая часть РС (линии РС 7-4) настраивается на ввод.

= 0 – старшая часть РС настраивается на вывод.

D2 = 1 – РВ настраивается на режим 1.

= 0 – РВ настраивается на режим 0.

D1 = 1 – РВ настраивается на ввод.

= 0 – РВ настраивается на вывод.

D0 = 1 – младшая часть РС (РС 3-0) настраивается на вывод.

= 0 – младшая часть РС настраивается на ввод.

В IBM PC/XT стоит микросхема ВВ55. При этом ее портам присвоены следующие системные адреса:

PA = 60h;

PB = 61h;

PC = 62h;

РУС = 63h.

При начальном старте XT выполняет две команды:

mov al, 99h

out 63h, al

то есть в РУС загружается двоичное число 10011001. Таким образом, все порты настраиваются на работу в режиме 0, РА и обе половины РС на ввод, а РВ на вывод. Начиная с IBM PC/AT, микросхема ВВ55 в системе отсутствует, но порты 60h и 61h существуют и выполняют те же функции.