- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

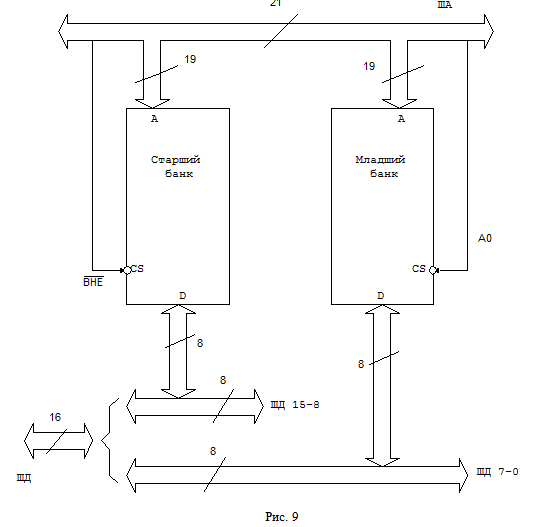

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

Микропроцессор К1810ВМ86.

Зарубежный аналог этой микросхемы имеет обозначение i8086.

Данный микропроцессор (МП) относится к CISC типу. Он имеет 20 адресных линий (то есть может адресовать 220 =1 Мбайт ячеек ОП) и 16 линий данных. МП может работать в двух режимах: минимальном и максимальном. Минимальный режим используется, когда на основе МП реализуется несложная однопроцес-сорная система. Для сложных однопроцессорных и многопроцессорных систем используется макси-мальный режим.

Организация адресного пространства портов ВУ

Существует два основных способа организации адресного пространства портов ВУ.

1) Раздельная организация адресных пространств ОП и портов ВУ. В этом случае к портам об-ращаются командами in и out, а к ОП – остальными командами. Соответственно МП выставляет еди-ницу на выходе M/IO, если он обращается к ОП и ноль, если он обращается к порту. Таким образом сигнал на выходе M/IO позволяет различить ячейку памяти и порт, даже если они имеют одинаковые системные адреса.

В командах in и out можно использовать два типа адресации: прямую и косвенную. При пря-мой адресации адрес порта указывается в команде непосредственно (например, in al,60h) и имеет размер 1 байт. То есть таким способом мы можем задать 256 различных адресов портов. Учитывая, что МП вырабатывает сигналы RD и WR, мы можем считать, что при прямой адресации в системе можно использовать максимум 512 портов, половина из которых работает на ввод информации, а другая половина – на вывод.

При косвенной адресации адрес порта берется из регистра dx (например, out [dx],al). Посколь-ку данный регистр шестнадцатиразрядный, то, исходя из тех же соображений, в систему максимально можно поставить 128К портов, половина из которых работает на ввод, а другая половина – на вывод.

2) Отображение адресного пространства портов на адресное пространство памяти. При таком способе порты рассматриваются как ячейки ОП. Соответственно обращение к таким портам произво-дится командами обращения к памяти, а не командами in и out. Сигнал на выходе M/IO при обраще-нии к таким портам будет равен единице. Следовательно, такие порты и ячейки памяти не могут иметь одинаковые адреса. Такой способ позволяет наращивать число портов вплоть до 1М, правда за счет уменьшения объема ОП. В чистом виде на практике этот способ применения не находит, однако зачастую его используют в сочетании с первым способом.

Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

Реальный режим. С точки зрения пользователя МП в этом режиме представляет собой аналог МП i8086, только более быстрый и с расширенной системой команд. Механизм формирования физического адреса в реальном режиме аналогичен подобному механизму МП i8086:

Аф = (sr)×16 + Аэф.

Так как сегментные регистры (sr) и Аэф – 16 разрядные, формируемый таким образом Аф будет 20 разрядным. Следовательно в реальном режиме МП адресует 1Мбайт оперативной памяти (младший мегабайт 4 Гбайтного пространства памяти). Сегменты, как и в i8086 имеют фиксированный размер 64Кбайта.

Режим виртуального i8086 (V86). Этот режим предназначен для того, чтобы в защищенном режиме у нас была возможность выполнять программы, написанные для i8086 (DOS задачи). Работа процессора в этом режиме похожа на работу i8086, но сам режим V86 является подмножеством защищенного режима.

Защищенный режим. В этом режиме раскрываются все возможности МП. В этом режиме используются все 32 адресных линии и следовательно может адресоваться память объемом до 4 Гбайт. Сегменты в защищенном режиме имеют переменный объем (от 1 байта до 4 Гбайт). Одновременно МП может работать с 214 таких сегментов. Очевидно, что все эти сегменты могут не поместиться в реально существующей оперативной памяти (ОП), поэтому часть из них (а скорее всего большинство) находится на диске. Когда процессор обращается к сегменту, которого нет в ОП происходит прерывание. Обработчик этого прерывания должен подкачать с диска в ОП нужный сегмент, после чего происходит рестарт «виноватой» команды. От пользователя этот процесс скрыт и у него создается впечатление что в его распоряжении находится виртуальная память объемом 64 Тбайта (214 сегментов по 4 Гбайта каждый, то есть 246 байт).

В защищенном режиме МП аппаратным образом поддерживает многозадачность. То есть в системе одновременно может находиться множество задач, а МП обеспечивает быстрое переключение между этими задачами. Наличие многозадачности приводит к ряду проблем, основные две из которых:

как переключаться с задачи на задачу;

как защитить задачи друг от друга.

Для решения первой проблемы для каждой задачи в системе создается так называемый «сегмент состояния задачи» (TSS – task state segment). Размер этого сегмента должен быть не менее 104-х байт. Когда МП переключается с задачи А на задачу В он автоматически запоминает контекст задачи А (содержимое почти всех своих внутренних регистров) в TSS задачи А, а затем также автоматически загружает в свои регистры контекст задачи В (из TSS задачи В). Тем самым обеспечивается переключение на задачу В и в то же время возможность возврата и продолжения выполнения задачи А. Вообще под задачей понимается любой программный код, для которого в системе создан свой TSS. Создание TSS -это функция операционной системы.

Для решения проблемы защиты задач друг от друга всем создаваемым в системе сегментам присваивается уровень привилегий. Всего возможно четыре уровня привилегий: 0,1,2 и 3, причем 0-й уровень самый старший. Уровень 3 (самый низкий) присваивается обычно сегментам пользователя, уровень 0 - сегментам ОС, а уровни 1 и 2 предназначены для расширения ОС и на практике зачастую не используются .

Когда программа с уровнем привилегий А обращается к сегменту с уровнем привилегий В процессор проверяет условие А <= В. Если это условие выполняется доступ к сегменту будет предоставлен, если же условие не выполняется будет прерывание (нарушены права доступа к сегменту).

Механизм формирования физического адреса в защищенном режиме радикально отличается от механизма i8086. Для каждого создаваемого в системе сегмента создается (как правило ОС) специальная структура, называемая дескриптором этого сегмента. Дескриптор занимает в памяти 8 байт и содержит все необходимые сведения о сегменте: начальный адрес сегмента, размер сегмента, уровень привилегий, атрибуты сегмента и.т.д. МП вычисляет физический адрес по формуле:

Аф = начальный адрес сегмента + Аэф.

При этом, в отличие от i8086, начальный адрес сегмента не вычисляется, а берется готовым из дескриптора.

Все созданные в системы дескрипторы сводятся в дескрипторные таблицы. Любая задача может одновременно работать с двумя такими таблицами. Одна из них называется глобальной (GDT (global descriptor table)), а другая - локальной (LDT (local descriptor table)). В GDT собраны дескрипторы сегментов, разделяемых всеми задачами в системе, а в LDT располагаются дескрипторы сегментов, с которыми работает только данная задача. GDT в системе одна и всегда должна находиться в ОП, а LDT может быть столько же сколько и задач (для любой задачи LDT может быть создана, а может и не создаваться) и располагаться эти таблицы могут как в ОП, так и на диске.

Для того чтобы перейти к новому сегменту, надо обратиться к его дескриптору, то есть надо найти этот дескриптор в дескрипторной таблице. Для этого необходимо знать начальный адрес таблицы и внутритабличное смещение. Это смещение принято называть селектором дескриптора. Практически селектор представляет собой номер дескриптора в таблице. Начальные адреса таблиц процессору известны, они хранятся в специальных внутренних регистрах МП (gdtr и ldtr), а смещение берется из сегментного регистра. При этом любой сегментный регистр в МП имеет формат, приведенный на рис. 2.1 .

-

Видимая часть

Теневая часть

16 бит

64 бита

Видимая часть доступна программисту, а с теневой частью работает сам МП. Видимая часть имеет формат, приведенный на рис. 2.2.

-

15 3

2

1 0

селектор

TI

RPL

Здесь старшие 13 разрядов (биты 15 - 3) занимает селектор, определяющий местоположение дескриптора в одной из двух дескрипторных таблиц ( в какой именно задает бит TI (table indicator)). Биты 1 и 0 задают запрашиваемый уровень привилегий (RPL(requested privilege level)). Нетрудно видеть, что максимальное число дескрипторов в любой дескрипторной таблице 213 (поскольку селектор 13-ти разрядный), а максимальный размер таблицы равен 8×213 = 64К. А так как одновременно процессору доступны две такие таблицы то, как уже отмечалось выше, МП одновременно доступны 214 сегментов.

При обращению к новому сегменту в видимую часть сегментного регистра загружается новый селектор. По этому селектору в дескрипторной таблице МП находит дескриптор нового сегмента. Проверяются права доступа (и не только они) и, если они не нарушены, найденный дескриптор копируется (кэшируется) в теневую часть сегментного регистра (с тем чтобы в дальнейшем он был у МП «под рукой» и не требовалось каждый раз обращаться за ним в память). Например. Выполняется команда jmp 0008 : 00000002h. При этом 00000002h –это смещение в новом кодовом сегменте и эта величина будет загружена (если не нарушены права доступа и другие условия) в регистр eip. Величина 0008h представляет из себя селектор, ссылающийся на 1-й дескриптор в GDT (TI = 0, RPL = 0). Смотри рис. 44.

-

GDT

0-й дескриптор

1-й дескриптор

.

.

.

.

Рис. 44

Очевидно что таким способом (из-за проверки прав доступа) нельзя обратится к более привилегированному сегменту, поскольку при этом будет прерывание (нарушены права доступа). В то же время должна быть возможность обращения к привилегированным сегментам, хотя бы потому, что в противном случае задачам пользователя вообще будут недоступны средства ОС. Для предоставления такой возможности в системе создаются специальные структуры называемые шлюзами (вентилями) (gate).

Шлюз - структура, подобная дескриптору. Так же как и дескрипторы шлюзы занимают в памяти по 8-мь байт и располагаются в дескрипторных таблицах. Однако, если через дескриптор мы обращаемся к сегменту и при этом проверяется уровень привилегий, записанный в этом дескрипторе (см. рис. 45), то через шлюз мы обращаемся к дескриптору, на который ссылается этот шлюз (и далее через этот дескриптор к сегменту), при этом проверяется уровень привилегий, записанный в шлюзе, а уровень привилегий, записанный в дескрипторе, игнорируется (см. рис. 46). Здесь cpl (current privilege level)- текущий уровень привилегий задачи, dpl (descriptor privilege level) – уровень привилегий сегмента, записанный в его дескрипторе. Уровень привилегий, записанный в шлюзе (dpl шлюза), задает минимальный уровень привилегий, на котором разрешается «проход» через данный шлюз. Отметим также что проверки, приведенные на рис. 45 и рис. 46, для простоты картины показаны несколько упрощенно и даже не совсем корректно, более полно они будут рассмотрены позднее.

Обращаться через шлюзы можно только к исполняемым сегментам. К последним относятся сегменты кода и сегменты TSS.

Рис. 45

Рис. 46

Например, пусть выполняется программа с уровнем привилегий 3. В какой-то момент программа обращается к сегменту, в дескрипторе которого записан уровень привилегий 0. Попытка этого обращения окончится неудачно (прерыванием). Однако, если в системе есть шлюз, ссылающийся на этот дескриптор и имеющий уровень привилегий 3, и нашей программе известно его месторасположение в таблице она может обратиться к этому шлюзу. При этом права доступа для шлюза нарушены не будут и шлюз позволит программе обратиться к дескриптору. Права доступа дескриптора проверяться в этом случае не будут и программа получит доступ к сегменту с уровнем привилегий 0.

Шлюзы бывают четырех типов:

шлюз вызова. Может располагаться в таблицах GDT и LDT. Предназначен для вызова привилегированных подпрограмм.

шлюз задачи. Может располагаться в GDT, LDT и IDT (interrupt descriptor table) (дескрипторная таблица прерываний). Предназначен для переключения на привилегированную задачу.

шлюз прерываний. Может располагаться только в IDT. Служит для вызова обработчика внешнего прерывания. При переходе через этот шлюз флаг if сбрасывается в ноль, то есть запрещаются внешние прерывания.

шлюз ловушки. Может располагаться только в IDT. Служит для вызова обработчика внутреннего прерывания (особого случая). Практически аналогичен шлюзу прерываний, только внешние прерывания не запрещаются.

Некоторые сегменты кода могут быть отмечены как согласованные (подчиненные) (conforming). Если обычный сегмент кода всегда выполняется на том уровне привилегий, который записан в его дескрипторе, то согласованный сегмент кода выполняется на том уровне привилегий, с которого он был вызван. То есть уровень привилегий, записанный в дескрипторе согласованного сегмента в расчет не принимается и к такому сегменту можно обратиться с любого уровня привилегий. Здесь имеется одно исключение – ни к какому кодовому сегменту, в том числе и согласованному, нельзя обратиться с более высокого уровня привилегий !! Обычно в согласованных сегментах располагаются системные библиотеки. Большинство сегментов в системе, как правило, согласованными не являются.

Зачастую для одного и того же сегмента в системе создаются сразу несколько дескрипторов. Такие дескрипторы называют альтернативными (или псевдонимами) (alias). Например, пусть некоторый сегмент данных разделяется задачей пользователя и ОС. При этом ОС может менять данные в этом сегменте, а задача пользователя может только считывать информацию из этого сегмента. Для того чтобы такая организация была возможна придется создать два дескриптора этого сегмента. В одном сегменту будет присвоен 0-й уровень привилегий и этот сегмент будет описан как доступный для чтения/записи, в другом будет 3-й уровень привилегий и сегмент будет отмечен доступным только для чтения.