- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

Микропроцессор К1810ВМ86.

Зарубежный аналог этой микросхемы имеет обозначение i8086.

Данный микропроцессор (МП) относится к CISC типу. Он имеет 20 адресных линий (то есть может адресовать 220 =1 Мбайт ячеек ОП) и 16 линий данных. МП может работать в двух режимах: минимальном и максимальном.

Минимальный режим используется, когда на основе МП реализуется несложная однопроцес-сорная система. Для сложных однопроцессорных и многопроцессорных систем используется макси-мальный режим.

Сегментация памяти

Как уже отмечалось выше, МП 8086 имеет 20 адресных линий, то есть может адресовать ОП объемом 1 Мбайт. Эта память логическим образом разбивается на сегменты, объемом 64 Кбайт каж-дый, которые могут располагаться практически в любом месте памяти. Одновременно МП может ра-ботать с четырьмя такими сегментами. Они называются:

сегмент кода, в нем располагается программа, которую выполняет МП;

сегмент стека, в нем организуется стек;

сегмент данных, в нем располагаются данные;

дополнительный сегмент, обычно используется как дополнительный сегмент данных.

Каждому из этих сегментов ставится в соответствие находящийся внутри МП 16 разрядный сегментный регистр. Сегментный регистр cs соответствует сегменту кода, ss – стека, ds –данных и es – дополнительному сегменту.

Содержимое сегментного регистра задает начальный (базовый) адрес соответствующего сег-мента в ОП. Однако сегментный регистр 16 разрядный, а адрес ОП должен быть 20 разрядным. Чтобы из шестнадцати разрядов получить двадцать, содержимое сегментного регистра при формировании адреса ОП сдвигают на 4 разряда влево (умножают на 16). Например, пусть cs=2231h, тогда началь-ный адрес сегмента кода равен 22310h. Отсюда можно сделать вывод, что начальный адрес любого сегмента всегда кратен шестнадцати. Это единственное ограничение на расположение сегментов в памяти. Других ограничений не существует, то есть сегменты могут быть полностью независимы друг от друга, а могут частично и даже полностью перекрываться.

При выполнении команды, если в ней требуется обращение к памяти, МП формирует по адрес-ному коду, заданному в команде, так называемый эффективный адрес (Аэф).

Например, пусть

ds=2200h, bx=1000h, si=0770h

и выполняется команда

mov ax,[bx+si+2]

тогда

Аэф=(bx)+(si)+2=1000h+0770h+2=1772h

Сформированный Аэф рассматривается как внутрисегментное смещение, поэтому далее МП формирует физический адрес (Аф) по следующей формуле:

Аф = (сегментный регистр)×16 + Аэф.

Аф и является адресом ячейки ОП, к которой обращается МП. Для нашего примера (по умол-чанию здесь в качестве сегментного регистра берется сегментный регистр ds):

Аф = (ds)×16 + Аэф = 22000h + 1772h = 23772h.

В процессе формирования Аэф возможно возникновение переноса из старшего разряда. При этом данный перенос попросту отбрасывается. Таким образом, после Аэф = ffffh идет Аэф = 0000h. Иначе говоря, достигнув конца сегмента мы автоматически переходим на его начало. Это так назы-ваемая кольцевая организация сегмента. Таким образом, существует только один способ выйти за пределы текущего сегмента – сменить содержимое соответствующего сегментного регистра.

В процессе формирования Аф также возможно возникновение переноса из старшего разряда. Как и в предыдущем случае, этот перенос попросту отбрасывается, Получается кольцевая организа-ция памяти. Иначе говоря, никаким способом мы не можем сформировать адрес за пределами 1 Мбайта.

Организация оперативной памяти

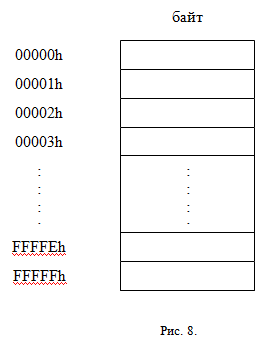

С точки зрения программиста оперативная память для ВМ86 представляет собой линейный массив ячеек форматом 1 байт каждая, с адресами от 00000h до fffffh (рис. 8).

Информация, располагаемая в ОП, может иметь следующие форматы:

байт;

слово (2 байта);

двойное слово (4 байта).

При этом адресом слова или двойного слова считается адрес его младшего байта.

Физически память для МП86 организуется иначе. Память реализуется в виде 2-х банков: стар-шего и младшего. В младший банк входят все ячейки с четными адресами, в старший – все ячейки с нечетными адресами. Обращение к тому или иному банку (или к обоим сразу) определяется комбина-цией сигналов на выходах BHE и A0 МП. Подключение банков к шине данных показано на рис. 9.

Банк подключается к ШД, когда на его вход CS приходит активный (нулевой) сигнал. При этом младший банк подключается к младшей половине ШД, а старший – к старшей половине ШД. Такая организация позволяет производить обмен между МП и ОП как по всей ШД, так и по отдельным ее половинам. Подобная архитектура приводит к следующему правилу: слова желательно располагать в памяти по четным адресам. Если слово располагается в ОП по четному адресу, то оно будет передаваться по ШД за один цикл шины, если же по нечетному – за два цикла шины. По той же причине двойные слова также желательно располагать по четным адресам.