- •Билет №1 Структура эвм общего назначения. Алу, уу

- •Арифметико-логические устройства.

- •Устройства управления.

- •Описание сегментного механизма

- •Билет №2 Структура эвм общего назначения. Risc и cisc процессоры. Форматы машинных команд.

- •Risc и cisc процессоры.

- •Форматы машинных команд.

- •Описание страничного механизма.

- •Билет №3 Структура эвм общего назначения. Способы адресации. Стековая адресация. Виды стеков.

- •Способы адресации.

- •Стековая адресация. Виды стеков.

- •Особенности страничного механизма в Pentium и в р6.

- •Билет №4 Микропроцессор вм86. Назначение входов/выходов вм86 в минимальном/максимальном режиме.

- •Назначение входов/выходов вм86 в максимальном режиме.

- •Общие сведения о механизмах адресации в защищенном режиме.

- •Билет №5 Внутренняя архитектура мп вм86. Программная модель мп вм86.

- •Программная модель мп вм86.

- •Форматы системных таблиц защищенного режима. Системные таблицы

- •Билет №6 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Tss, ldt, gdt. Селектор,дескриптор. Билет №7 мп вм86. Организация адресного пространства портов ву.

- •Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, Режимы работы 32 разрядного процессора.

- •Билет №8 Программируемый адаптер к1810вв55 (i8255)

- •Битовая карта ввода вывода

- •Билет 9 Программируемый таймер к1810ви54 (i8254)

- •Механизм перехода в защищенном режиме

- •Билет №10 Общие сведения об обработке прерываний.

- •Формат машинной команды 32х разрядного процессора.

- •Билет №11 Система прерываний вм86.

- •Внутренняя кэш-память.

- •Билет №12 Контроллер прерываний к1810вн59 (i8259). Настройка вн59.

- •Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение).

- •Билет №13 Общие сведения о прямом доступе к памяти.

- •Буфер tlb. Кэш-память страниц.

- •Билет 14 Контроллер прямого доступа к памяти к1810вт37 (i8237).

- •Программирование кпдп вт37

- •Вопрос №2

- •Билет 15

- •1. Организация процессорного модуля вм86.

- •2.21 Организация процессорного модуля вм86.

- •Программная модель 32-разрядного мп.

- •Программная модель 32 разрядного мп

- •Билет 16 Слабосвязанная конфигурация.

- •2.23. Слабо связанные конфигурации.

- •Форматы таблиц gdt, ldt и idt.

- •3.4. Системные таблицы

- •Билет 17 Арбитр шин к1810вб89 (i8289).

- •2.24. Арбитр шин к1810вб89 (i8289).

- •Формат дескриптора.

- •3.15 Формат дескриптора.

- •Билет №18 Сильно связанные конфигурации на примере совместной работы мп86 и арифметического сопроцессора вм87.

- •Форматы элементов pte и pde.

- •3.8. Формат элемента pte (pde).

- •Билет №19 Формат машинных команд мп вм86.

- •Механизм переключения задач. Формат сегмента tss

- •Билет №20 мп вм86. Сегментация памяти. Организация оперативной памяти.

- •Сегментация памяти.

- •2.7 Организация оперативной памяти.

- •Общие сведения о кэш-памяти.

- •Внутренняя кэш-память

- •Сведения о кэшах в процессорах фирмы Intel.

Оглавление

Билет №1 5

Структура ЭВМ общего назначения. АЛУ, УУ 5

Арифметико-логические устройства. 5

Устройства управления. 6

Типичная структура микропрограммного УУ приведена на рис. 2 6

Описание сегментного механизма 8

DPL >= max { CPL, RPL }. 8

DPL = max { CPL, RPL }. 8

Билет №2 10

Структура ЭВМ общего назначения. RISC и CISC процессоры. Форматы машинных команд. 10

RISC и CISC процессоры. 11

Форматы машинных команд. 12

Описание страничного механизма. 12

Билет №3 15

Структура ЭВМ общего назначения. Способы адресации. Стековая адресация. Виды стеков. 15

Способы адресации. 16

Стековая адресация. Виды стеков. 16

Особенности страничного механизма в Pentium и в Р6. 16

Билет №4 17

Микропроцессор ВМ86. Назначение входов/выходов ВМ86 в минимальном/максимальном режиме. 17

Микропроцессор К1810ВМ86. 17

Назначение входов/выходов ВМ86 в минимальном режиме. 17

Назначение входов/выходов ВМ86 в максимальном режиме. 20

Общие сведения о механизмах адресации в защищенном режиме. 21

Аф = начальный адрес сегмента + Аэф. 22

Билет №5 23

Внутренняя архитектура МП ВМ86. Программная модель МП ВМ86. 23

Форматы системных таблиц защищенного режима. 29

Рис. 48 30

Билет №6 32

МП ВМ86. Сегментация памяти. Организация оперативной памяти. 32

Микропроцессор К1810ВМ86. 32

Сегментация памяти 33

Например, пусть 33

Аэф=(bx)+(si)+2=1000h+0770h+2=1772h 33

Аф = (сегментный регистр)×16 + Аэф. 33

Аф = (ds)×16 + Аэф = 22000h + 1772h = 23772h. 33

Организация оперативной памяти 33

Общие сведения о 32х разрядных процессорах фирмы Intel. TSS, LDT, GDT. Селектор,дескриптор. 34

Билет №7 34

МП ВМ86. Организация адресного пространства портов ВУ. 34

Микропроцессор К1810ВМ86. 34

Организация адресного пространства портов ВУ 34

Общие сведения о 32х разрядных процессорах фирмы Intel. Режимы работы, 35

Режимы работы 32 разрядного процессора. 35

Аф = (sr)×16 + Аэф. 35

Аф = начальный адрес сегмента + Аэф. 36

Рис. 44 38

Рис. 45 39

Рис. 46 39

Билет №8 40

Программируемый адаптер К1810ВВ55 (i8255) 40

Битовая карта ввода вывода 42

Рис. 61 43

Билет 9 43

Программируемый таймер К1810ВИ54 (i8254) 43

Механизм перехода в защищенном режиме 45

Аф = начальный адрес сегмента + Аэф. 46

Рис. 2.1 46

Рис. 2.2 47

Билет №10 47

Общие сведения об обработке прерываний. 47

Формат машинной команды 32х разрядного процессора. 48

Билет №11 52

Система прерываний ВМ86. 52

Внутренняя КЭШ-память. 54

Билет №12 55

Контроллер прерываний К1810ВН59 (i8259). Настройка ВН59. 55

Сведения о внутренней организации 32-х разрядных процессорах, (состав, назначение). 57

Билет №13 60

Общие сведения о прямом доступе к памяти. 60

Буфер TLB. Кэш-память страниц. 60

Билет 14 62

Контроллер прямого доступа к памяти К1810ВТ37 (i8237). 62

Начиная с PC/AT, в системе стоят два ВТ37, соединенных каскадно. 65

Рис. 27 65

Рис. 28 65

Вопрос №2 66

Билет 15 67

1. Организация процессорного модуля ВМ86. 67

Рис. 29 68

READY = AEN1&RDY1 AEN2&RDY2. 68

Рис 30. 72

Рис. 31 73

Программная модель 32-разрядного МП. 73

Рис. 69 75

Рис. 70 75

Билет 16 76

Слабосвязанная конфигурация. 76

Рис 35 78

Форматы таблиц GDT, LDT и IDT. 79

Рис. 48 79

Рис. 49 81

Билет 17 82

Арбитр шин К1810ВБ89 (i8289). 82

Рис. 36 84

Рис. 37 85

Формат дескриптора. 87

Рис. 62 87

Рис. 63 88

Рис. 64 89

Рис. 65 89

Билет №18 90

Сильно связанные конфигурации на примере совместной работы МП86 и арифметического сопроцессора ВМ87. 90

Форматы элементов PTE и PDE. 92

Рис. 54 92

Билет №19 93

Формат машинных команд МП ВМ86. 93

Механизм переключения задач. Формат сегмента TSS 95

Билет №20 99

МП ВМ86. Сегментация памяти. Организация оперативной памяти. 99

Общие сведения о КЭШ-памяти. 101

Билет №1 Структура эвм общего назначения. Алу, уу

Любая ЭВМ содержит два основных блока:

центральный процессор (ЦП);

оперативную память (ОП).

Задачей ЦП является выполнение машинных команд, которые он выбирает из ОП. Внутренняя организация различных ЦП может серьезно отличаться друг от друга, однако любой ЦП содержит ряд стандартных блоков. К ним относятся:

дешифратор команд, позволяющий декодировать считанную из ОП команду;

арифметико-логическое устройство (АЛУ), позволяющее реализовать заданную в команде операцию;

блок регистров общего назначения (блок РОН), предназначенных для временного хранения информации. Наличие РОН позволяет резко снизить количество обращений к ОП, повышая тем самым общее быстродействие ЭВМ;

устройство управления (УУ), обеспечивающее на всех этапах выполнения команды выра-ботку необходимых управляющих сигналов.

Оперативная память состоит из ПЗУ и ОЗУ и предназначена для хранения программ, исходных данных, а также промежуточных и конечных результатов вычислений.

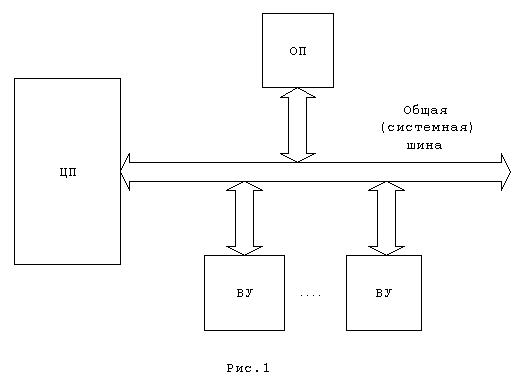

Обычно ЭВМ общего назначения организуется по так называемой схеме с общей шиной (рис. 1).

Здесь ВУ – внешнее устройство.

Системная шина (СШ) в свою очередь подразделяется на шину адреса (ША), шину данных (ШД) и шину управления (ШУ). На ША процессор выставляет адреса ячеек памяти и портов внешних устройств, к которым он обращается. На шине управления процессор формирует сигналы, управ-ляющие передачей информации. Сама передача информации производится по ШД.

В любой конкретный момент времени к СШ может быть подключено не более двух устройств. Одно из этих устройств передает информацию, другое ее принимает. Как правило, одним из этих уст-ройств является ЦП, который и управляет передачей информации по шине. Исключением является режим прямого доступа к памяти, когда ЦП в обмене участия не принимает, а управление обменом берет на себя стоящий в системе контроллер прямого доступа к памяти.

Арифметико-логические устройства.

АЛУ выполняет операции по преобразованию поступающей в него информации. В машинах малой и средней мощности, не имеющих отдельного блока для формирования физических адресов ОП, на АЛУ также возлагаются операции адресной арифметики.

Алгоритмы операций, выполняемых на АЛУ, включают определенную последовательность элементарных действий (микроопераций), среди которых различают прием кода операнда, преобра-зование этого кода, суммирование кодов двух операндов, сдвиг кода, логические операции над кода-ми и ряд других.

Для выполнения этих действий в АЛУ в общем случае включаются следующие функциональ-ные узлы:

регистры для временного хранения операндов;

сдвигатели;

преобразователи прямого кода в дополнительный и обратно;

сумматор, на котором реализуются арифметические и логические операции.

Существует много различных типов АЛУ. Например, по системам счисления различают АЛУ с двоичной и десятичной арифметикой, по формам представления числовых данных–АЛУ с фиксиро-ванной и плавающей запятой и. т. д. Более подробные сведения о типах и структурах АЛУ рекомен-дуется искать в соответствующей литературе.