- •Введение

- •1. Светодиодные индикаторы

- •1.1. Бинарные индикаторы

- •1.2. Статические цифровые индикаторы

- •1.3. Устройства динамической индикации

- •1.4. Варианты заданий для курсового проекта

- •2. Краткие справочные данные

- •2.1. Интегральные компоненты серии кр1533

- •2.2. Семисегментные полупроводниковые индикаторы

- •Список использованных источников

- •Приложение

1.3. Устройства динамической индикации

При построении многоразрядных индикаторов на основе выше приведенных схем каждая цифра обслуживается автономным дешифратором сегментов. Количество дешифраторов в схеме равно количеству отображаемых символов. Число соединительных линий информационного канала равно произведению 7хN, где N – число отображаемых символов (количество индикаторов). Для сокращения количества дешифраторов и соединительных линий используются устройства динамической индикации. На рис. 1.10 приведена схема мультиплексного индикатора.

Устройство динамической индикации мультиплексного типа

Рис. 1.10

32-х разрядный двоичный либо двоично-десятичный код формируется на информационных входах мультиплексоров (MX) таким образом, что первая тетрада присутствует на первых входах, вторая – на вторых, третья на третьих и т.д. Двоичный счетчик (СТ2) одновременно управляет мультиплексорами и дешифратором, выходы которого соединены с транзисторными ключами. Транзисторные ключи на рис. 1.10 изображены условно без соответствующих резисторов, обеспечивающих ключевой режим работы транзисторов. Кроме этого, при схемотехнической реализации для надежного обеспечения ключевого режима нагрузку (индикаторы) предпочтительнее включать в коллекторную цепь транзисторов. Питание в схеме за счет циклической работы счетчика одновременно подается только на один из индикаторов. В первом такте работы это индикатор HL1. Информационный сигнал, декодируемый дешифратором сегментов, соответствует первой информационной тетраде. Во втором такте работы счетчика питание подается через ключ VT2 (на схеме не показан) на второй индикатор. Число, отображаемое вторым индикатором, соответствует второй информационной тетраде. При быстром переключении разрядов свечение воспринимается как непрерывное вследствие инерционности восприятия изображения человеческим глазом. При частоте переключения выше 60 Гц циклическая смена изображения не воспринимается глазом человека. Время свечения каждого индикатора определяется скважностью , которая равна отношению суммарного времени свечения всех индикаторов к времени свечения одного индикатора. В рассмотренном варианте =8/1=8. Численное значение скважности необходимо для корректировки номинальных значений токоограничивающих резисторов для индикаторов с общими анодами, так как среднее значение тока через отдельный светодиод уменьшается в раз. Следует иметь в виду, что увеличение скважности снижает общую яркость свечения, поэтому, в реальных схемах динамической индикации количество разрядов индикатора ограничивается величиной 10-12.

Расчет транзисторного ключа может быть выполнен по следующей упрощенной методике. При включении нагрузки в цепь коллектора рассчитывается ток коллектора (IК), как сумма токов сегментов индикатора. По известному току коллектора и величине +Е выбирается транзистор. За величину коэффициента усиления (h21) принимается минимальное значение, приведенное в справочных данных. Ток базы транзисторного ключа определяется как IБ = IК/. Расчетное значение увеличивается в 5-10 раз для гарантированного обеспечения ключевого режима. По известному значению напряжения на выходе дешифратора и полученной величине тока базы определяется расчетное сопротивление резистора в цепи базы транзисторного ключа: RБ = UDC/IБ. Следует учитывать, что слишком большой ток базы вызывает режим глубокого насыщения транзистора и увеличивает время его закрытия. Увеличение времени закрытия приводит к явлению «послесвечения» и снижению качества отображения информации.

Принцип динамической индикации, описание которого приведено выше, широко используется в микропроцессорных системах различного типа. При этом отпадает необходимость мультиплексирования индицируемых данных, так как указанная процедура осуществляется программными средствами.

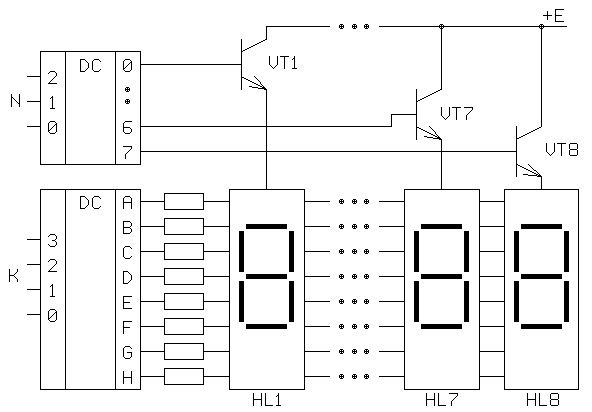

Варианты реализации устройств динамической индикации в составе микропроцессорных систем зависят от количества свободных разрядов портов вывода информации. Схема устройства с минимальным количеством информационных линий для восьмиразрядного индикатора показана на рис. 1.11.

Устройство динамической индикации для микропроцессорной системы

Рис. 1.11

В представленной схеме двоичные коды N и K формируются программным способом. При этом кодом N определяется номер индикатора, а кодом К – цифра или символ, отображаемый на этом индикаторе. Аналогично мультиплексному индикатору частота изменения кодов должна быть выше 60 Гц. Так как коды, поступающие на входы устройства индикации, формируются программным способом, появляется возможность улучшения качества отображения, например, за счет гашения незначащих нулей и т.п. В приведенной конфигурации количество информационных линий для обслуживания индикатора минимально за счет аппаратной дешифрации кодов отображаемого символа и его позиции в разрядной сетке.

Программное выполнение функций дешифрации увеличивает количество информационных линий (для схемы восьмиразрядного индикатора это число равно 16), но позволяет не использовать дешифраторы. Вместо дешифраторов в схему устройства могут быть включены буферные схемы или регистры, если штатные средства коммуникации микропроцессорных систем не позволяют выполнить непосредственное подключение к транзисторным ключам и объединенным сегментным выводам элементов индикации.

Число разрядов подобного индикатора также ограничивается на уровне 10-12 вследствие роста скважности .

Вариантом схемы с константным значением является устройство динамической индикации методом досчета (рис. 1.12).

Схема содержит группу вычитающих счетчиков с входами задания и записи параллельного кода. Выходы естественного обнуления названных счетчиков подключены к входам управления транзисторных ключей. Дешифратор сегментов управляется сигналами с выходов суммирующего счетчика. Коды индицируемых десятичных цифр К1,К2, … Кn-1,Кn (все счетчики двоично-десятичные) присутствуют на входах задания начального кода счетчиков соответствующих разрядов. После записи Кi импульсом с выхода естественного переполнения суммирующего счетчика каждый из разрядных счетчиков содержит индицируемую цифру в двоично-десятичном формате. В момент естественного обнуления каждого из названных счетчиков открывается транзисторный ключ соответствующего разряда.

Динамическая индикация методом досчета

Рис. 1.12

Так как вычитающие счетчики и суммирующий работают синхронно, то в момент обнуления вычитающего на выходах суммирующего счетчика код равен начальному коду вычитающего счетчика. Следовательно, на соответствующем разрядном индикаторе высвечивается требуемая цифра. Скважность в приведенной схеме постоянна и равна количеству отображаемых символов (в приведенном примере – 10).

При проектировании реальных устройств на основании изложенного принципа динамической индикации необходимо учитывать, что при равенстве кодов вычитающих счетчиков (индицируемые цифры одинаковы) все индикаторы включаются одновременно. Следовательно, нагрузочная способность сегментного дешифратора должна быть увеличена, например, могут быть применены промежуточные эмиттерные повторители или интегральные буферные элементы с повышенной нагрузочной способностью.