- •Курсовой проект.

- •«Обработка сигналов в микропроцессорной среде»

- •Построение амплитудно-частотной характеристики(ачх и фчх) передаточной функции фильтра, средствами пакета MathCad, для заданных значений сопротивлений, емкостей и индуктивностей.

- •Архитектура микроконтроллера aTmega8535.

- •Архитектура ядра микроконтроллера aTmega8535.

- •Цоколевка микроконтроллера aTmega8535.

- •Структурная схема микроконтроллера aTmega8535.

- •Работа с портами ввода-вывода.

- •Если какая-то линия порта ввода-вывода в схеме не используется, она должна быть определена как вход (соответствующий бит регистра ddRn должен быть равен нулю).

- •Программирование в среде CodeVision avr.

- •Решение системы по разностной схеме.

- •Результаты решения системы.

- •Проверка адекватности решений.

- •Блок схема алгоритма работы программы.

- •Выводы.

- •Список литературы.

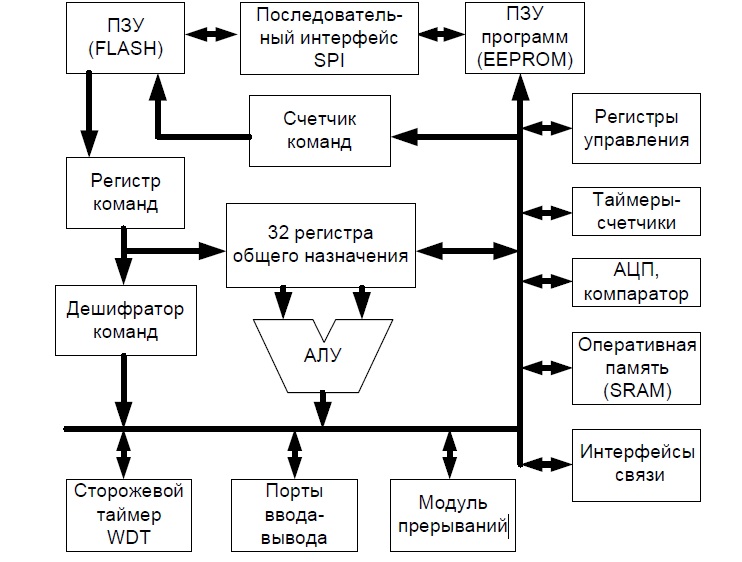

Архитектура ядра микроконтроллера aTmega8535.

Ядро микроконтроллера AVR семейства Mega выполнено по усовершенствованной RISC-архитектуре (enhanced RISC) (рис.7.), в которой используется ряд решений, направленных на повышение быстродействия микроконтроллеров.

Арифметико-логического устройство (АЛУ), выполняющие вычисления, подключено непосредственно к 32 рабочим регистрам, объединенным в регистровый файл. Благодаря этому, АЛУ может выполнять одну операцию (чтение содержимого регистров, выполнение операций и запись результата обратно в регистровый файл) за такт. Кроме того, практически каждая из команд (за исключением команд, у которых одним из операндов является 16-битный адрес), занимает одну ячейку памяти программ.

Рис.7. Упрощенная архитектура ядра микроконтроллера ATmega

В микроконтроллерах AVR реализована Гарвардская архитектура, характеризующаяся раздельной памятью программ и данных, каждая из которых имеет собственные шины доступа. Такая организация позволяет одновременно работать как с памятью программ, так и с памятью данных. Разделение информационных шин позволяет использовать для каждого типа памяти шины различной разрядности, причем способы адресации и доступа к каждому типу памяти также различаются. В сочетании с двухуровневым конвейером команд такая архитектура позволяет достичь производительности в 1 MIPS на каждый 1 МГц тактовой частоты.

Арифметико-логическое устройство (АЛУ) поддерживает арифметические и логические операции с операндами в виде двух регистров, либо регистры и константы. Большинство команд процессора выполняются за 1 такт, равный 1 периоду изменения тактового сигнала.

Указатель исполняемой команды хранится в программном счетчике и автоматически изменяет своё значение при переходе на следующую команду. Команды процессора выполняются последовательно, в порядке их следования в программе. При выполнении команд передачи управления (условный или безусловный переход, вызов программы, прерывание) счетчик команд автоматически изменяет свое значение, указывая на новый адрес исполняемой команды. Во время прерывания или вызова подпрограммы адрес возврата в вызывающую (основную) программу сохраняется в стеке. Размер стека ограничен размером оперативной памяти.

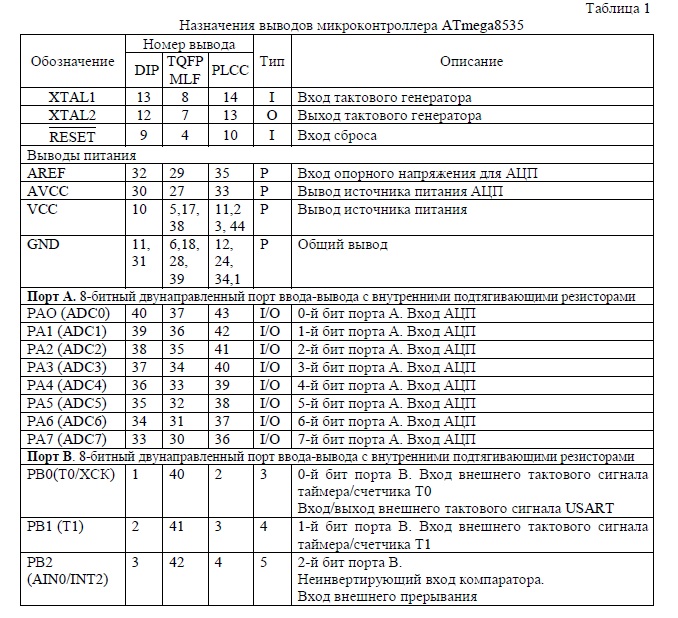

Цоколевка микроконтроллера aTmega8535.

Микроконтроллеры ATmega8535 выпускаются в 44-выводных корпусах типа TQFP, MLF, PLCC, а так же в 40-выводных корпусах типа DIP с числом контактов ввода-вывода, равным 32.

Цоколевка микросхемы ATmega8535 приведена на рис.8, назначения выводов – табл.1, где использованы следующие обозначения:

I – вход; O – выход; I/O – вход/выход; P – вывод питания.

Если

микросхема имеет неподключенные выводы

(NC), подключать их

к какому-либо уровню напряжения не

рекомендуется.

Рис.8. Цоколевка микроконтроллера ATmega8535

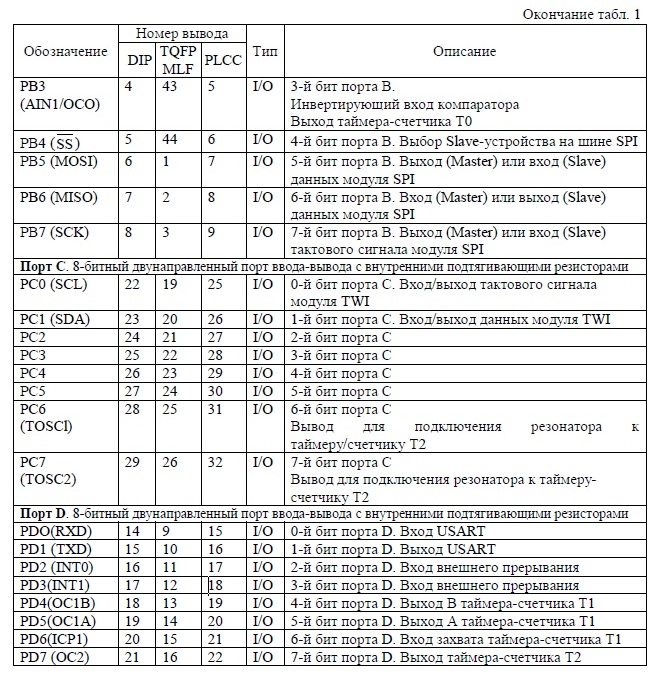

Структурная схема микроконтроллера aTmega8535.

Структурная схема микроконтроллера ATmega8535 представлена на рис.9.

Рис.9. Структурная схема микроконтроллераATmega8535