- •Змістовий модуль III

- •3. Чому на низьких (звукових) частотах краще застосовувати rc- автогенератори?

- •11. Яким процесом визначається час перебування одного з транзисторів (наприклад, vt1) в закритому стані? Оцініть цей час.

- •14. Чим можна пояснити невеликий позитивний заряд напруги uб, який з’являється в момент відкривання транзистора? Чим визначається тривалість цього викиду?

- •15. Чи зможе мультивібратор працювати, якщо не буде виконуватись умова насичення відкритого транзистора?

- •21. Чому схема симетричного тригера не може перебувати в симетричному режимі?

- •22. Чи може функціонувати тригер, якщо його відкритий транзистор не перебуватиме в режимі насичення?

- •23. Чому для побудови тригера бажано застосувати кремнієві, а не германієві транзистори?

- •Для чого у тригері рекомендується шунтувати опір зв’язку r1 невеликою ємністю?

- •25. Чому для керування тригером краще подавати позитивний імпульс на базу закритого транзистора, а не негативний - на базу відкритого?

- •26. Поясніть, чому тригер називають елементом електронної пам’яті.

- •27. Чому тригер Шмідта називають бістабільним?

- •28. З якою метою застосовують тригери Шмідта?

- •Змістовий модуль IV

- •1. В чому полягають принципи аналогового та цифрового подання інформації?

- •2. Наведіть приклади аналогового та цифрового зображення величин. Проаналізуйте переваги та недоліки кожного.

- •3. Детально опишіть алгоритм переходу від аналогової форми подання інформації до цифрової.

- •4. Що таке дискретизація за часом? Сформулюйте теорему Котельникова.

- •5. В чому суть квантування аналогового сигналу? Що собою являють шуми квантування і чому вони виникають?

- •6. В чому полягає кодування інформації?

- •7. Що таке дворівневий код та як відбувається зображення інформації у вигляді двійкових чисел?

- •8. Проаналізуйте переваги та недоліки цифрової форми подання інформації.

- •9. Які системи числення ви знаєте? Наведіть їхню порівняльну характеристику.

- •10. Що таке цифровий ключ? Детально опишіть роботу біполярного насиченого ключа.

- •11. Як працюють цифрові ключі на мдн—транзисторах?

- •12. Що є фізичною причиною існування інерційності цифрових ключів? Які способи зменшення інерційності цифрових ключів ви знаєте?

- •13. Що таке логічні елементи?

- •14.В чому полягає суть операцій повторення та інверсії? Наведіть приклади реальних схем.

- •15. В чому полягає суть операції диз’юнкції? Наведіть приклади реальних схем.

- •16. В чому полягає суть операції кон’юнкції? Наведіть приклади реальних схем.

- •17. В чому полягає суть операції “або—не”? Наведіть приклади реальних схем.

- •18. В чому полягає суть операції “і—не”? Наведіть приклади реальних схем.

- •19. В чому полягає суть операцій рівнозначність та нерівнозначність? Наведіть приклади реальних схем.

- •20. Що таке логічні елементи з трьома вихідними станами? Для чого вони використовуються?

- •21. Що таке логічні інтегральні мікросхеми? Наведіть приклад функціонально повної системи логічних елементів.

- •22. Що таке суматор? Опишіть принцип дії суматора використовуючи поняття про доповняльний код.

- •23. Що таке дешифратор? Як він працює? Де використовується?

- •24. Що таке селектор? Як він працює? Де використовується?

- •25. Що таке мультиплексор? Опишіть принцип його дії.

- •26. Формувачі імпульсів: класифікація та принципи дії.

- •27. Запам’ятовуючі пристрої. Наведіть загальні характеристики запам’ятовуючих пристроїв та їхню класифікацію.

- •28. Що таке тригери? Де вони використовуються? Наведіть приклади.

- •29. Що таке регістр? Які типи регістрів ви знаєте? Наведіть приклади.

- •30. Що таке лічильник? Де вони застосовуються. Наведіть приклади.

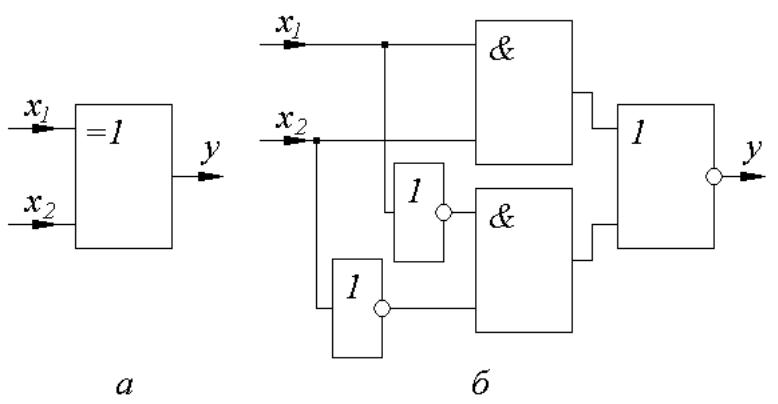

19. В чому полягає суть операцій рівнозначність та нерівнозначність? Наведіть приклади реальних схем.

Операція

“РІВНОЗНАЧНІСТЬ”: y =

Ця операція має таку назву тому, що

вихідна

Ця операція має таку назву тому, що

вихідна

функція у набуває значення логічної одиниці тоді і тільки тоді, коли усі аргументи одночасно дорівнюють нулям чи одиницям. Таблиця істинності для цієї функції:

|

|

y |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Операція

“НЕРІВНОЗНАЧНІСТЬ”:

y= . Операція нерівнозначність

є звичайною інверсією операції

рівнозначність

. Операція нерівнозначність

є звичайною інверсією операції

рівнозначність

|

|

y |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Тут вихідний сигнал рівний логічній одиниці лише тоді, коли значення аргументів протилежні один одному. Умовне позначення логічного елементу, що реалізує операцію нерівнозначність

наведено на рис. 8, а. Спосіб побудови електричних схем, здатних реалізовувати операції рівнозначність та нерівно- значність, випливає з наведених вище формул. Схема, яка виконує операцію нерівнозначність, наведена на рис.8, б. Ця схема має одну важливу властивість: вона є

узагальненим логічним елементом по відношенню до аргументу х2, функціональність якого визначається значенням аргументу х1. Дійсно, якщо х1=“0”, то по відношенню до х2 маємо повторювач, а за умови х1=“1” – інвертор.

Рис.8

Рис.8

Принцип керування функціональністю цифрових електричних схем за допомогою керуючих електричних сигналів лежить в основі усієї цифрової схемотехніки і саме на ньому базується робота усіх сучасних ЕОМ.

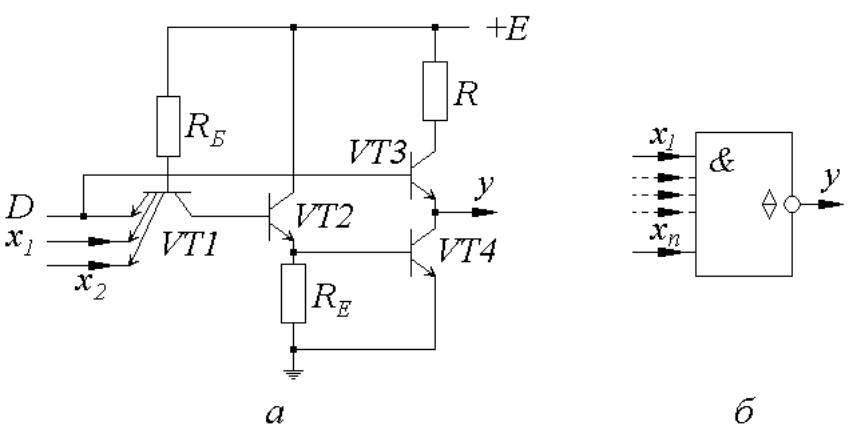

20. Що таке логічні елементи з трьома вихідними станами? Для чого вони використовуються?

Усі розглянуті вище логічні елементи (повторення, заперечення, диз’юнкція, кон’юнкція, рівнозначність, нерівнозначність, або-не, і-не) мають на виході два логічні стани: логічний нуль та логічну одиницю. У кожному з цих станів їхній вихідний опір невеликий. У складних цифрових системах виходи великої кількості логічних елементів паралельно з’єднуються з загальною шиною. З них у кожен момент часу працює лише один логічний елемент, а інші не використовуються, проте своїми вихідними опорами шунтують вихід працюючого логічного елементу і заважають йому. Тому виходи усіх логічних елементів, які в даний момент не використовуються, переводять у так званий третій стан з високим вихідним опором.

Для цього у схемі логічного елементу передбачають дозволяючий вхід D. У випадку, коли D=“1”, вихід цього елементу відкривається і сам елемент з’єднується із загальною шиною.

Спрощена схема логічного лементу “І-НЕ” з третім станом на виході зображена на рис. а , а його умовне позначення – на рис. б. Коли D=“0”, то транзистори VT2, VT3 та VT4 – закриті, і вихід логічного елементу відрізано від шини. Коли ж D=“1”, транзистор VT4 – відкритий, і схема керується сигналами на інформаційних входах хі.

21. Що таке логічні інтегральні мікросхеми? Наведіть приклад функціонально повної системи логічних елементів.

У наш час логічні схеми виготовляють в інтегральному виконанні у вигляді мікросхем (ІМС). Переважно випускають універсальні ІМС типу “І-НЕ” чи “АБО-НЕ” з кількома входами. Відповідним комбінуванням з них можна виготовити пристрої, що реалізовуватимуть інші логічні операції. Схеми, у яких використовують самі лише транзистори, мають назву схем з транзисторно-транзисторною логікою (ТТЛ). Якщо ж використовують транзистори разом з діодами Шотткі чи транзистори Шотткі – ТТЛШ. Логічні елементи, у яких усі транзистори зв’язані загальним емітерним опором RE побудовані за так званою емітерно-зв’язаною логікою. Нарешті схеми, побудовані з використанням комплементарних пар МОН-транзисторів називають КМОН-логікою. В ІМС ТТЛ або ТТЛШ витрати потужності на один логічний елемент становлять кілька десятків мВт, а у КМОН-логіки – 1 мВт і менше. Логічні інтегральні мікросхеми можна охарактеризувати такими параметрами:

коефіцієнт об’єднання за входом – він визначає максимально можливу кількість входів однієї ІМС. Для ТТЛ схем він становить близько 10;

коефіцієнт розгалуження за виходом – він визначає максимальну кількість входів ІМС, якими може керувати вихід даної мікросхеми. Для ТТЛ він становить 10, а для КМОН – 50.

Усім логічним елементам притаманна певна інерційність, зумовлена інерційністю як самих транзисторів, так і схемотехнічними факторами. За ступенем інерційності логічні елементи та схеми поділяють на:

низько швидкодіючі, кілька сотень нс на 1 елемент;

середньо швидкодіючі, кілька десятків нс на 1 елемент;

високо швидкодіючі, менше за 10 нс на 1 елемент.

Інерційність логічних мікросхем є дуже важливим параметром, оскільки вона визначає швидкість роботи усіх тих пристроїв, де ці мікросхеми використовуються.

Інтегральні мікросхеми розробляються та випускаються серіями. Серія – це сукупність мікросхем, які виконують різні функції, але мають єдине конструктивно-технологічне виконання та призначені для спільного використання. Як правило, на базі такої серії повинна повністю забезпечуватися можливість розробки пристроїв певного класу, які відповідають заданим умовам. Конструктивне виконання усіх мікросхем серії однотипне, вони виготовляються у однакових корпусах, розташування зовнішніх однойменних виводів однакове, значення напруги живлення та рівнів логічного нуля U(H) та логічної одиниці U(B) зберігаються однаковими. Технологія виготовлення мікросхем однієї серії також однакова. Основою кожної серії ІМС є базовий елемент. Як правило, це універсальний логічний елемент типу “І-НЕ” чи “АБО-НЕ”, на базі якого можна здійснювати будь-які логічні операції, а також будувати елементи електронної пам’яті. Таким чином, кожна логічна ІМС, незалежно від її складності та призначення, є кристалом, на якому багаторазово повторено базовий елемент даної серії. Функціональність кожної окремої ІМС визначається відповідним з’єднанням цих базових елементів.