- •Кдп Данные

- •Адрес Ячейки зу

- •Интерфейс

- •Блок регистров.

- •Арифметическо-логическое устройство.

- •Формат команд

- •Команды передачи данных

- •00 110 110 00 000 001 - 1 Загружается в ячейку памяти,адрес которой записан в паре регистров h,l.

- •4.Stax, ldax - передача данных между регистрами а и ячейками памяти, адрес которых хранится- в паре регистров вс,de.

- •Формат команды: 00 ddd 101

- •1.1 Понятие о микропроцессорной системе управления.

- •2. Цикл проектирования системы.

- •3. Требования пользователей и функциональная спецификация.

- •4. Проектирование системы.

Двоичная арифметика.

Системы счисления:

1. Непозиционная.

Римская, пример: IV, VI.

Каждая цифра не меняет своего веса в зависимости от положения в числе. Вес всего числа определяется с помощью арифметических действий.

2. Позиционная.

Арабская, например 753, 357.

Число определяется сложением отдельных весов цифр, но цифра меняет свой вес в зависимости от позиции в числе.

![]()

S – основание системы счисления;

A – весовой коэффициент цифры;

n - номер

Пример: 999=900+90+9

К позиционным системам счисления относятся также: двоичная, четверичная, восьмеричная, шестнадцатеричная. По формулам можно перевести из одной системы счисления в другую:

101101110(2) = 1*28 + 0*27 + 26 + 25 + 23 + 22 + 21 =

= 256 + 64 + 32 + 8 + 4 + 2 = 366(10)

или:

3 66

2

66

2

-

366 183 2

0 1 91 2

1 45 2

1 22 2

1 22 2

0 11 2

1 5 2

1 2 2

0 1

366(10) = 101101110(2)

В восьмеричной системе используются цифры 0 - 7. В шестнадцатеричной системе используют цифры 0 - 9, A, B, C, D, E, F.

Десятичная |

Двоичная |

Восьмеричная |

Шестнадцатеричная |

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 10000 |

0 1 2 3 4 5 6 7 10 11 12 13 14 15 16 17 20 |

0 1 2 3 4 5 6 7 8 9 A B C D E F 10 |

Перевод из восьмеричной или шестнадцатеричной системы в двоичную и обратно осуществляется просто:

101 | 101 | 110(2) 1 | 0110 | 1110(2)

5| 5| 6(8) 1 | 6| С(16)

Для обозначения системы счисления после цифры ставят одну из букв:

H - шестнадцатеричная

D - десятичная

B - двоичная.

Таблица сложения Таблица умножения

0+0 = 0 0*0 = 0

0+1 = 1 0*1 = 0

1+0 = 1 1*0 = 0

1+1 = 10 1*1 = 1

Примеры: 10101101 10101111

+1011101 - 1011100

100001010 01010011

1 0110110 101011110 1010

х  10101 - 1010

10101 - 1010

100011

100011

10110110 01111

10110110 - 1010

1 0110110

0110110

1 11011101110 01010

11011101110 01010

101011110B = 350D

100011B = 35D;

350 / 10 = 35

При вычитании из меньшего числа большего, например:

3 - 4 = 011 - 100, проводятся следующие преобразования:

Инвертируем второе число: 4 = 011

Прибавляем 1 = 100

Складываем первое и второе числа:

0.011

+ 1.100

1.111

Затем проводим те же преобразования: 000 + 1 = 001

Булевая алгебра.

Булева алгебра оперирует двоичными переменными, которые подчиняются условию: Х=1, если Х0 и Х=0, если Х1.

Переключательная, или булева, функция вида Y= f(х1,х2,....,хn) относительно аргументов х1,х2,....,хn, как и ее аргументы, может принимать только два значения - 0 и 1.

Все аксиомы и законы булевой алгебры могут быть представлены в двух видах, что следует из принципа дуальности (двойственности) логических операций, согласно которому операции конъюнкции и дизъюнкции допускают взаимную замену, если одновременно поменять логический 0 на логическую 1, а 1 на 0.

Аксиомы (тождества) алгебры логики

а) аксиомы операции отрицания:

_ _

0 = 1 или дуальное отношение 1 = 0;

б) аксиомы операций с константами 0 и 1:

0 0 = 0 или 1 1 = 1;

1 0 = 0 1 = 0 или 0 1 = 1 0 = 1;

1 1 = 1 или 0 0 = 0.

Из аксиом вытекают законы булевой алгебры.

а) Переместительный закон (закон коммутативности):

Х1 Х2 = Х2 Х1 или Х1 Х2 = Х2 Х1.

б) Сочетательный закон (закон ассоциативности):

Х1 Х2 Х3 = Х1 (Х2 Х3) = (Х1 Х2) Х3 или

Х1 Х2 Х3 = Х1 (Х2 Х3) = (Х1 Х2) Х3.

в) Распределительный закон ( закон дистрибутивности):

Х1 (Х2 Х3) = Х1 Х2 Х1 Х3 или

Х1 (Х2 Х3) = Х1 Х2 Х1 Х3.

г) Закон повторения (тавтологии, идемпотентности):

Х1 Х1 Х1= Х1 или Х1 Х1 Х1 = Х1.

д) Законы операций с константами:

Х1 0 = 0 или Х1 1 = 1;

Х1 1 = Х1 или Х1 0 = Х1.

е) Закон двойной инверсии:

Х = Х.

ж) Закон обращения:

__ __

если Х1 = Х2 , то Х1 = Х2.

з) Закон дополнительности:

__ __

Х1 Х1 =0 или Х1 Х1 = 1.

и) Законы дуальности (законы де Моргана):

_______________ ___ __ __

Х1 Х2 .... Хn = Х1 Х2 ..... Хn.

Инверсия конъюнкции (логического произведения) двух и более переменных равна дизъюнкции (логической сумме) инверсий этих переменных.

_______________ __ __ ___

Х1 Х2 .... Хn = Х1 Х2 .... Хn.

Инверсия дизъюнкции (логической суммы) двух и более переменных равна конъюнкции (логическому произведению) инверсий этих переменных.

к) Закон (правило) поглощения:

Х1 (Х1 Х2) = Х1 или Х1 ( Х1 Х2) = Х1.

Поглощается переменная Х2.

л) Закон (правило) склеивания:

__

( Х1 Х2 ) ( Х1 Х2 ) = Х1 или дуальная форма

__

( Х1 Х2 ) ( Х1 X2 ) = Х1.

м) Правило вычеркивания:

__ __

(Х1 Х2 ) Х1 = Х2 Х1 или дуальная форма

___ ___

(Х1 Х2 ) Х1 = Х2 Х1.

ЛОГИЧЕСКИЕ ФУНКЦИИ ДВУХ ПЕРЕМЕННЫХ

Областью определения логической функции n переменных является совокупность комбинаций этих переменных. Так как для n-разрядного двоичного числа имеется всего 2n различных комбинаций, то область определения логической функции n переменных состоит из m=2n точек. Поскольку в каждой позиции (точке) функция может принимать значение 0 или 1, то, следовательно, для n переменных может быть составлено 2m логических функций. Например, при двух переменных Х1,Х2 область определения функции состоит из 22 = 4 точек (00, 01, 10, 11), и мы имеем 24 = 16 логических функций. Некоторые из этих функций зависят не от всех аргументов. Такие функции называются вырожденными.

Если определенным числовым комбинациям элементов, которые могут принимать значения 0 и 1 можно поставить в соответствие функцию числа, принимающего те же значения, то такую функцию можно назвать логической.

N функции |

X1 0 0 1 1 X2 0 1 0 1 |

Обозначение |

Наименование |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

0 Х1 ^ Х2 Х1 Х2 Х1 Х2 ^ Х1 Х2 Х1 Х2 Х1 v Х2 Х1 ^ Х2 Х1 Х2 Х2 Х2 Х1 Х1 Х1 Х2 Х1 / Х2 1 |

Константа 0 Конъюнкция, лог. "И" Запрет по Х2 Тождество Х1 Запрет по Х1 Тождество Х2 Сумма по мод. Х2 Дизъюнкция, лог. "ИЛИ" Стрелка Пирса Эквивалентность Инверсия Х2 Импликация от Х2 к Х1 Инверсия Х1 Импликация от Х1 к Х2 Штрих Шеффера Константа 1 |

Понятия о комбинационных схемах.

Понятия о конечном автомате (последовательные схемы).

Организация производственного процесса. Принцип хранения программ.

Вычислительный процесс может быть реализован:

1. Можно сконструировать устройства, логическая схема которых соответствует действиям алгоритма вычисления, или одно устройство, соответствующее программе вычислений. Такой

способ организации вычислительного процесса называется коммутационным программированием.

К

АЛБ

Данные результата

Данные результата

Данные

2. Можно сконструировать схему, которая выполняет алгоритмические и логические действия, на вход которого можно подавать переменные и управляющие сигналы, а на выходе получить результат.

3. Принцип хранимой программы, сущность заключается в том, что можно закодировать определенным образом каждое из указаний АЛБ так, что оно может быть расшифровано устройством управления, и записать эти указания в специальное запоминающее устройство, причем так, что УУ считывает и дешифрирует их в определенной последовательности.

ОЧ

Кдп Данные

Адрес Ячейки зу

АЛБ

УУ

Программа и данные находятся в одном ЗУ и могут обрабатываться одинаково.

Обобщенная структурная схема ЭВМ.

Микропроцессор - это сравнимое по структуре и возможностям с процессором функционально-законченное структурное изделие, реализованное на БИС и предназначенное для преобразования и обработки информации с помощью арифметического устройства, внутренних регистров и устройства управления. Микропроцессорный элемент - это схемотехнически ЭВМ с программируемыми функциями.

Упрощенная схема вычислительного процесса по рис.1.

В результате работы УУ осуществляется считывание нужной информации из памяти машины и её обработка в арифметическом устройстве. Результаты отправляются обратно. Для того, чтобы считать нужную информацию и записать её обратно, нужна определенная организация памяти. Эта организация обычно заключается в кодировании, т.е. в нумеровании отдельных частей памяти. По заданному коду УУ находит участок памяти, содержащий нужную информацию. Для того, чтобы осуществить какое-либо преобразование информации, хранящейся в памяти, необходимо указать её адрес и последовательность операций над ней.

Обобщенная структурная схема ЭВМ

Процессор

ЗУ

Пульт

Упр. ЭВМ

Интерфейс

Пульт

Упр.

тех

УСО

КСУ

Процессор предназначен для управления операциями.

ЗУ - для хранения данных и команд.

Пульт управления ЭВМ - для управления вводом \ выводом данных

Пульт управления технологический - для управления техпроцессом, ради которого создана машина.

Комплект согласующих устройств - для подключения стандартных внешних устройств, дополнительных устройств в\в, дополнительных устройств хранения информации и т.п.

Устройство связи с объектом - предназначено для управления объектом, для связи с внешним объектом

Интерфейс - комплекс программных и аппаратных средств, предназначенных для связи объектов между собой.

Управляющая ЭВМ отличается наличием УСО.

УСО.

Устройство связи с объектом (УСО)

УСО предназначено для связи систем управления с электроавтоматикой объекта, физическими величинами и т.д.

Датчики Исполнительные устройства

Ан.

Ан.

Объект

Ц

Ц

Ввод

Вывод

ЭВМ

Ан.

Ан.

Ц

Ц

Объект описывается физическими характеристиками. Объект должен иметь ДОС для преобразования физических величин в унифицированные электрические сигналы. Датчики подразделяются на аналоговые и цифровые.

Аналоговые:

1) генераторные (термопара);

2) параметрические (терморезистор);

Цифровые датчики выдают коды электрических сигналов. Цифровыми называют часто бинарные датчики - выдают два сигнала (есть, нет). Выходное напряжение бинарного датчика должно быть 12 В или 24 В. Пример бинарного датчика: геркон. Аналоговая цифровая системы ввода УСО предназначены для преобразования аналоговых и цифровых физических величин, напряжений и токов, и их характеристик, форму, приемлемую для использования в ЭВМ. Форма, пригодная для использования в ЭВМ - это сигналы ТТЛ логики. Подсистема аналогового ввода осуществляет преобразование аналоговых напряжений и токов в цифровой код. Функции, выполняемые подсистемой аналогового ввода:

1) нормирование - усиление или ослабление сигналов усиление фильтрация - ограничение спектра преобразуемого сигнала смещение уровня преобразование тока в напряжение

2) коммутация сигналов, т.е. мультиплексирование аналоговых сигналов

3) аналого-цифровое преобразование

Подсистема аналогового вывода.

Существует три конфигурации:

1) с ЦАП в каждом выходном канале

2) с одним ЦАП, работающем в режиме разделения во времени и

с выходным запоминающим усилителем в каждом выходном канале.

3) комбинированный.

Первый вариант обладает высоким быстродействием и высокой ценой. Второй вариант обладает низкой ценой и низким быстродействием.

Подсистема цифрового ввода осуществляет:

1) ввод дискретных сигналов

2) подсчет повторяющихся сигналов.

Устройства: счетчики, регистры, блоки согласования.

Подсистема цифрового вывода осуществляет:

1) выработка цифровых (бинарных) управляющих сигналов для управления коммутирующими элементами (ключи, контакторы). Стандартное напряжение в коммутирующих цепях 110,220 В.

В цифровых подсистемах ввода и вывода применяются элементы гальванической развязки. Гальваническая развязка нужна для

отделения силовых и управляющих цепей.

Архитектурные и структурные особенности управляющих ЭВМ. Принципы проектирования.

Архитектурные и структурные особенности ЭВМ определяются принципом проектирования:

1. Магистральность

2. Модульность

3. Микропрограммируемость

Магистраль1 – Данные

Магистраль1 – Данные

Магистраль2 – Адрес

Магистраль3 – Управление

..................

1. Магистральность предполагает канальный характер связи блоков ЭВМ, все блоки системы подключаются к общей системе управляющих шин. Магистральность позволяет создавать схемотехнически наращиваемые системы, легко изменять архитектуру системы и её характеристики.

2. Модульность предполагает унифицированный ограниченный набор микромодулей, отличающихся конструктивной особенностью, функциональной автономностью и структурной универсальностью. Модульность определяет набор команд, логическую организацию и конструктивные особенности. Каждый модуль должен отличаться структурной законченностью. Каждый модуль должен выполнять свою функцию автономно, самостоятельно, не перегружая другие модули. Идентичен только характер связи между блоками, остальное можно менять, что позволяет менять характеристики, объем и структуру ЭВМ.

3. Микропрограммирование.

УУ

Запоминающее устройство микропрограмм

Блок

микропрограммного управления

устройства

устройства

процессора

Методы проектирования:

1) Структурный.

2) Программируемый - позволяет в процессе проектирования менять набор команд, позволяет создать несколько модификаций СУ.

Каждая команда ЭВМ является совокупностью элементарных действий, в зависимости от условий применения желательно применять набор элементарных действий. Схемное устройство управления не дает возможности изменять совокупность элементарных действий. Программируемое устройство управления осуществляет подобные изменения за счет особой структуры системы управления. Эта структура предполагает в составе СУ:

- блока программного управления, который состоит из схемы определения следующего адреса, регистров и флагов, а также

- СУ микрокоманд, определяющего последовательность микроопераций и формирование управляющих сигналов процессора для реализации команд.

Системы и набор команд меняют путем изменения значения содержимого ЗУ микропрограмм.

В настоящее время разработчики ЭВМ сталкиваются с микро программируемыми ЭВМ очень редко, в основном они используются в микросхемотехнике для разработки БИС.

Классификация УЭВМ по назначению.

Назначение и область применения. Структура АСУ с ЭВМ в различных областях применения.

Назначение и область применения управляющих ЭВМ.

По применению управляющие ЭВМ делятся на:

1) узкоспециализированные

2) общепромышленного назначения

1. Целесообразно использовать в следующем случае:

- алгоритм управления не сложен и не велик по объему

- управляющее устройство характеризуется повышенной надежностью

- алгоритм управления не изменяется существенно в процессе разработки и эксплуатации системы

- на потребляемую мощность, габариты и массу и другие эксплуатационные характеристики наложены жесткие ограничения

- потребность в устройствах данного типа довольно велика.

2. Целесообразно использовать когда:

- вышеперечисленные 5 факторов не важны;

- разработка системы должна быть выполнена в сжатые сроки;

- система должна иметь разветвленную структуру программных средств;

не используются большими париями, т.к. цена высока.

Отличия 1 от 2 состоит в том, что 1 оптимизируется на конкретно выполняемые функции для конкретной задачи.

Назначение:

в СУ ЭВМ предназначены для реализации устройства управления, при этом они выполняют следующие функции:

1) прием информации от измерительных устройств, локальных автоматических систем управления, устройств защиты и блокировки и других источников информации.

2) преобразование информации по заданному алгоритму управления

3) выдача результатов на исполнительное устройство, оператору и другим потребителям

При этом ЭВМ подразделяются по решаемым задачам:

1) сбор данных и их обработка

2) управление в режиме разомкнутого контура (через оператора)

3) программное управление пуском и остановом агрегата

4) прямое или непрямое цифровое управление процессом или агрегатом в режиме замкнутого контура.

В режиме разомкнутого контура.

ЭВМ собирает и обрабатывает данные, моделирует процессы в ОУ и на основе этой модели выдает советы. Применяют когда машине нельзя доверить принятие решения.

ЭВМ

Д

ОУ

ИМ

У

ВВ

ВВ

Человек

Пульт управления

Режим непосредственного цифрового управления

ЭВМ выполняет те же задачи, но вместо выдачи советов выдаёт управляющий сигнал на ИМ.

ЭВМ

Д

ОУ

ИМ

У

Человек

Режим непрямого цифрового управления.

ЭВМ воздействует на ОУ не прямо, а через локальный регулятор (ЛР), который является локальной системой управления. Кроме сбора информации и формирования управляющих воздействий ЭВМ решает задачу вычисления оптимальных установок для локальной системы управления.

ЭВМ

Д

ОУ

ИМ

У

ВВ

ВВ

Локальный регулятор

S

Иерархическая структура систем

управления

ЭВМ

УЭВМ

Управляющая ЭВМ

Управляющая ЭВМ

УМЭВМ

УМЭВМ

УМЭВМ

ЛСУ ........ .....

ИУ

Понятие СУ

Д

УУ

ОУ

ИМ

СУ - совокупность некоторых элементов, предназначенных для реализации задачи управления и решающая следующие задачи:

1) сбор данных, т.е. преобразование физических величин, характеризующих состояние объекта управления в унифицированные сигналы

2) обработка информации с целью преобразования в вид удобный для принятия решения

3) моделирование поведения объекта

4) принятие решений на основе собранной информации и модели

5) формирование управляющих воздействий

6) выдача управляющих воздействий

Когда не требуется реакция системы в течение заданного времени, применяется пакетный метод выполнения программ.

1. Пакетный режим предполагает, что система не требует мгновенной реакции системы. Режим ЭВМ - советчик. Принятие решения осуществляется в ручную.

2. Для режима реального масштаба времени система должна отреагировать за время, не превышающее минимально заданного или расчетного. Полоса пропускания управляющей ЭВМ очень влияет на устойчивость. Один из основных расчетов, который проводи при проектировании систем.

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ УПРАВЛЯЮЩИХ ЭВМ

Точность

Адресность

Набор команд

Быстродействие

Режимы обмена

Точность ЭВМ.

Точность. определяется разрядностью системы

Общая погрешность системы

Dобщ= Dм + Dвх + Dинстр +Dобр

Dм - методическая погрешность, отражает степень совершенства математической модели реального объекта. (Работа СД описывается с помощью дифференциального уравнения разного порядка, решение уравнений будет различно).

Dвх - погрешность, возникающая в результате трансформации входных переменных. Пока физическая величина преобразуется в цифровой код, она приобретает погрешность.

Dобр - (обработки) - методическая погрешность, определяется погрешностью численных методов, используемых при решении математической задачи.

Dинстр - обусловлена конечным числом разрядов, используемых для представления чисел в ЭВМ. Ошибка возникает из необходимости округления и накопления погрешностей.

Увеличение разрядности приводит к увеличению стоимости машины и уменьшению надежности.

ЭВМ характеризуется набором выполняемых инструкций.

Быстродействие.

Быстродействие.

- косвенно определяется числом операций в секунду, такая характеристика характеризует технические возможности процессора без учета параллельности отдельных блоков ЭВМ и особенностей решаемой задачи и не отражает полностью характеристику быстродействия. Существует такая характеристика - производительность ЭВМ, определенная на основе статистических методов по функции Гибсона. Производительность зависит от времени выполнения и частоты исполнения операции

k k

Р = S k дi / [ S k ci ti ] i=1 i=1

kд - динамическая частность

kс - статистическая частность

ti - время выполнения i-ой операции

k - общее число типов операции

kc оценивается статистическим распределением операции

взамен программы.

kд - динамическим распределением при реализации программы.

Пример для одноадресной управляющей ЭВМ:

-

Операции

Kс

kд

основные

над кодами

управления

связи с внешним устр.

специальные

23,5

49,5

18

3

6

24,3

44,2

20,5

2,8

7,7

Адресность и способы адресации.

Адресность

Характеристика, которая определяет число адресов инструкции или команды, способы связи отдельных элементов между собой (способы адресации)

ЭВМ бывают:

-одноадресные

-двухадресные

-многоадресные

-с переменной адресносностью

Инструкция одноадресная содержит инструкцию и один адрес операнда.

Чем больше адресов, тем удобней программировать.

Способы адресации:

1) Адресные команды:

-непосредственная адресация

-непрямая адресация ( косвенная и относительная )

-прямая адресация

2) Безадресные команды:

-счетчик команд

-указатель стека

-останов

прерывание

При непосредственной адресации информация, участвующая в выполнении операции помещается в адресной части команды:

MVI A(регистр), В (число)

Прямая адресация: адрес операнда непосредственно указывается в адресной части команды.

Непрямая адресация: адресная часть используется для определения адреса операнда.

При косвенной адресации указывается адрес ячейки, в которой содержится адрес операнда. Косвенная адресация используется, если заранее не известен адрес расположения операнда.

При выполнении программы адрес будет вычислен.

Процессор содержит базовый регистр.

При относительной адресации адрес указанный в адресной части команды например прибавляется к содержимому базового регистра и таким образом получается фактический адрес операнда. Фактический адрес операнда получается путем канкотенции приращения, заданного в адресной части команды с содержимым одного из регистров процессора.

Безадресные команды используются для организации работы специальных блоков процессора, таких как счетчик команд, указатель стека, блок управления прерываниями и др.

Набор команд.

Набор команд определяется количеством разновидностей выполняемых машинных операций.

Операции делят на 5 категорий:

- основные

- операции над кодами

- операции управления

- операции, связанные с внешними устройствами

- специальные

Основные операции:

- арифметические,

- связанные с обработкой мат. моделей

- логические

Операции над кодами:

- сдвиг

- ссылка

- специальные (десятичная коррекция)

Операции управления:

- условные, безусловные переходы

- операции управления прерываниями, пуском, остановом

- управление циклами

- вызовы подпрограмм

Операции с внешними устройствами:

- передача во внешнее устройство

- прием из внешнего устройства

Специальные операции:

- управление внутренней структурой процессора (работа с регистрами)

Микропрограммность позволяет изменять набор команд.

Режимы обмена.

Режимы обмена информации

1. Пакетный режим

2. Режим реального масштаба времени

1. Обмен между процессором и периферийными устройствами

2. Обмен между процессором и памятью

3. Обмен между периферийными устройствами и памятью

Режимы ввода \ вывода предполагают обмен между процессором и периферийными устройствами и процессором и памятью. Особенность ввода \ вывода состоит в значительном отличии в быстродействии процессора и внешних устройств и способности выполнять функции.

Режимы обмена:

1. Программно-управляемый синхронный

2. - " - асинхронный

3. С использованием прерывания

4. Внепрограммный, с помощью канала ПДП

1. Режим программно-асинхронный.

Применяется тогда, когда периферийное устройство всегда готово к обмену. Предполагаем, что быстродействие внешнего устройства сравнимо с быстродействием процессора, а скорость обмена сравнима с операциями ввода \ вывода.

ЭВМ

ВУ

Т1

Т2

Синхр.

Если начало операции ВУ синхронизировалось с началом операции ЭВМ, то данные, которые будут передаваться, могут быть приняты без искажений и потерь.

2. Предполагаем, что процессы несинхронизированны. Для организации достоверного приема информации от ВУ процессор ожидает готовности ВУ, анализируя специальный сигнал, называемый флагом.

ЭВМ

ВУ

флаг

Недостаток: ЭВМ простаивает, ожидая флага готовности ВУ.

Достоинство: ВУ с любым быстродействием могут быть обслужены.

3. Обмен по прерыванию.

Достоинства: сокращаются затраты машинного времени на обмен с медленно действующими ВУ, из-за отсутствия повторения цикла опроса.

Недостаток: требуются дополнительные аппаратные затраты необходим контроллер прерываний.

Можно выделить 5 основных этапов механизма прерывания:

1) Фиксация прерывания. Предполагается, что ЭВМ сигнал от внешнего устройства может принимать, а может не принимать. Фиксация нужна для того, чтобы не потерять информацию от ВУ. Существуют процессы, запрещающие их прерывание. Процесс запроса прерывания это программно-аппаратная функция.

2) Анализ прерывания. Так как в ЭВМ может существовать несколько устройств, требующих обмена с прерыванием, то может поступить несколько запросов прерывания одновременно. Поэтому каждому типу прерываний присваивается определенный приоритет.

3) Фиксация состояния процессора. Для фиксации состояния процессора необходимо зафиксировать состояния: Счетчика адреса, аккумулятора и указателя стека.

Для полного сохранения необходимо еще сохранить состояние регистров.

Эта операция выполняется аппаратным путем.

4) Выполнение программы обслуживающей прерывание. Для каждого уровня прерывания назначен некоторый адрес в адресной части памяти, который будет содержать адрес подпрограммы обработки прерывания. Этот адрес называется адрес-вектор.

5) Восстановление прерванного процесса. Необходимо восстановить состояние регистров, указателя стека, аккумулятора и счетчика адреса.

4. Обмен через канал ПДП.

Процессор не принимает в этом обмене участия. Это не программный обмен. ВУ считывает или записывает информацию из\в память напрямую. Этот режим еще больше сокращает затраты машинного времени, но требует специальной аппаратуры в периферийных устройствах: нужен контроллер ПДП.

Существует 3 режима ПДП:

1) Режим с захватом самый простой и медленный. ВУ осуществляет захват шин памяти на все время обмена.

2) Приостановка работы процессора на 1 машинный цикл для передачи слова через канал ПДП. Существуют аппаратные усложнения, но быстродействие выше.

3) Одновременная работа процессора и канала ПДП. В процессе выполнения команд процессор не всегда обращается к памяти. На это время канал ПДП может захватить шину. Если возникнет ситуация обращения процессора к памяти, то обращение задерживает до конца передачи слова по каналу ПДП. Это самый дорогой и быстрый способ обмена.

РЕЖИМ ОБМЕНА ПРОЦЕССОР-ПАМЯТЬ

Различают 2 вида обмена: изолированный и совмещенный.

При 1-м режиме существует отдельный канал памяти и ВУ.

При 2-м режиме канал общий.

Для изолированного режима обмена применяют 2 формата адреса: для ЗУ и для ВУ. Формирование форматов адреса осуществляется микропрограммно, или схемным устройством управления.

Для 2-го вида один формат адреса. Обращение к регистрам ВУ как к ячейкам памяти ЗУ.

Изолированная шина: Совмещенная шина:

Память

ЧТ пам.

ЗП пам. Пер. Адр.

ВУ

ЗП ВУ Пер. Дан.

При совмещенной шине часть адресов, выделенных под ВУ используется для стандартных устройств в\в. По ШАД адрес и данные передаются в два такта. Существует управляющая шина, кот синхронизирует передачу адреса и данных.

Структура МП КР 580ВМ80.

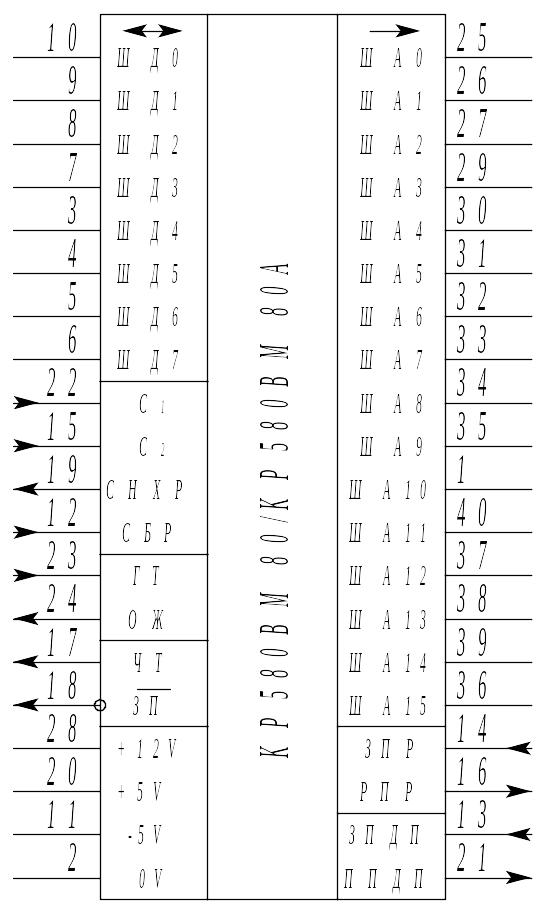

На Рис. 0- представлена структурная схема МП КР580, а на показано назначение выводов корпуса процессора.

МП имеет 3 шины: 8-разрядную двунаправленную внутреннюю шину данных (ШД), 16-разрядную адресную шину (ША) и шину управления (ШУ).

Рис. 0- . Структурная

схема МП КР580.

. Структурная

схема МП КР580.

Внутренняя ШД является магистралью, по которой могут обмениваться данными все подключенные к ней блоки (узлы) МП. Одновременно по ШД осуществляется обмен только между двумя узлами МП, т. е. все узлы, подсоединенные к ШД, разделяют ее во времени.

ШУ содержит линии для передачи управляющих сигналов, признаков состояния процессора и периферийных устройств, в том числе линии: синхронизации передачи и идентификации информации, передаваемой по ШД; сигналов, информирующих МП о готовности периферийных устройств; сигнала запроса прерывания от периферийных устройств и сигнала разрешения прерывания и др.

Выводы микропроцессора имеют следующее назначение:

Выводы C1 и C2 используются для ввода в микропроцессор синхросигналов от тактового генератора.

Выводы ШД0 … ШД7 образуют двунаправленную шину данных для обмена данными между процессором и внешней памятью или внешними устройствами.

Выводы ША0 … ША15 образуют шину адреса, которая используется процессором для вывода адреса ячейки памяти или адреса внешнего устройства, с которой(ым) будет проводиться обмен данными.

Вывод СНХР (СИНХР) используется для синхронизации процессором внешних устройств.

Вывод СБР – это аппаратный сброс микропроцессорной системы.

Вывод ГТ используется процессором для приема сигналов от внешнего устройства или памяти о готовности его (ее) к обмену данными.

Вывод ОЖ используется МП для формирования им сигналов внешнему устройству или памяти об ожидании готовности устройства (памяти) к обмену информацией между ним и процессором.

Выводы ЧТ и ЗП используются процессором для формирования им сигналов чтения и записи для внешней памяти и устройств ввода/вывода.

Выводы ЗПР и РПР – выводы для сигналов запроса и разрешения прерывания.

Выводы ЗПДП и РПДП – выводы для сигналов запроса и разрешения прямого доступа к памяти.

Для нормального функционирования микропроцессорной системы недостаточно управляющих сигналов, генерируемых на выводах МП. МП-система в каждом машинном цикле должна получать более полную информацию о состоянии процессора. Из-за недостаточного количества выводов на корпусе МП процессор на первом такте каждого машинного цикла (МЦ) выдает через шину данных дополнительную информацию о своем состоянии, которая представляет собой 8-разрядное слово состояния процессора (ССП). Т. к. сигнал СИНХР вырабатывается в МП в начале каждого МЦ, то он используется в качестве сигнала, идентифицирующего информацию, представленную в ШД, как слово состояния. По сигналу СИНХР внешний по отношению к процессору регистр (регистр слова состояния РСС) должен читать данные с ШД и сохранять их в виде ССП на своих выходных выводах. Сигналы с выхода РСС используются в качестве сигналов управления периферией МП-системы [Error: Reference source not found, Error: Reference source not found].

При рассмотрении структуры МП можно выделить следующие ее основные части: блок регистров, арифметическо-логическое устройство (АЛУ), буферные схемы, устройство управления (УУ).

0

0