- •1Формы представления и кодирования чисел с плавающей точкой:

- •2Сложение чисел в формате с плавающей точкой:

- •5Основные понятия алгебры логики:

- •6Основные законы и тождества алгебры логики.

- •7.Представление логической функции:

- •8.10. Минимизация переключательных фун-ций с использованием законов и тождеств.

- •9Карты Карно-Вейча. Свойства карты. Получение карты по формуле и таблице истинности.

- •16Преобразователь двоичных кодов.

- •17 Преобразователь прямого кода в дополнительный.

- •19Полный одноразрядный сумматор

- •20Назначение, принцип действия десятичного сумматора

- •21Асинхронный rs триггер.

- •22Синхронный rs триггер.

- •23 D триггер.

- •24 Jk триггер.

- •25 Параллельный регистр – применяется для ввода, хранения и выдачи двоичной информации в параллельном коде.

- •26. Назначение, принцип действия, устройства сдвигающего регистра.

- •27. Назначение, принцип действия, устройство реверсивного регистра.

- •28. Назначение, принцип действия, устройство суммирующего счетчика.

- •29. Назначение, принцип действия, устройство вычитающего счетчика.

- •30. Назначение, принцип действия, устройство реверсивного счетчика.

- •31.Cчётчик с различным коэфицентом счёта.

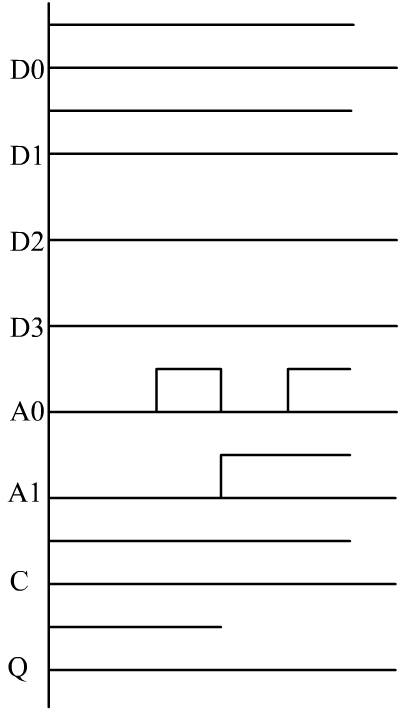

- •33. Микросхемы памяти статического озу . Временные диаграммы работы .

- •34. Микросхемы памяти динамического озу . Принцип действия по структурной схеме.

- •35Элемент памяти динамического озу.

- •38.Виды динамической памяти: fpm, edo, bedo, sdram, drdram.

- •39. Классификация и виды пзу.

- •40. Масочные пзу на диодах и транзисторах.

- •41.Програмируемые пзу. Принцип действия, надежность хранения информации.

- •42Принцип действия репрограммируемых пзу.

- •43. Виды современных пзу (rom, eprom, eeprom, флешь память).

- •44. Генераторы импульсов. Схемы. Времен. Диаграммы. Формир. Имп. Врем. Диагр. Сх.

- •45.Правила перевода целых и дробных чисел из одной системы счисления в другую.

17 Преобразователь прямого кода в дополнительный.

X3 X2 X1 X0 D1 D2 D3 D0

0 0 0 0 0 0 0 0

0 0 0 1 1 1 1 1

0 0 1 0 1 1 1 0

0 0 1 1 1 1 0 1

0 1 0 0 1 1 0 0

0 1 0 1 1 0 1 1

0 1 1 0 1 0 1 0

0 1 1 1 1 0 0 1

1 0 0 0 1 0 0 0

1 0 0 1 0 1 1 1

1 0 1 0 0 1 1 0

1 0 1 1 0 1 0 1

1 1 0 0 0 1 0 0

1 1 0 1 0 0 1 1

1 1 1 0 0 0 1 0

1 1 1 1 0 0 0 1

D1=X0 (+) X1

D2=(X0 v X1) (+) X2

D3=((X0 v X1) v X2) (+) X3

Yi=ŵXi v wDi

Y0=X0

Y1=ŵX1 v w(X0 (+) X1)

Y2=ŵX2 v w((X0 v X1) (+) X2)

Y3=ŵX3 v w((((X0 v X1) v X2) (+) X5))

18 Назначение, принцип действия, устройства полусумматора. Сумматор – это узел, в котором выполняется арифметическая операция суммирования цифровых входов двух двоичных чисел

Полусумматор

ai bi Si Pi

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Si= ai*bi v ai bi*

![]()

Pi=aibi

19Полный одноразрядный сумматор

ai bi Pi Si Pi+1

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Si= ai* bi*Pi V *aibi Pi* V ai bi* Pi* V aibiPi=Pi(aibi v ai* bi*) V Pi*(ai*bi V ai bi*)

Pi+1=Pi(ai*bi V ai bi*) V

![]()

20Назначение, принцип действия десятичного сумматора

Сумматор – это узел, в котором выполняется арифметическая операция суммирования цифровых входов двух двоичных чисел.

на входы а-i и в-i подаются 2 числа в двоичной форме которые будут складываться. На вход р-i – значение переноса. На выходах S-i образуется сумма этих чисел.

![]()

21Асинхронный rs триггер.

Триггер типа RS имеет 2 входа установки в единицу (S) и установки в ноль (R).

Если R=0 и S=0, то триггер работает в режиме хранения информации: Q n+1=Qn.

Если R=0 и S=1, то на прямом выходе устанавливается в единицу: Q n+1=1.

Если R=1 и S=0, то на прямом выходе устанавливается ноль (режим сброса): Q n+1=0.

Комбинация R=1 и S=1 – запрещенная комбинация и значения триггера на прямом и инверсном выходах не определены. В асинхронных триггерах изменение состояния происходит при подаче сигналов на информационный вход.

Q![]() t

S

R

Qt+1

t

S

R

Qt+1

0 0 0 x

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 x

1 0 1 1

1 1 0 0

1 1 1 1

![]() Qt

R S Qt+1

Qt

R S Qt+1

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 x

1 0 0 1

1 0 1 1

1 1 0 0

1 1 1 x

22Синхронный rs триггер.

Триггер типа RS имеет 3 входа установки в единицу (S) и установки в ноль (R) информационный (С).

Если R=0 и S=0, то триггер работает в режиме хранения информации: Q n+1=Qn.

Если R=0 и S=1, то на прямом выходе устанавливается в единицу: Q n+1=1.

Если R=1 и S=0, то на прямом выходе устанавливается ноль (режим сброса): Q n+1=0.

Комбинация R=1 и S=1 – запрещенная комбинация и значения триггера на прямом и инверсном выходах не определены. В синхронных триггерах кроме информационных входов есть 1 или несколько дополнительных входов для сигналов управления состояние таких триггеров изменяется при подаче синхронизирующих сигналов в соответствии со значением сигналов на инф. входах.

Q t

S R Qt+1(c=0) Qt+1(c=1)

t

S R Qt+1(c=0) Qt+1(c=1)

0 0 0 0 0

0 0 1 0 0

0 1 0 0 1

0 1 1 0 x

1 0 0 1 1

1 0 1 1 0

1 1 0 1 1

1 1 1 1 x

![]()