- •1Микропроцессоры. История появления и развития.

- •6Внутреннее построение микропроцессора. Алу.

- •2Архитектуры процессоров по разделению памяти данных и команд (Архитектура фон Неймана, Гарвардская архитектура).

- •3Архитектуры процессоров по набору команд (risc, cisc).

- •4Микропроцессор, микрокомпьютер, микроконтроллер. Определения и отличительные особенности.

- •5Внутреннее построение микропроцессора. Структурная схема микропроцессора.

- •7Внутреннее построение микропроцессора. Аккумулятор, счетчик команд.

- •8Внутреннее построение микропроцессора. Регистры.

- •9Микропроцессорная система. Шинная структура связей.

- •14. Аппаратное обеспечение микроконтроллера. Базовый функциональный блок микроконтроллера.

- •10Микропроцессорная система. Выходные каскады цифровых микросхем

- •11. Режимы работы микропроцессорной системы. Программный обмен информацией.

- •12. Режимы работы микропроцессорной системы. Обмен по прерываниям.

- •13. Режимы работы микропроцессорной системы. Прямой доступ к памяти.

- •1 5. Аппаратное обеспечение микроконтроллера. Изменяемый функциональный блок микроконтроллера.

- •17 Схема сброса

- •18 Порты ввода/вывода

- •19 Сторожевой таймер

- •20 Резидентная память

- •21 Микроконтроллер msp430. Общие сведения

- •22 Микроконтроллер msp430. Центральный процессор

- •23 Микроконтроллер msp430. Режимы адресации

- •24 Микроконтроллер msp430. Систематактирования

- •25 Микроконтроллер msp430.Энергосберегающиережимы

- •27. Микроконтроллер msp430 Порты ввода-вывода

- •37Ацп. Определение. Основные понятия: разрешение, разрядность, частота дискретизации.

- •28.Микроконтроллер msp430.16битный ацп sd16_a

- •29. Микроконтроллер msp430. Модуль универсального последовательно интерфейса

- •30. Микроконтроллер msp430. Таймеры

- •31. Микроконтроллер msp430. Модуль таймера микроконтроллера. Архитектура.

- •32. Микроконтроллер msp430. Модуль таймера микроконтроллера. Режимы счёта.

- •Непрерывный режим

- •Режим «вверх/вниз»

- •36Микроконтроллер msp430. Модуль таймера микроконтроллера. Регистры.

- •33. Микроконтроллер msp430. Модуль таймера микроконтроллера. Прерывание таймера. Прерывания Таймера а

- •Прерывание taccr0

- •Генератор вектора прерывания taiv

- •34. Микроконтроллер msp430. Модуль таймера микроконтроллера. Блоки захвата/сравнения.

- •35. Микроконтроллер msp430. Модуль таймера микроконтроллера. Устройство вывода. Модуль вывода

- •Режимы вывода

- •38Ацп. Типы ацп. Параллельного преобразования.

- •39Ацп. Типы ацп. Последовательного приближения.

- •40Ацп. Типы ацп. Интегрирующие.

- •42Ацп. Погрешности, причины.

- •57. Tms c281x. Конвейер

- •43. Последовательные интерфейсы. Spi.

- •45Последовательные интерфейсы. Uart.

- •44. Последовательные интерфейсы. I2c.

- •46Последовательные интерфейсы. Rs-232с.

- •47Последовательные интерфейсы. Rs-485.

- •49. Программируемые логические контроллеры

- •51. Процессоры цифровой обработки сигналов и реальный масштаб времени.

- •52. Процессоры цифровой обработки сигналов (пцос). Требования к пцос.

- •53. Процессоры цифровой обработки сигналов (пцос). Типовые задачи и области применения.

- •54. Tms c281x. Общие сведения

- •55. Tms c281x. Архитектура.

- •56. Tms c281x. Цпу. Аппаратный умножитель и атомарное алу.

- •58. Tms c281x. Страничная организация памяти.

- •59. Микропроцессорные системы управления. Управление двигателем постоянного тока.

- •60. Управление шаговым двигателем.

- •16.Система тактирования

9Микропроцессорная система. Шинная структура связей.

Д ля

достижения максимальной универсальности

и упрощения протоколов обмена информацией

в микропроцессорных системах применяется

так называемая шинная структура связей

между отдельными устройствами, входящими

в систему. Суть

шинной структуры связей

сводится к следующему.

ля

достижения максимальной универсальности

и упрощения протоколов обмена информацией

в микропроцессорных системах применяется

так называемая шинная структура связей

между отдельными устройствами, входящими

в систему. Суть

шинной структуры связей

сводится к следующему.

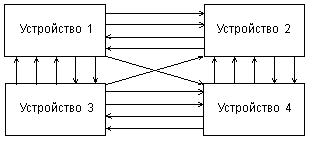

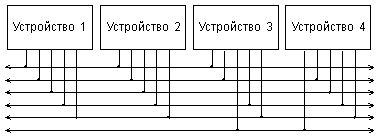

При классической структуре связей (рис. 1.5) все сигналы и коды между устройствами передаются по отдельным линиям связи. Каждое устройство, входящее в систему, передает свои сигналы и коды независимо от других устройств. При этом в системе получается очень много линий связи и разных протоколов обмена информацией.

Рис.

1.6. Шинная структура связей.

Рис.

1.6. Шинная структура связей.

При шинной структуре связей (рис. 1.6) все сигналы между устройствами передаются по одним и тем же линиям связи, но в разное время (это называется мультиплексированной передачей). Причем передача по всем линиям связи может осуществляться в обоих направлениях (так называемая двунаправленная передача). В результате количество линий связи существенно сокращается, а правила обмена (протоколы) упрощаются. Группа линий связи, по которым передаются сигналы или коды как раз и называется шиной.

При шинной структуре связей легко осуществляется пересылка всех информационных потоков в нужном направлении. Однако при шинной структуре связей вся информация передается по линиям связи последовательно во времени, по очереди, что снижает быстродействие системы по сравнению с классической структурой связей.

Большое достоинство шинной структуры связей состоит в том, что все устройства, подключенные к шине, должны принимать и передавать информацию по одним и тем же правилам (протоколам обмена информацией по шине). Соответственно, все узлы, отвечающие за обмен с шиной в этих устройствах, должны быть единообразны, унифицированы.

Существенный недостаток шинной структуры связан с тем, что все устройства подключаются к каждой линии связи параллельно. Поэтому любая неисправность любого устройства может вывести из строя всю систему, если она портит линию связи. По этой же причине отладка системы с шинной структурой связей довольно сложна и обычно требует специального оборудования.

14. Аппаратное обеспечение микроконтроллера. Базовый функциональный блок микроконтроллера.

Базовый функциональный блок включает:

- центральный процессор;

- внутренние магистрали адреса, данных и управления;

- схему формирования многофазной импульсной последовательности для тактирования ЦПУ и межмодульных магистралей;

- устройство управления режимами работы МК, такими как активный режим, режим пониженного энергопотребления, состояния начального запуска и прерывания.

Базовый функциональный блок называют процессорным ядром МК. Тип процессорного ядра определяет имя семейства МК, основой которого оно является.

10Микропроцессорная система. Выходные каскады цифровых микросхем

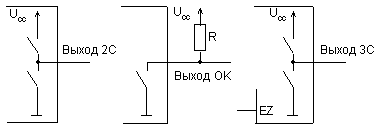

В системах с шинной структурой связей применяют все три существующие разновидности выходных каскадов цифровых микросхем:

•стандартный выход или выход с двумя состояниями (обозначается 2С, 2S, реже ТТЛ, TTL);

•выход с открытым коллектором (обозначается ОК, OC);

•выход с тремя состояниями с возможностью отключения (обозначается 3С, 3S).

Упрощенно эти три типа выходных каскадов могут быть представлены в виде схем на рис. 1.7.

Рис.

1.7. Три типа выходов цифровых микросхем.

Рис.

1.7. Три типа выходов цифровых микросхем.

У выхода 2С два ключа замыкаются по очереди, что соответствует уровням логической единицы (верхний ключ замкнут) и логического нуля (нижний ключ замкнут). У выхода ОК замкнутый ключ формирует уровень логического нуля, разомкнутый — логической единицы. У выхода 3С ключи могут замыкаться по очереди (как в случае 2С), а могут размыкаться одновременно, образуя третье, высокоимпедансное, состояние. Переход в третье состояние (Z-состояние) управляется сигналом на специальном входе EZ.

Выходные каскады типов 3С и ОК позволяют объединять несколько выходов микросхем для получения мультиплексированных (рис. 1.8) или двунаправленных (рис. 1.9) линий.

Р![]() ис.

1.8. Мультиплексированная линия.

ис.

1.8. Мультиплексированная линия.

Р![]() ис.

1.9. Двунаправленная линия.

ис.

1.9. Двунаправленная линия.

При этом в случае выходов 3С необходимо обеспечить, чтобы на линии всегда работал только один активный выход, а все остальные выходы находились бы в это время в третьем состоянии, иначе возможны конфликты. Объединенные выходы ОК могут работать все одновременно, без всяких конфликтов.