- •Федеральное агентство по образованию Государственное образовательное учреждение высшего профессионального образования

- •Аннотация

- •1.2 Формат команд ту-тс

- •1.3 Выбор синхрокомбинации

- •I0(X) функция Бесселя нулевого порядка.

- •3.2 Помехоустойчивость при импульсной помехе

- •4 Расчет линии передачи

- •5.4 Аппаратура ип

- •5.4.1.2 Передатчик оа ип

- •5.4.2 Управляющий автомат ип (уа ип)

- •5.5 Аппаратура дп

- •5.5.1.2 Передатчик оа дп

- •5.5.2 Управляющий автомат дп (уа дп)

- •5.6 Внешний вид панели дп

- •Библиографический список

5.4.1.2 Передатчик оа ип

Принципиальная

схе ма

передатчика ОА ИП представлена на

рисунке 5.10:

ма

передатчика ОА ИП представлена на

рисунке 5.10:

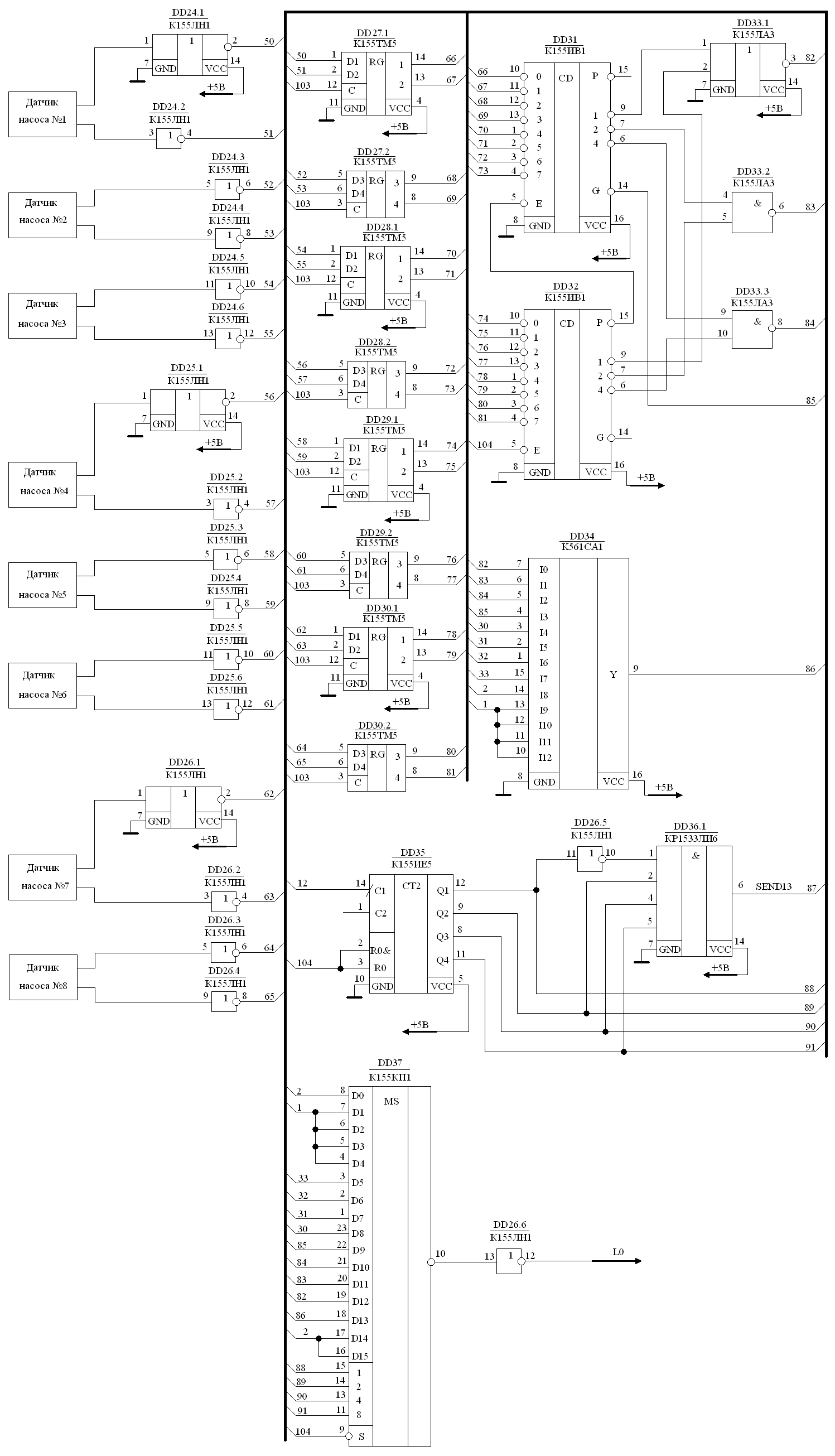

Рисунок 5.10 – Принципиальная схема передатчика ОА ИП

Рассмотрим принцип работы передатчика ОА ИП.

В

случае если произошло изменение состояния

какого-либо

ОУ, то соответствующий датчик регистрирует

данное изменение и по переднему фронту

импульса SA=1,

разрешающего передачу команды ТС в ЛС,

информация со всех датчиков ОУ запоминается

в соответствующем ЗУ, реализованном на

основе двухразрядного регистра. Если

ОУ был включен, то на выходе датчика мы

имеем 01, если был выключен, то на выходе

соответствующего датчика мы имеем 10, а

если же состояние датчика неизменно,

то на выходе датчика мы имеем 00.

какого-либо

ОУ, то соответствующий датчик регистрирует

данное изменение и по переднему фронту

импульса SA=1,

разрешающего передачу команды ТС в ЛС,

информация со всех датчиков ОУ запоминается

в соответствующем ЗУ, реализованном на

основе двухразрядного регистра. Если

ОУ был включен, то на выходе датчика мы

имеем 01, если был выключен, то на выходе

соответствующего датчика мы имеем 10, а

если же состояние датчика неизменно,

то на выходе датчика мы имеем 00.

Далее информация с ЗУ всех ОУ поступает на вход приоритетного шифратора, собранного на микросхемах DD31, DD32 и DD33. Появление сигнала SA=1 разрешает работу микросхем DD31 и DD32. С учетом того, что микросхемы DD31 и DD32 имеют инверсные входы, то и на выходе датчиков ОУ мы используем инверторы.

При помощи 13-разрядной схемы контроля четности К561СА1 (DD34) формируем контрольный бит проверки на четность. Формирование данного бита осуществляется согласно следующему алгоритму. Если код, состоящий из 4 бит команды ТС и 4 бит адреса ИП содержит нечетное количество единиц, то контрольный бит проверки на четность равен 1, иначе данный бит равен 0.

После выдачи в ЛС 13 бит информации (4 бита синхрокомбинации, 4 бита адреса ИП, 4 бита команды ТС и 1 контрольный бит проверки на четность) вырабатывается сигнал SEND13=1, сообщающий об окончании передачи команды ТС в ЛС. Отсчет 13 бит информации осуществляется при помощи четырехразрядного счетчика DD35, который срабатывает по переднему фронту синхроимпульсов CLK1. До прихода со стороны УА ИП сигнала SA=1, разрешающего передачу команды ТС в ЛС, счетчик DD35 удерживается в нулевом состоянии. И только после прихода сигнала SA=1 начинает счет синхроимпульсов, поступающих на его вход. Сигнал SEND13=1 выделяется конъюнктором DD36.1 на выходе счетчика.

Последовательная передача команды ТС в ЛС осуществляется при помощи мультиплексора DD37, на адресные входы которого подаются сигналы с выхода счетчика. Тем самым при поступлении на вход счетчика DD35 очередного синхроимпульса, значение данного счетчика увеличивается на единицу. И при этом на выход мультиплексора поступает информация со следующего по порядку входа.

5.4.2 Управляющий автомат ип (уа ип)

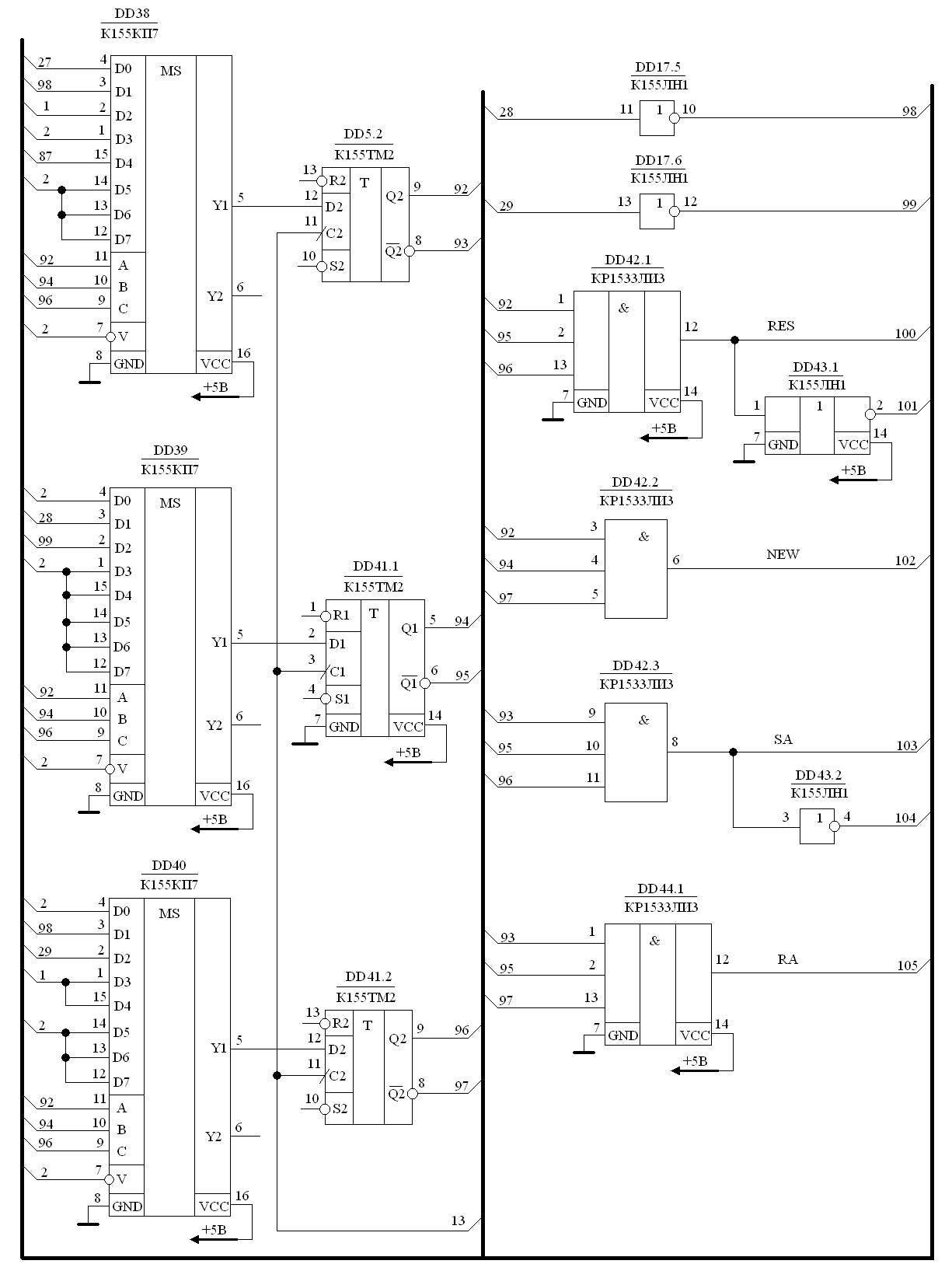

Принципиальная схема УА ИП представлена на рисунке 5.11:

Рисунок 5.11 – Принципиальная схема УА ИП

Рассмотрим

принцип работы управляющего авт омата

исполнительного пункта (УА ИП).

омата

исполнительного пункта (УА ИП).

Первоначально УА ИП находится в состоянии 000. После того, как счетчик DD14 ОА ИП отсчитает 9 бит принятой информации (4 бита адреса, 4 бита команды ТУ и один контрольный бит проверки на четность), со стороны ОА ИП вырабатывается сигнал READ9=1, который сигнализирует об окончании приема команды. Данный сигнал воздействует на УА ИП и переводит его в состояние 001. При этом со стороны УА ИП вырабатывается сигнал RA=0, который запрещает прохождение тактовых импульсов в приемный регистр.

Далее идет проверка совпадения 4-х адресных битов команды с адресом исполнительного пункта. Если данная проверка прошла успешно (принятая команда ТУ предназначалась именно данному ИП), то со стороны ОА ИП вырабатывается сигнал ADROK=1, который воздействует на УА ИП и переводит его в состояние 010. Если же проверка на совпадение адреса не прошла (принятая команда ТУ предназначалась другому ИП), то УА ИП переходит в состояние 101. При этом со стороны УА ИП формируется сигнал RES=1, который сбрасывает ВСК. При этом УА ИП возвращается в исходное нулевое состояние 000.

Далее автомат анализирует принятую команду на наличие ошибки путем проверки на четность. Если проверка на четность прошла успешно, т.е. ошибка отсутствует, то УА ИП переходит в состояние 011. При этом УА ИП формирует сигнал NEW=1, который разрешает запоминание принятой команды в двухразрядных регистрах DD20-DD23. В противном случае (проверка на четность не прошла) УА ИП переходит в состояние 101. При этом со стороны УА ИП формируется сигнал RES=1, который сбрасывает ВСК. При этом УА ИП возвращается в исходное нулевое состояние 000.

Далее УА ИП переходит в состояние 100. При этом формируется сигнал SA=1, разрешающий передачу команды ТС в ЛС. Данный сигнал выделяется конъюнктором DD42.3.

В состоянии 100 УА ИП находится до тех пор, пока не поступит сигнал SEND13=1, сообщающий о передаче 13 битов команды ТС в ЛС (4 бит синхрокомбинации, 4 адресных бита ИП, 4 бита команды ТС и 1 контрольный бит проверки на четность). После этого УА ИП переходит в состояние 101, где происходит выработка сигнала RES=1, который сбрасывает ВСК, а также счетчик DD14 приемной части ОА ИП И далее УА ИП возвращается в исходное нулевое состояние 000.

Блок-схема,

описывающая работу ИП п редставлена

на рисунке 5.12.

редставлена

на рисунке 5.12.

Рисунок 5.12 – Блок-схема работы ИП