- •Федеральное агентство по образованию Государственное образовательное учреждение высшего профессионального образования

- •Аннотация

- •1.2 Формат команд ту-тс

- •1.3 Выбор синхрокомбинации

- •I0(X) функция Бесселя нулевого порядка.

- •3.2 Помехоустойчивость при импульсной помехе

- •4 Расчет линии передачи

- •5.4 Аппаратура ип

- •5.4.1.2 Передатчик оа ип

- •5.4.2 Управляющий автомат ип (уа ип)

- •5.5 Аппаратура дп

- •5.5.1.2 Передатчик оа дп

- •5.5.2 Управляющий автомат дп (уа дп)

- •5.6 Внешний вид панели дп

- •Библиографический список

5.4 Аппаратура ип

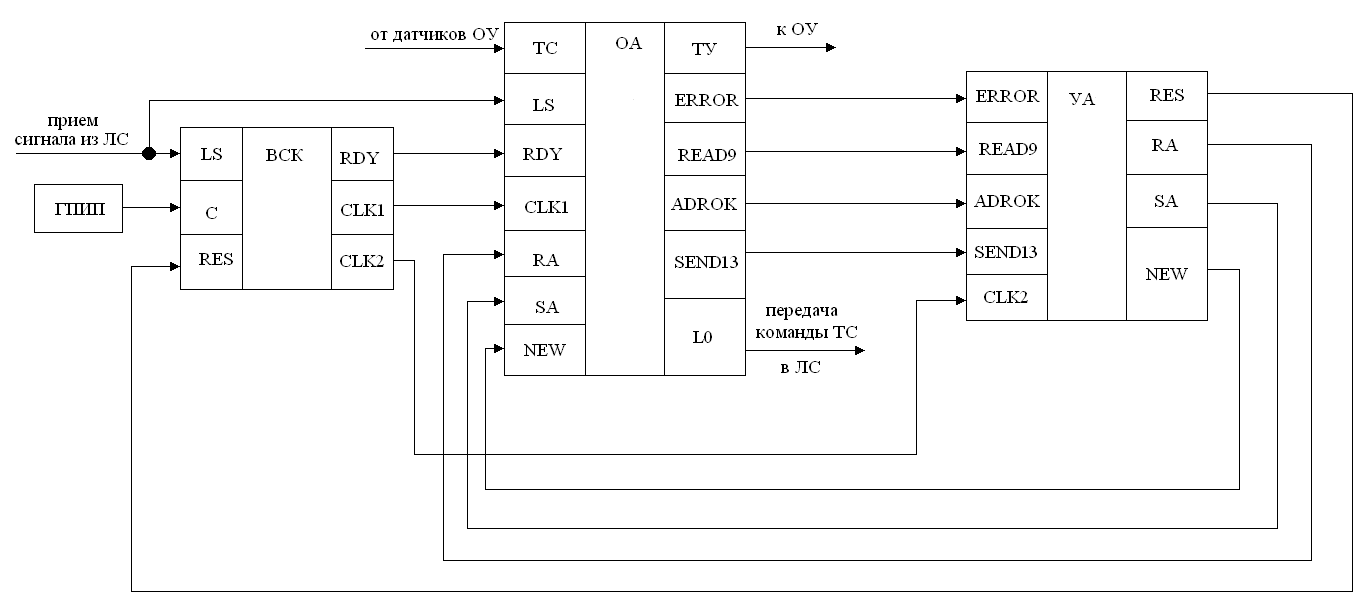

Функциональная схема цифрового автомата исполнительного пункта (ЦА ИП) представлена на рисунке 5.7.

Рисунок 5.7 – Функциональная схема ЦА ИП

На выше приведенной функциональной схеме приняты следующие сокращения:

LS – вход из линии связи;

L0 – выход в линию связи;

С – синхронизация триггеров и счетчика ВСК;

RES – сброс ВСК;

CLK1, CLK2 – синхросерии для операционного автомата (ОА) и управляющего автомата (УА) соответственно;

RDY – сигнал успешного приема синхрокомбинации;

RA – разрешение приема команды ТУ из ЛС для ОА;

SA – разрешение на передачу команды ТС в ЛС для ОА;

NEW – разрешение на запоминание новой принятой команды;

ERROR – сигнал наличия ошибки в принятой команде ТУ;

ADROK – сигнал соответствия переданного адреса адресу текущего ИП;

READ9 – сигнал об окончании приема команды ТУ из ЛС (принято 9 бит);

SEND13 – сигнал об окончании передачи команды ТС в ЛС (передано 13 бит);

При

появлении сигнала в ЛС ВСК проверяет

наличие необходимой синхрокомбинации

(1111) для того, чтобы быть уверенным, что

принимаемая информация это действительно

команда ТУ, а не помеха. При этом

вырабатывается сигнал RDY, сообщающий

ОА об успешном приеме синхрокомбинации.

С этого момента информация начинает

проходит на вход сдвигающего регистра,

преобразующего последовательный код

в параллельный и работающий по переднему

фронту тактового импульса CLK1.

Одновременно с этим запускается счетчик,

подсчитывающий количество принятых

бит информации. В нашему случае нам

необходимо принять 9 бит (4 бита адреса,

4 бита команды ТУ и 1 контрольны й

бит проверки на четность). После того,

как счетчик отсчитает 9 принятых битов

информации, формируется сигнал READ9=1.

Данный сигнал воздействует на УА, который

в свою очередь вырабатывает сигнал

RA=0, запрещающий прохождение тактовых

импульсов в приемный регистр.

й

бит проверки на четность). После того,

как счетчик отсчитает 9 принятых битов

информации, формируется сигнал READ9=1.

Данный сигнал воздействует на УА, который

в свою очередь вырабатывает сигнал

RA=0, запрещающий прохождение тактовых

импульсов в приемный регистр.

С этого момента начинается обработка принятой информации.

Сначала проверяется соответствие 4 адресных разрядов принятой команды адресу ИП. Если адреса совпадут, то вырабатывается сигнал ADROK=1. Если же проверка адреса завершилась неудачей, то УА ИП вырабатывает сигнал RES=1, который сбрасывает ВСК и обработка принятой команды прекращается.

После этого осуществляется проверка принятой команды на четность. Если проверка на четность прошла успешно, то 4 разряда команды ТУ запоминаются в регистре, с выходов которого затем передаются на дешифратор команд, выходы которого подключены непосредственно к ОУ. Если же проверка на четность завершилась неудачей, то вырабатывается сигнал ERROR=1, соответствующий сигналу ошибки. При этом УА ИП вырабатывает сигнал RES=1, который сбрасывает ВСК и обработка принятой команды прекращается.

Далее УА ИП вырабатывает сигнал SA=1, разрешающий передачу команды ТС в ЛС. После того как счетчик отсчитает 13 бит посланной информации (4 бита синхрокомбинации, 4 адресных бита ИП, 4 бита команды ТС и 1 контрольный бит проверки на четность), то ОА ИП формирует сигнал SEND13=1, сигнализирующий об окончании передачи команды ТС в ЛС. После этого УА ИП формирует сигнал RES=1, который сбрасывает ВСК.

На этом рабочий цикл аппаратуры ИП прекращается.

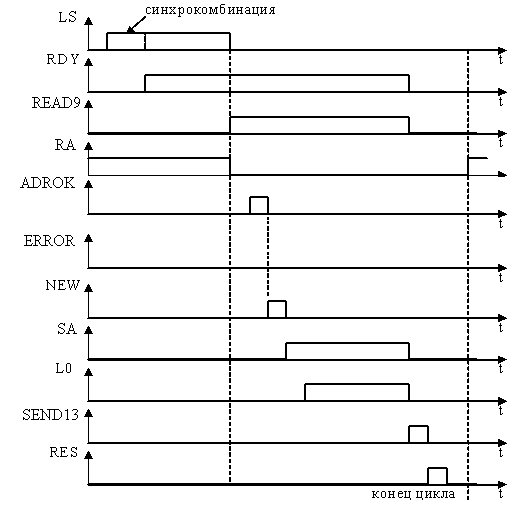

Временные

диаграммы работы аппаратуры ИП

пре дставлены

на рисунке 5.8:

дставлены

на рисунке 5.8:

Рисунок 5.8 – Временные диаграммы работы аппаратуры ИП

5.4.1

Операционный автомат ИП (ОА ИП)

5.4.1.1 Приемник ОА ИП

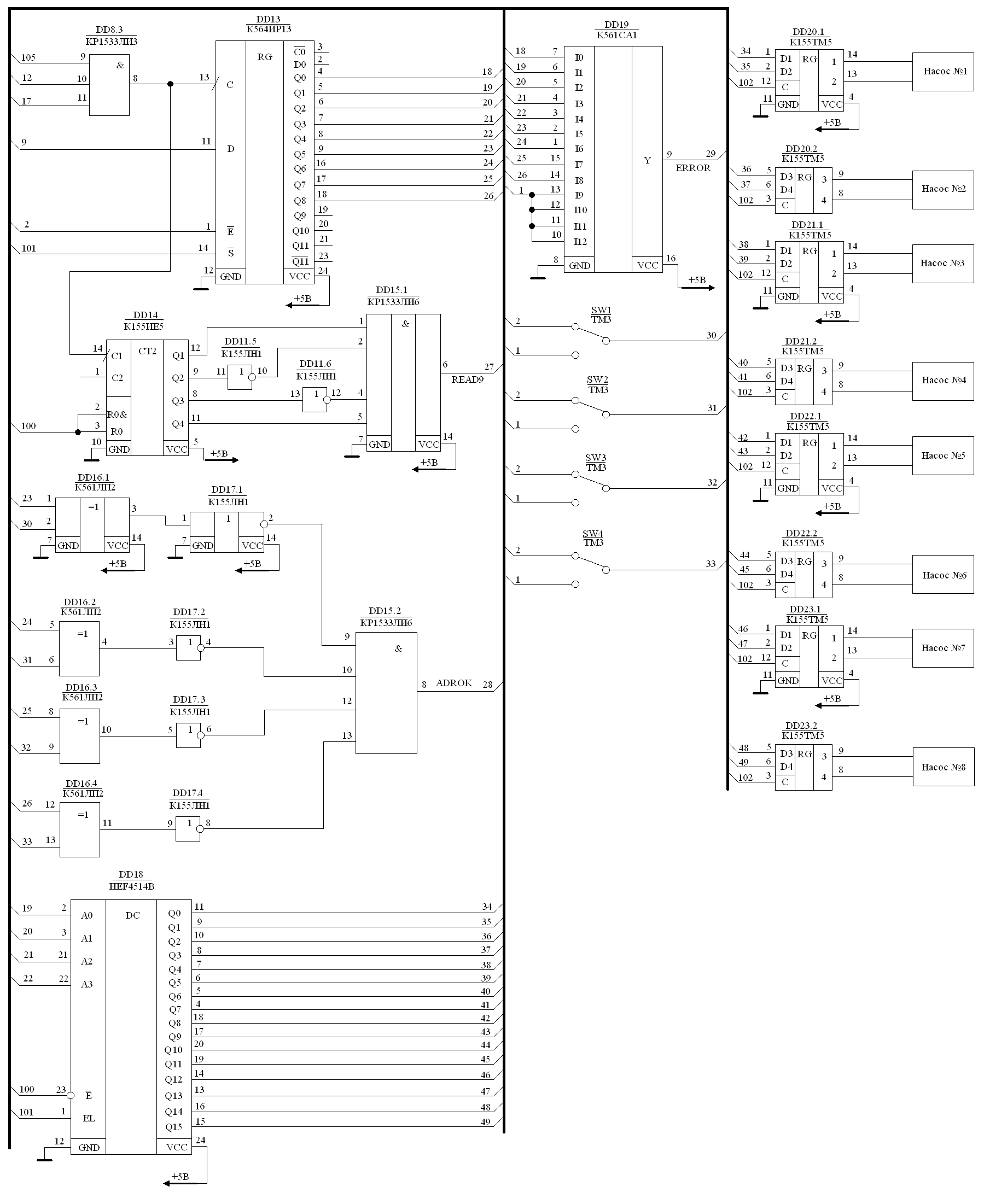

Принципиальная схема приемника ОА ИП представлена на рисунке 5.9.

Рисунок 5.9 – Принципиальная схема приемника ОА ИП

Рассмотрим принцип работы приемника ОА ИП.

Сигнал из линии связи поступает на вход сдвигающего регистра DD13, который преобразует последовательный код в параллельный и работает по нарастающему фронту тактового импульса CLK1. Серия синхроимпульсов CLK1 проходит на вход данного сдвигающего регистра только после удачного приема синхрокомбинации выявителем синхрокомбинации (на входе RDY ОА ИП появится логическая единица). При этом сигнал RA, разрешающий прохождение синхроимпульсов в приемный регистр DD13, равен 1. Сигнал RA вырабатывается управляющим автоматом (УА).

Одновременно

с этим при появлении сигнала RDY начинает

свою работу счетчик DD14. Счетчик DD14

предназначен для подсч ета

принятых битов. В данном случае нам

необходимо принять 9 бит (4 бита адреса,

4 бита команды телеуправления и 1

контрольный бит проверки на четность).

Счетчик DD14 срабатывает по переднему

фронту синхроимпульсов CLK1. После того

как счетчик отсчитает 9 бит принятой

информации, вырабатывается сигнал

READ9=1, сигнализирующий об окончании

приема. Сигнал READ9 выделяется конъюнктором

DD15.1

на выходе счетчика. Этот сигнал

воздействует на управляющий автомат

исполнительного пункта (УА ИП), который

вырабатывает сигнал RA=0. Данный сигнал

закрывает логический ключ, реализованный

на конъюнкторе DD8.3 и тем самым запрещает

прохождение тактовых импульсов в

приемный регистр DD13 и в счетчик DD14.

ета

принятых битов. В данном случае нам

необходимо принять 9 бит (4 бита адреса,

4 бита команды телеуправления и 1

контрольный бит проверки на четность).

Счетчик DD14 срабатывает по переднему

фронту синхроимпульсов CLK1. После того

как счетчик отсчитает 9 бит принятой

информации, вырабатывается сигнал

READ9=1, сигнализирующий об окончании

приема. Сигнал READ9 выделяется конъюнктором

DD15.1

на выходе счетчика. Этот сигнал

воздействует на управляющий автомат

исполнительного пункта (УА ИП), который

вырабатывает сигнал RA=0. Данный сигнал

закрывает логический ключ, реализованный

на конъюнкторе DD8.3 и тем самым запрещает

прохождение тактовых импульсов в

приемный регистр DD13 и в счетчик DD14.

С этого момента начинается обработка принятой информации.

Первоначально необходимо проверить предназначалась ли принятая команда телеуправления данному ИП. Для этого необходимо проверить соответствие четырех адресных разрядов принятого кода адресу данного ИП. Схема идентификации адреса построена на четырех элементах исключающее ИЛИ. Адрес исполнительного пункта задается при помощи четырех переключателей SW1, SW2, SW3 и SW4. Если все четыре адресных разряда соответствуют адресу ИП, то формируется сигнал ADROK=1, который выделяется конъюнктором DD15.2.

Контроль на четность реализована на микросхеме К561СА1 (13-разрядная схема контроля четности). Если проверка на четность прошла успешно, то на выходе Y данной микросхемы формируется низкий уровень сигнала. Если проверка на четность не прошла (нечетное количество пораженных битов принятой команды), то на выходе Y формируется высокий уровень сигнала, что соответствует сигналу ошибки ERROR.

Далее

код принятой команды поступает на

дешифратор команды ТУ DD18,

выходы которого идут к ЗУ объекта

управления. Данный дешифратор имеет

четыре адресных входа А0, А1, А2, А3, и 16 выходов.

А2, А3, и 16 выходов.

Каждый исполнительный пункт содержит по 8 ОУ (насосов), для каждого из которых предусмотрено две команды ТУ (включить и выключить). Для каждого насоса предусмотрено отдельное запоминающее устройство, реализованное на двухразрядном регистре. Запоминание команд в таких двухразрядных регистрах осуществляется при выработке со стороны УА сигнала NEW=1, разрешающего запомнить принятую команду. Таким образом команда 01 включает данный насос, а команда 10 выключает. Команда 00 не изменяет состояние насоса.