- •1.Расчитать минимальный коэффициент усиления выходного транзистора простейшего ттл вентиля.

- •2. Электрическая схема ттл вентиля со сложным инвертором.

- •3.Что такое таблица истинности. Функциональный контроль микросхем.

- •4. Способы включения биполярного транзистора как диода.

- •5.Принцип работы транзистора Шоттки.

- •7.Что такое радиочастотная идентификация. Диапазоны используемых частот в Европе.

- •8.Как влияет облучение на характеристики р-n перехода.

- •9.Что такое пинч-резистор?

- •10.Масштабирование. Основные принципы

- •11. Статическое электричество. Схема защиты от статического электричества.

- •12. Принцип работы транзистора в инверсном режиме

- •13. Первый и второй закон Мура.

- •14.Что такое потенциальные и импульсные схемы. Привести примеры.

- •15.Тиристор. Принцип работы

- •16.Туннельный диод Принцип работы.

- •17.Метод измерения динамических параметров интегральных схем.

- •18.Типы конденсаторов в интегральном исполнении

- •19. Виды полузаказных интегральных схем

- •Вентильные матрицы

- •2. Ис на основе готовых ячеек

- •1. Биполярные вентильныематрицы

- •20. Конструктивные и тепловые ограничения при проектировании интегральных схем

- •21. Модель Эберса-Молла биполярного транзистора

- •22. «Положительная» и «отрицательная» логика. Привести примеры

- •23. Способы включения биполярного транзистора.

- •24. Полевой транзистор. Принцип действия

- •25. Полевой транзистор с управляющим p-n переходом

- •26. Типы помех в интегральных схемах

- •27. Биполярный транзистор. Принцип работы

- •28. Зависимость потребляемой мощности кмоп вентиля от частоты.

- •29.Современные системы автоматической идентификации.

- •30. Формула вольт-амперной характеристики диода.

- •31. Полупроводниковые приборы с n - образными характеристиками.

- •32. Система параметров логических элементов.

- •34. Полупроводниковые приборы с отрицательным сопротивлением.

- •35. Способы включения биполярного транзистора и их конструктивные решения.

- •36. Конструкция и принцип работы многоэмиттерного транзистора.

- •37. Закон Мура. Степень интеграции интегральных схем.

- •38.Многослойные полупроводниковые структуры

- •39.Инжекционный вентиль. Принцип работы.

- •40.Расчет параметров интегрального резистора.

- •41.Формула коэффициента усиления биполярного транзистора.

- •42. Степень насыщения биполярного транзистора.

- •43. Чем отличается реальная вольтамперная характеристика р-п перехода от теоретической.

- •44. Как называются приборы, основанные на контакте металл-полупроводник.

- •45. Начертите схемы включения транзистора с общей базой, с общим эмиттером и с общим коллектором.

- •46. Нарисуйте схему устройства транзистора с изолированным затвором и объясните его принцип действия.

- •47. Объясните принцип действия динистора.

- •48. Назовите параметры тиристоров.

- •49.Что такое заказные и полузаказные интегральные схемы.

- •53. Нарисуйте передаточную характеристику логического вентиля, выполняющего функцию «инверсия».

- •Вопросы спиэ js_Edition

- •44. Как называются приборы, основанные на контакте металл-полупроводник.

- •45. Начертите схемы включения транзистора с общей базой, с общим эмиттером и с общим коллектором.

- •46. Нарисуйте схему устройства транзистора с изолированным затвором и объясните его принцип действия.

- •47. Объясните принцип действия динистора.

- •48. Назовите параметры тиристоров.

- •49.Что такое заказные и полузаказные интегральные схемы.

- •50.3Ависимость емкости конденсатора (мдп - процесс) от полярности подаваемого напряжения

- •51. Зависимость емкости конденсатора (мдп - процесс) от частоты.

- •52. Зависимость емкости конденсатора (биполярный тех.Процесс) от напряжения.

- •53. Нарисуйте передаточную характеристику логического вентиля, выполняющего функцию «инверсия».

- •54.Нарисуйте график зависимости мощности потребления от частоты для кмоп-схем.

- •54.Нарисуйте вертикальную структуру биполярного транзистора с диодом Шоттки.

- •55.Типы помех в интегральных схемах.

- •56.Принцип построения кольцевого генератора.

- •57.Принцип работы логического вентиля с тремя устойчивыми состояниями.

- •58.Нарисуйте вертикальную структуру р - п - р транзистора.

- •59. Нарисуйте вертикальную структуру р - п - р транзистора и п-р-п транзисторов изготовленных в одном техпроцессе.

- •60.Влияние температуры на параметры биполярного транзистора.

1.Расчитать минимальный коэффициент усиления выходного транзистора простейшего ттл вентиля.

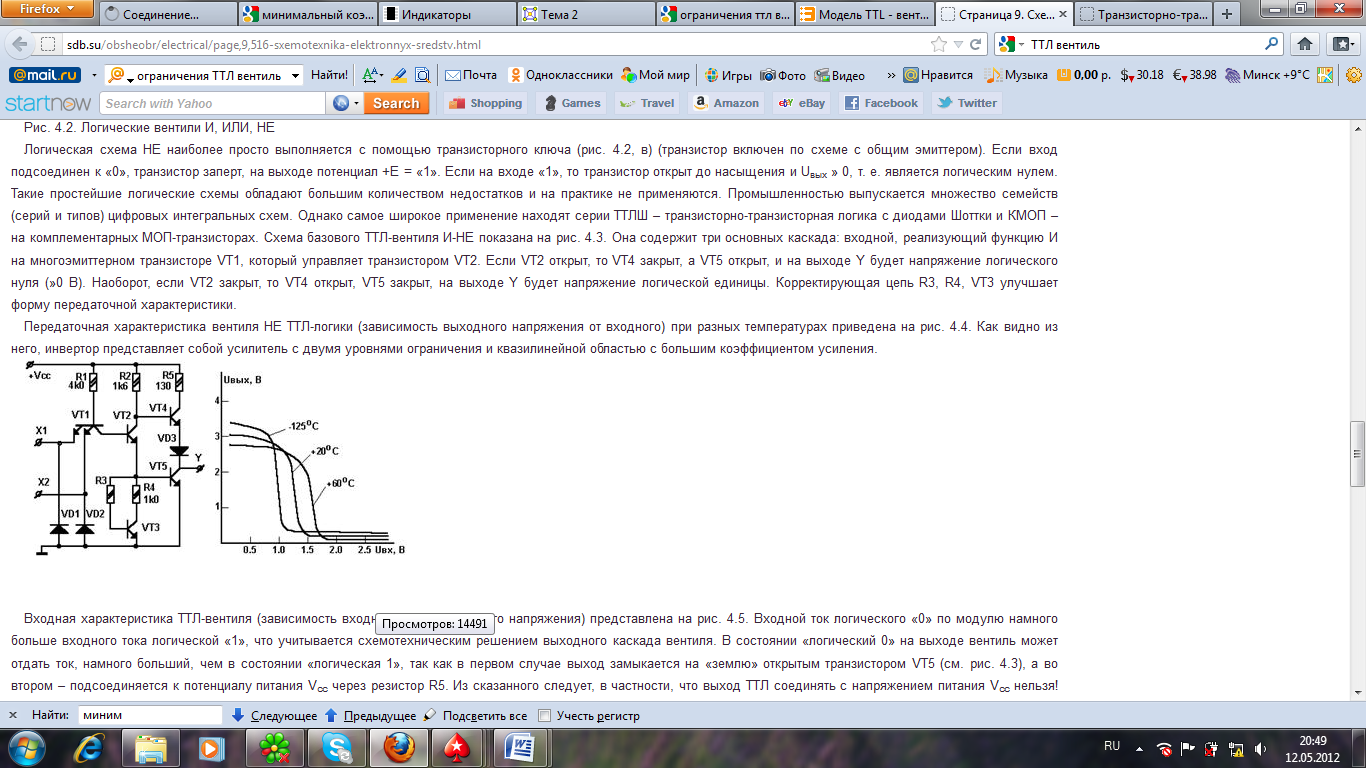

Слева ттл вентиль (И-не) справа, его передаточная характеристика. Минимамальный коэффициент усиления, для транзистора VT5 – при котором он равен b= Ik / Iб1

2. Электрическая схема ттл вентиля со сложным инвертором.

А- с простым, Б – сложным инвертором

Пример работы:

Если же на все эмиттеры транзистора VT1 подать напряжение Uвх1, равное примерно половине напряжения питания Uп, то эмиттерные токи VT1резко сократятся (входные токи лог.1), а базовый ток уйдет в коллектор, создавая на базе транзистора VT2 потенциал, близкий к потенциалу Uп. В таком случае транзистор VT2 фазоинверсного каскада откроется, запирая при этом VT4 и отпирая VT5. Включенный в коллекторную цепь VT4 диод VD5 создает при отпирании транзистора VT5 между базой и эмиттером VT4 разность потенциалов, меньшую напряжения отпирания VT4. Иными словами разность потенциалов между базой транзистора VT4 и выходом логического элемента распределяется между участком база-эмиттер VT4 и диодом VD5. Таким образом за счет полного запирания транзистора эмиттерного повторителя и насыщения транзистора VT5 на выходе ИС формируется уровень напряжения примерно равный 0.4В. Это напряжение есть напряжение насыщения транзистора VT5 и является выходным напряжением логического 0 Uвых0.

3.Что такое таблица истинности. Функциональный контроль микросхем.

Таблица истинности - таблица, в которой перечислены состояния на выходе при любой комбинации входных сигналов.

Функциональный контроль. Используется для проверки интегральных схем с

высокой степенью интеграции и включает в себя проведение статистических и

динамических измерений на базе контрольной тестовой таблицы, составленной,

например, с помощью ЭВМ с учетом минимизации количества входных кодовых

комбинаций. Функциональный контроль позволяет проводить проверку больших

интегральных микросхем в условиях, близких к эксплуатационным.

Принцип работы автоматизированной системы функционального контроля

интегральных микросхем с применением ЦВМ состоит в следующем.

По команде от ЦВМ в счетчик адреса памяти записывается начальный адрес

входных тестовых комбинаций, а в регистр адреса контролируемой тестовой

комбинации – соответствующий адрес. На компаратор подается от ЦВМ ожидаемая

комбинация входных сигналов. Несколько разрядов запоминающего устройства

входных тестовых комбинаций выделено для хранения определенного числа циклов

тактового генератора В течение периода хранения на входные выводы

интегральной схемы должна подаваться одна и та же тестовая комбинация. Число

циклов в обратном коде переписывается в счетчик повторений тестовых

комбинаций, на счетный вход которого поступают тактовые импульсы. При его

заполнении увеличивается содержимое счетчика адреса памяти и опрашивается

запоминающее устройство входных тестов по новому адресу. При равенстве адреса

счетчика памяти и регистра контролируемой комбинации прекращается подача

тактовых импульсов, компаратор стробируется по времени, фиксируя входные

импульсы последней тестовой комбинации.

Путем записи в регистр адреса контролируемой комбинации различных адресов

проверяется интегральная микросхема с динамической логикой на всех тестовых

комбинациях. Кроме указанных элементов система включает в себя схему

сравнения, схему выдачи входных воздействий и вентиль.

Наиболее эффективными методами контроля качества соединений являются

испытания на механическую прочность и металлографический анализ.