- •Состояние старт и стоп

- •Подтверждение

- •Адресация в шине i2c

- •Расширение i2c

- •Организация памяти.

- •Поясню на примере:

- •Арбитраж шины i2c.

- •Подтверждение

- •Адресация в шине i2c

- •Применение

- •I²c находит применение в устройствах, предусматривающих простоту разработки и низкую себестоимость изготовления при относительно неплохой скорости работы.

- •Разработка

- •1.2 Подключение микросхем к шине i2c с различным напряжением питания и совместимыми с 5в-ым напряжением линиями ввода-вывода

- •1.3 Микросхемы с различными логическими уровнями, подключенные через двунаправленный преобразователь уровня

- •1.3.1 Описание преобразования уровня

- •1.3.2 Защита каскада пониженного напряжения от выбросов повышенного напряжения

- •1.3.5 Усовершенствованная схема для изоляции выключенного каскада повышенного напряжения

- •2. Характеристики моп-ьранзисторов

- •3.2 Преобразование уровня с 5в до 3в

- •3.3 Осциллограммы сигналов при отключении питания шинных каскадов

Расширение i2c

Стандартная шина I2C со скоростью передачи данных 100 кбит/с и 7-битным адресом существует уже на протяжении более 10 лет в неизменном виде. Стандартная шина I2C принята повсеместно как стандарт для сотен типов микросхем, выпускаемых фирмой Philips и другими поставщиками. В настоящее время спецификация шины I2C расширена в двух направлениях : увеличение быстродействия и расширение адресного пространства для расширения номенклатуры вновь разрабатываемых устройств.

Введение спецификации "быстрого" режима, позволяющего в четыре раза увеличить скорость передачи данных до 400кБит\сек. Необходимость в этом "расширении" стандарта потребовалось из-за необходимости пересылки больших объемов информации, и, как следствие, необходимость увеличения пропускной способности канала.

Введение спецификации "10-битной адресации", позволяющая использовать 1024 дополнительных адресов, т.к. большинство из 112 адресов, допустимых при 7-битной адресации, уже были использованы более чем один раз. Для предотвращения проблем с размещением адресов новых устройств, желательно иметь большее количество адресных комбинаций. Примерно десятикратное увеличение количества доступных адресов получено при использовании новой 10-битной адресации.

Все новые устройства с I2C интерфейсом работают в быстром режиме. Предпочтительно, они должны уметь принимать и/или передавать данные на скорости 400 кбит/с. Как минимум они должны быть способны входить в синхронизацию в быстром режиме, с тем чтобы снизить скорость передачи (путем удлиннения НИЗКОГО периода SCL) до допустимой величины.

Быстрые устройства как правило совместимы снизу-вверх, что означает их способность работать со стандартными устройствами по медленной шине. Очевидно, что стандартные устройства не способны работать в быстрой шине, потому что они не могут синхронизироваться на высокой скорости и их состояние станет непредсказуемым. Ведомые быстрые устройства могут обладать как 7-битным, так и 10-битным адресом. Однако, 7-битный адрес более предпочтителен, так как его аппаратная реализация более проста и длина посылки меньше. Устройства с 7-битным и 10-битным адресами могут одновременно использоваться на одной шине, независимо от скорости передачи. Как существующие, так и будущие ведущие смогут генерировать и 7-битные, и 10-битные адреса.

В быстром режиме протокол, формат, логические уровни и максимальная емкостная нагрузка линий шины остается неизменными. Алгоритм синхронизации линий SDA и SCL не изменен. Однако, от "быстрых" устройствне требуется совместимости с CBUS-устройствами, так как они не могут работать на высоких скоростях. Входные цепи быстрых устройств должны иметь встроенное подавление выбросов и триггер Шмитта на обоих линиях Выходной буфер быстрых устройств должен иметь каскад с управлением временем заднего фронта линий SDA и SCL. Как правило при пропадании напряжения питания быстрых устройств выводы, подключенные к линиям I2C шины должны переходить в третье состояние . Претерпели изменения схемотехнические решения выходных каскадов для обеспечения времени нарастания переднего фронта (переход из НИЗКОГО состояния в ВЫСОКОЕ). Если для нагрузок шины до 200 пФ эту роль выполняют подтягивающие резисторы, то для нагрузок от 200 пФ до 400 пФ эту функцию выполняет источник тока или схема на переключаемых резисторах, обеспечивающая "форсированое" переключение линий I2C шины.

10-битная адресация также не изменяет формат шины. Для этого используется зарезервированная адресная комбинация 1111ХХХ первых семи бит первого байта. 10-битная адресация не влияет на существующую 7-битную адресацию. Устройства с 7-битной и 10-битной адресацией могут быть подключены к одной шине. Хотя имеются восемь возможных комбинаций последовательности 1111ХХХ, из них используются только четыре - 11110ХХ. Комбинации типа 11111ХХ зарезервированы для дальнейших улучшений шины. Назначение битов первых двух байтов 10-битный адрес формируется из первых двух байтов. Первые семь бит первого байта являются комбинацией вида 11110ХХ, где два младших бита (ХХ) являются двумя старшими (9 и 8) битами 10-битного адреса; восьмой бит первого байта - бит направления. "Ноль" в этом бите означает, что ведущий собирается записывать информацию в ведомого, а "единица" - что ведущий будет считывать информацию из ведомого. Если бит направления равен "нулю", то второй байт содержит оставшиеся 8 бит 10-битного адреса. Если бит направления равен "единице", то следующий байт содержит данные, переданные с ведомого ведущему.

В заключение следует отметить, что стандарт I2C шины достаточно просто реализует арбитраж столкновений - решает проблему одновременной инициализации обмена по шине несколькими ведущими, при этом без потери данных.

Вся передача данных состоит из Стартовой посылки, битов и стоповой посылки. Порядок изменения уровня на шинах задает тип посылки.

После старта передача одного бита данных идет по тактовому импульсу. То есть когда линия SCL в нуле master или slave выставляют бит на SDA (прижимают — если 0 или не прижимают — если 1 линию SDA) после чего SCL отпускается и master/slave считывают бит. Таким образом, у нас протокол совершенно не зависит от временных интервалов, только от тактовых битов. Поэтому шину I2C очень легко отлаживать — если что то не так, то достаточно снизить скорость до байта в минуту и спокойно, обычными вольтметрами, смотреть что у нас происходит. Правда это не прокатит с железным I2C, там нет таких низких скоростей. Но что нам мешает затактовать микроконтроллер от ОЧЕНЬ медленного тактового генератора и отладить все по шагам? ;)

Начало передачи определяется Start-последовательностью — провал SDA при высоком уровне SCL

При передаче информации от Master к Slave, ведущий генерирует такты на SCL и выдает биты на SDA. Которые ведомый считывает когда SCL становится 1.

При передачи информации от Slave к Master, ведущий генерирует такты на SCL и смотрит что там ведомый творит с линией SDA — считывает данные. А ведомый, когда SCL уходит в 0, выставляет на SDA бит, который мастер считывает когда поднимет SCL обратно.

Заканчивается все STOP-последовательностью. Когда при высоком уровне на SCL линия SDA переходит с низкого на высокий уровень.

То есть, изменение на шине данных в момент приема данных может быть только при низком уровне на SCL. Когда SCL вверху то идет чтение. Если же у нас SDA меняется при высоком SCL, то это уже служебные команды START или STOP.

I2C

Физический уровень. Данные передаются по двум проводам — провод данных и провод тактов. Есть ведущий(master) и ведомый (slave), такты генерирует master, ведомый лишь поддакивает при приеме байта. Всего на одной двупроводной шине может быть до 127 устройств. Схема подключения — монтажное И

|

Передача/Прием сигналов осуществляется прижиманием линии в 0, в единичку устанавливается сама, за счет подтягивающих резисторов. Их ставить обязательно всегда! Стандарт! Резисторы на 10к оптимальны. Чем больше резистор, тем дольше линия восстанавливается в единицу (идет перезаряд паразитной емкости между проводами) и тем сильней заваливаются фронты импульсов, а значит скорость передачи падает. Именно поэтому у I2C скорость передачи намного ниже чем у SPI. Обычно IIC работает либо на скорости 10кбит/с — в медленном режиме, либо на 100кбит/с в быстром. Но в реальности можно плавно менять скорость вплоть до нуля.Ни в коем случае нельзя переключать вывод микроконтроллера в OUT и дергать ногу на +5. Можно запросто словить КЗ и пожечь либо контроллер либо какой-нибудь девайс на шине. Мало ли кто там линию придавит.

Вся передача данных состоит из Стартовой посылки, битов и стоповой посылки. Порядок изменения уровня на шинах задает тип посылки.

|

|

После старта передача одного бита данных идет по тактовому импульсу. То есть когда линия SCL в нуле master или slave выставляют бит на SDA (прижимают — если 0 или не прижимают — если 1 линию SDA) после чего SCL отпускается и master/slave считывают бит. Таким образом, у нас протокол совершенно не зависит от временных интервалов, только от тактовых битов. Поэтому шину I2C очень легко отлаживать — если что то не так, то достаточно снизить скорость до байта в минуту и спокойно, обычными вольтметрами, смотреть что у нас происходит. Правда это не прокатит с железным I2C, там нет таких низких скоростей. Но что нам мешает затактовать микроконтроллер от ОЧЕНЬ медленного тактового генератора и отладить все по шагам? ;)

Повторим для ясности:

Начало передачи определяется Start последовательностью — провал SDA при высоком уровне SCL

При передаче информации от Master к Slave, ведущий генерирует такты на SCL и выдает биты на SDA. Которые ведомый считывает когда SCL становится 1.

При передачи информации от Slave к Master, ведущий генерирует такты на SCL и смотрит что там ведомый творит с линией SDA — считывает данные. А ведомый, когда SCL уходит в 0, выставляет на SDA бит, который мастер считывает когда поднимет SCL обратно.

Заканчивается все STOP последовательностью. Когда при высоком уровне на SCL линия SDA переходит с низкого на высокий уровень.

То есть, изменение на шине данных в момент приема данных может быть только при низком уровне на SCL. Когда SCL вверху то идет чтение. Если же у нас SDA меняется при высоком SCL, то это уже служебные команды START или STOP.

|

Если Slave торомоз и не успевает (у EEPROM, например, низкая скорость записи), то он может насильно положить линию SCL в землю и не давать ведущему генерировать новые такты. Мастер должен это понять и дать слейву прожевать байт. Так что нельзя тупо генерить такты, при отпускании SCL надо следить за тем, что линия поднялась. Если не поднялась, то надо остановиться и ждать до тех пор, пока Slave ее не отпустит. Потом продолжить с того же места.

|

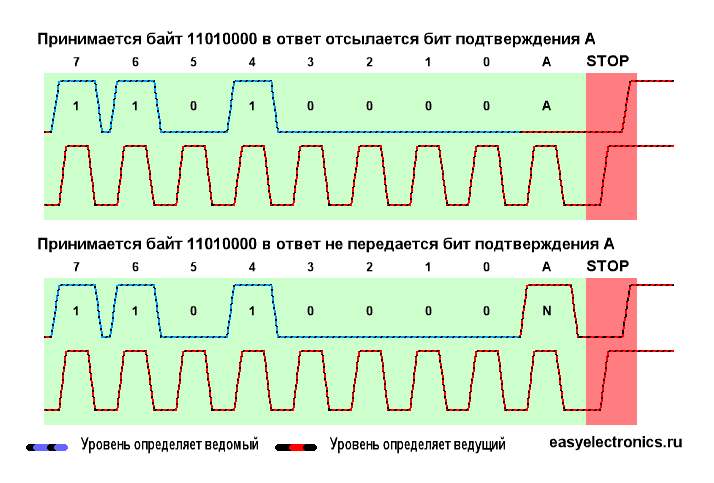

Логический уровень Как передаются отдельные биты понятно, теперь о том что эти биты значат. В отличии от SPI тут умная адресная структура. Данные шлются пакетами, каждый пакет состоит из девяти бит. 8 данных и 1 бит подтверждения/не подтверждения приема.

Первый пакет шлется от ведущего к ведомому это физический адрес устройства и бит направления.

|

Сам адрес состоит из семи бит (вот почему до 127 устройств на шине), а восьмой бит означает что будет делать Slave на следующем байте — принимать или передавать данные. Девятым битом идет бит подтверждения ACK. Если Slave услышал свой адрес и считал полностью, то на девятом такте он придавит линию SDA в 0, сгенерировав ACK — то есть Понял! Мастер, заметя это, понимает, что все идет по плану и можно продолжать. Если Slave не обнаружился, прозевал адрес, неправильно принял байт, сгорел или еще что с ним случилось, то, соответственно, SDA на девятом такте будет прижать некому и ACK не получится. Будет NACK. Мастер с горя хлопнет водки и прекратит свои попытки до лучших времен.

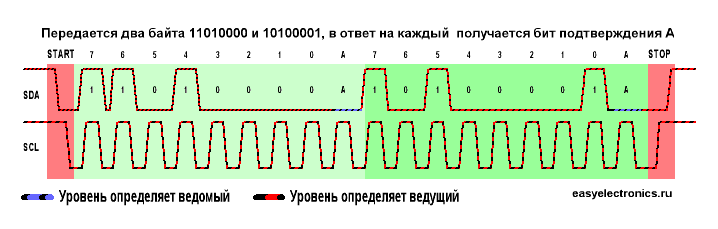

После адресного пакета идут пакеты с данными в ту или другую сторону, в зависимости от бита RW в заголовочном пакете. Вот, например, Запись. В квадратиках идут номера битов. W=0

|

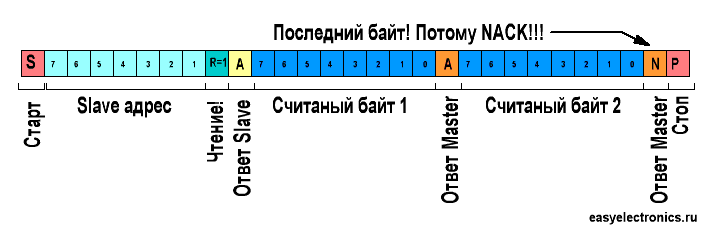

Чтение практически также, но тут есть одна тонкость из-за которой я когда то убил кучу времени. При приеме последнего байта надо дать ведомому понять, что в его услугах больше не нуждаемся и отослать NACK на последнем байте. Если отослать ACK то после стопа Master не отпустит линию — такой уж там конечный автомат. Так что прием двух байтов будет выглядеть так (R=1):

|

Есть еще одно состояние, как повторный старт. Это когда мы не обьявляя STOP вкатываем на шину еще один START. После него мы можем обратиться к другому устройству не освобождая шину. Но чаще идет обращение к тому же самому устройству и это связано с особенностями организации памяти.