- •Состояние старт и стоп

- •Подтверждение

- •Адресация в шине i2c

- •Расширение i2c

- •Организация памяти.

- •Поясню на примере:

- •Арбитраж шины i2c.

- •Подтверждение

- •Адресация в шине i2c

- •Применение

- •I²c находит применение в устройствах, предусматривающих простоту разработки и низкую себестоимость изготовления при относительно неплохой скорости работы.

- •Разработка

- •1.2 Подключение микросхем к шине i2c с различным напряжением питания и совместимыми с 5в-ым напряжением линиями ввода-вывода

- •1.3 Микросхемы с различными логическими уровнями, подключенные через двунаправленный преобразователь уровня

- •1.3.1 Описание преобразования уровня

- •1.3.2 Защита каскада пониженного напряжения от выбросов повышенного напряжения

- •1.3.5 Усовершенствованная схема для изоляции выключенного каскада повышенного напряжения

- •2. Характеристики моп-ьранзисторов

- •3.2 Преобразование уровня с 5в до 3в

- •3.3 Осциллограммы сигналов при отключении питания шинных каскадов

2. Характеристики моп-ьранзисторов

Ниже представлены требования к наиболее важным характеристикам МОП-транзисторов, используемых в качестве двунаправленных преобразователей уровней в шинных системах I2C с максимальными уровнями 6В и минимальными 2,7В. Значения приведены для справки и могут быть адаптированы под другие напряжения питания, логические уровни и/или другие применения.

Тип: N-канальный МОП-транзистор с режимом обогащения

Пороговое напряжение затвора: VGS(th) |

не менее 0.1В, не более 2В |

Сопротивление открытого канала: RDS(on) |

не более 100 Ом при токе стока ID= 3 мА, VGS= 2.5В |

Входная емкость: Ciss |

не более 100 пФ при VDS= 1В, VGS = 0В |

Время переключения: ton toff |

не более 50 нс |

Допустимый ток стока: ID |

10 мА или более |

Номиналы подтягивающих резисторов и последовательных резисторов здесь не приводятся, они зависят от наихудших уровней напряжения питания и логических уровней, протяженности и загруженности линий шины, а также требований по временам нарастания и спада фронтов. Номиналы данных резисторов необходимо рассчитать для каждой шинной системы отдельно. Хорошим подходом для расчета является поддержание примерно одинаковых значений RC различных каскадов; это позволяет достичь минимальных расхождений во временах установления и удержания.

В таблице 1 представлены МОП-транзисторы, которые могут использоваться в преобразователе уровней. В справочнике SC07 компании Philips представлены полные характеристики данных транзисторов. BSN10 или BSN20 - недорогие транзисторы, которые обладают хорошими характеристиками для преобразования уровней 3В/5В, изоляции и защиты.

Таблица 1

Тип транзистора |

VGS(th) |

RDS(on) |

Ciss |

Корпус |

BSN10 |

не менее 0.4В не более 1.8В |

25 Ом (тип.) |

15 пФ |

TO-92 |

BSN20 |

не менее 0.4В не более 1.8В |

25 Ом (тип.) |

15 пФ |

SOT23 |

BSS83 |

не менее 0.1В не более 2.0В |

70 Ом (тип.) |

1.5 пФ (тип.) |

SOT143 |

BSS88 |

не менее 0.4В не более 1.2В |

15 Ом |

50 пФ (тип.) |

TO-92 |

3. Осциллограммы логических уровней

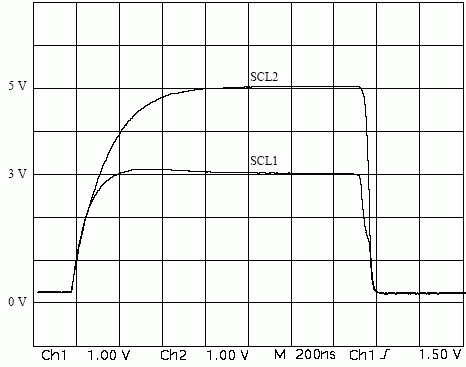

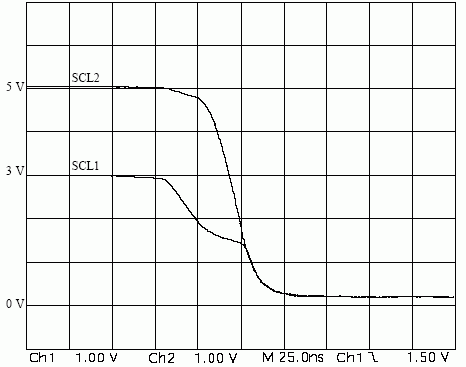

На рисунках 4, 5, 6, 7 и 8 представлены осциллограммы логических уровней для схемы на рисунке 2. На рисунке 9 представлены осциллограммы сигналов для схемы на рисунке 3. В качестве МОП-транзисторов T1, T2, T3 и T4 используется BSN10. В каскаде пониженного напряжения номинал Rp равен 3,3 кОм, емкость линии шины равна 50 пФ, а в каскаде повышенного напряжения - 4,7 кОм и 30 пФ, соответственно. Показаны осциллограммы только для линий синхронизации SCL. У управляющих микросхем выполняется управление падающим фронтом на выходах. Длительность падающего фронта до 50 нс.

3.1 Преобразование уровня с 3В до 5В

Рисунок

4. Преобразование уровня с 3В до 5В (200

нс/дел.)

Рисунок

4. Преобразование уровня с 3В до 5В (200

нс/дел.)

Рисунок

5. Падающий фронт с рисунка 4 в увеличенном

масштабе (25 нс/дел.)

Рисунок

5. Падающий фронт с рисунка 4 в увеличенном

масштабе (25 нс/дел.)

На рисунке 4 показано преобразование уровня из каскада пониженного напряжения в каскад повышенного напряжения с временным масштабом 200 нс/дел. 3В-ая микросхема управляет линией SCL1 и форма этого сигнала смещается к 5В-ому уровню на линии SCL2. При нарастании фронта на уровне приблизительно 2В МОП-транзистор отключается и уровни в каждом каскаде плавно нарастают по своей собственной кривой до конечного значения. На рисунке 5 показана форма падающего фронта в увеличенном масштабе (развертка 25 нс/дел.). На уровне около 2В во время падающего фронта SCL1 МОП-транзистор переходит в проводящее состояние и соединяет обе линии шинных каскадов. На это затрачивается примерно 25 нс (см. отрезок от 100 до 125 нс по оси времени), что объясняется необходимостью разряда линии SCL2 до достижения уровня линии SCL1. Этим демонстрируется увеличение длительности спада уровня на линии SCL1, но оно находится в допустимых пределах в соответствии с требованиями шины I2C (300 нс). После этого, напряжения на линиях SCL1 и SCL2 плавно снижаются до низкого уровня.

Емкостная связь через МОП-транзистор между SCL1 и SCL2 оказывает некоторое отрицательное влияние на форму сигналов:

небольшой выброс на SCL1 в процессе нарастания фронта SCL2 (рисунок 4),

замедление в начале падающего фронта SCL2, вызванное спаданием фронта SCL1 (рисунок 5).