- •1. Принципи цифрового управління технологічними об'єктами

- •1.1. Класифікація та склад систем управління

- •1.2. Способи управління технологічними об'єктами

- •1.3. Методи вибору періоду квантування

- •1.4. Типові алгоритми бцу

- •4. Способи управління технологічними об'єктами.

- •2. Засоби спряження з об'єктом

- •2.1. Технологічні процеси як об'єкти управління

- •Матриця планування

- •2.2. Пристрої отримання інформації

- •2.3. Перетворення вихідних сигналів датчиків

- •2.4. Аналого-цифрові та цифро-аналогові перетворювачі

- •3. Мп засоби систем управління

- •3.1. Інтерфейси систем управління

- •3.2. Організація паралельного інтерфейсу

- •3.3. Організація послідовного інтерфейсу

- •3.4. Елементи, що задають час

- •3.5. Організація режиму переривання

- •3.6. Елементи захисту інформації

- •4. Синтез систем логічного управління

- •Питання для самоконтролю

- •Рекомендована література

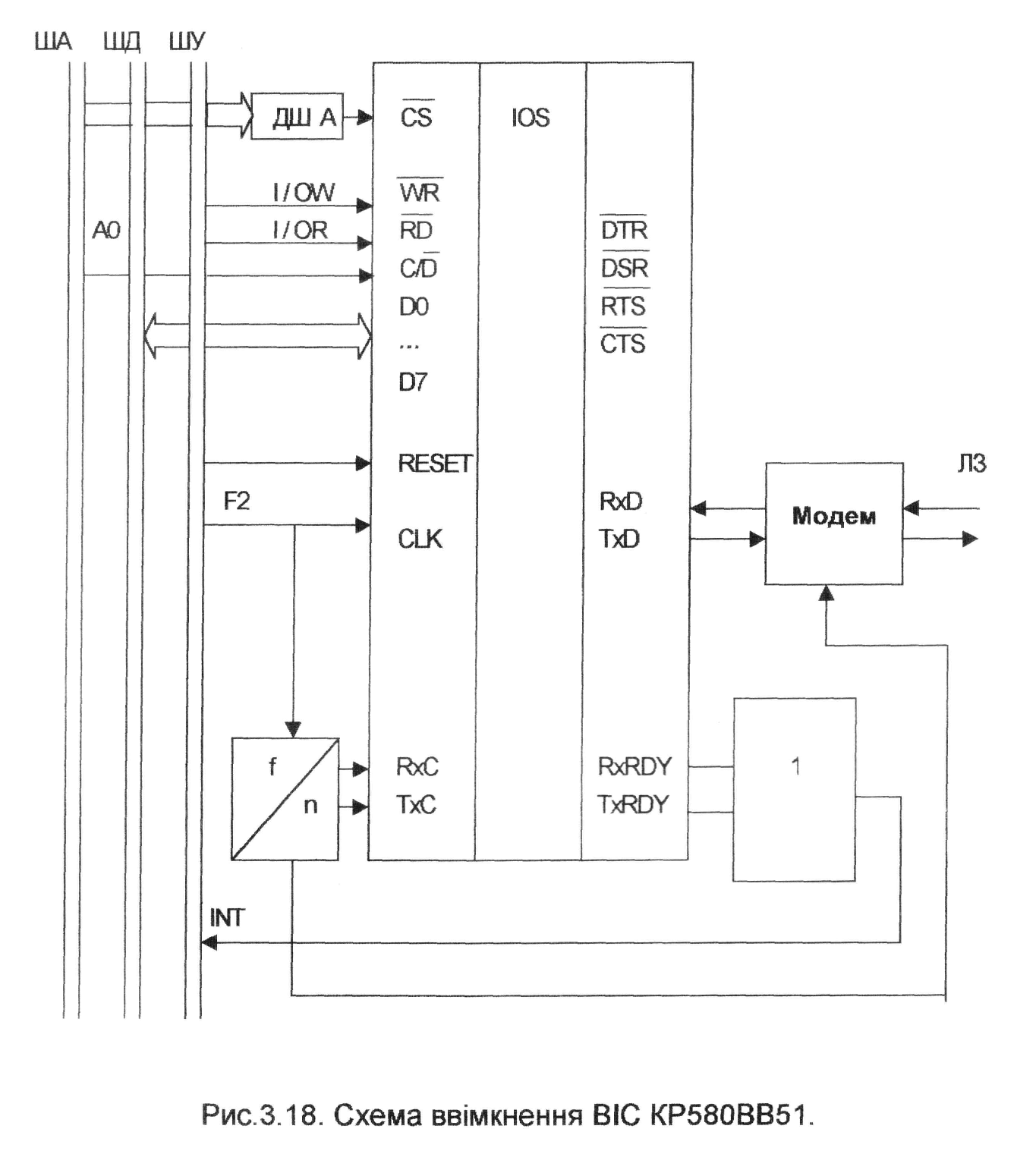

3.3. Організація послідовного інтерфейсу

Послідовний інтерфейс характеризується тим, що передача проходить по одній лінії зв'язку, причому біти, що складають слово, передаються один за одним. Звичайна швидкість передачі даних складає:

• 110 та 300 біт/с для телетайпу;

• 1200; 2400; 4800; 9600 біт/с - для ЕОМ.

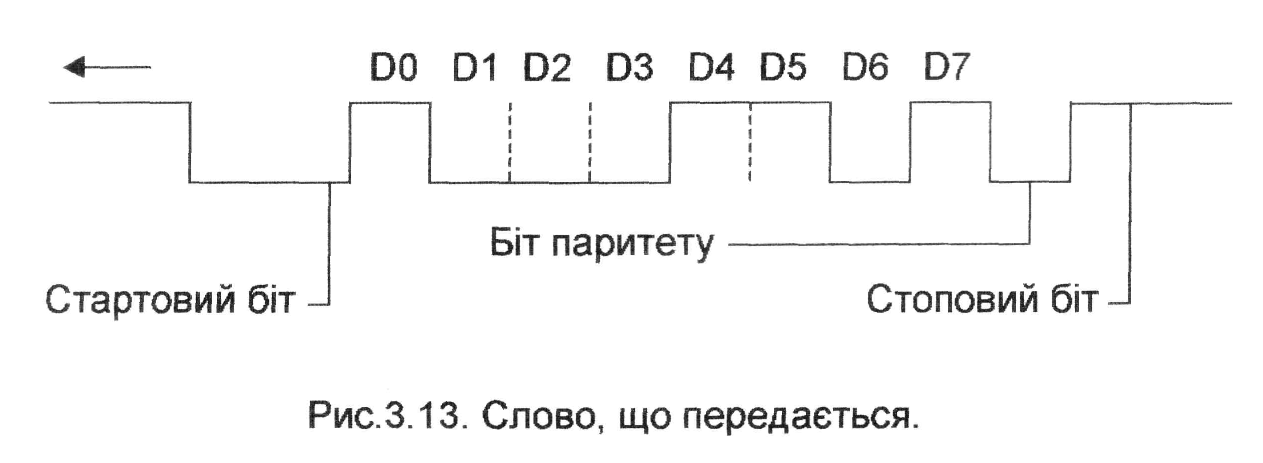

Розглянемо, як здійснюється прийом і розпізнавання даних, які передали. Припустимо, що передається слідуюча комбінація 10110001.

Першим передається DO. Лінія за відсутності передачі, припустимо, знаходилась у стані логічної 1. Коли 00=1, то момент початку передачі даних буде пропущений. Тому до слова, що передається, додають додаткові стартові біти, що інформують приймаючий пристрій про початок передачі. Стан стартового біта протилежний стану лінії в режимі очікування.

Крім стартового біта до інформації, що передається кодовою комбінацією, додаються:

• біт паритету контролю правильності прийому;

• столовий біт для позначення закінчення прийому. Тоді повне цифрове слово складе (рис.3.13):

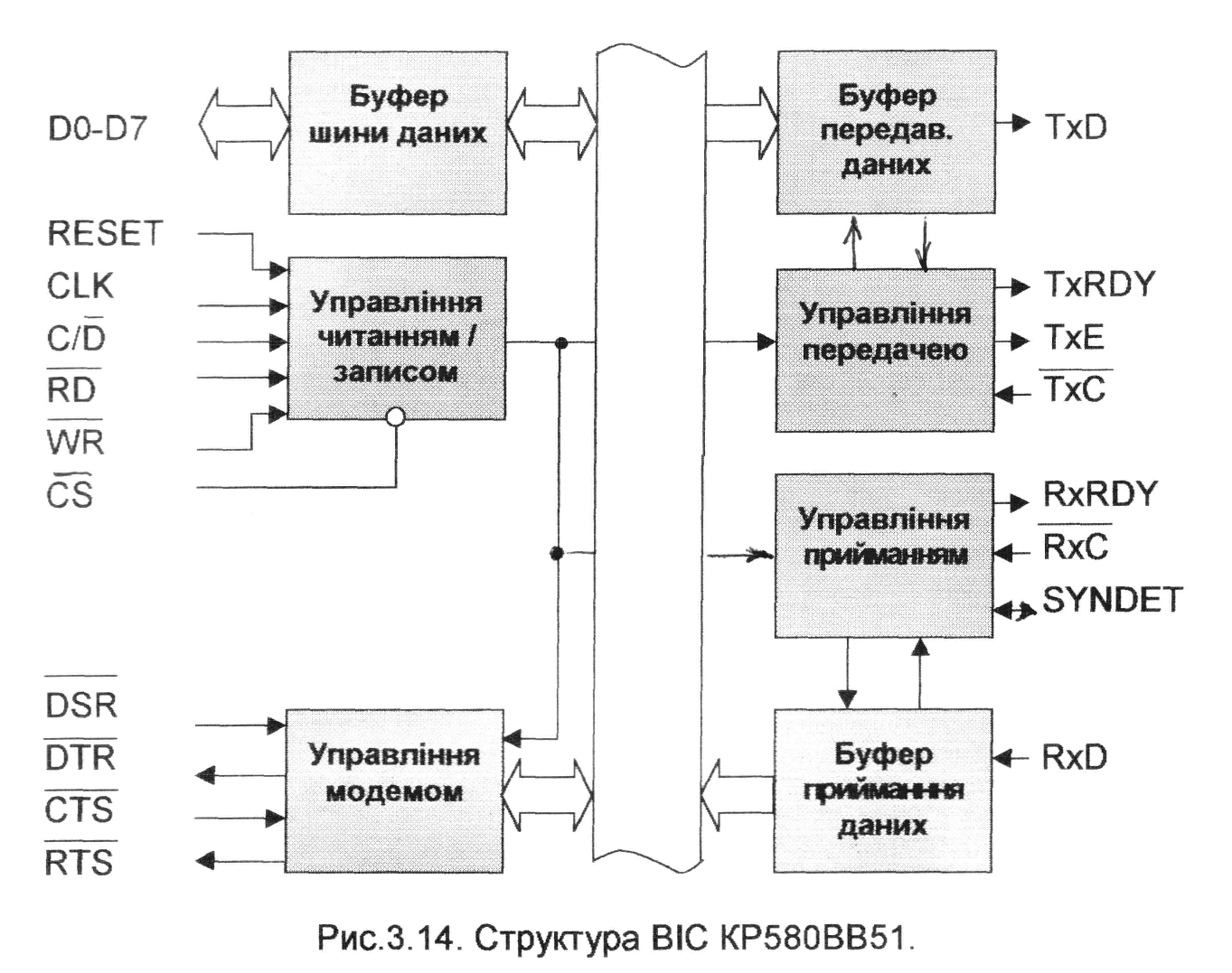

Для полегшення організації послідовних ліній зв'язку розроблена спеціалізована інтегральна схема: універсальний синхронно-асинхронний приймач-передавач (УСАПП).

Структурна схема ВІС КР580ВВ51 наведена на рис.3.14.

75

![]() -

управління/дані;

«1»

- записується

управляюче

слово

чи

слово

стану;

«0»

- записуються

чи

читаються

дані.

-

управління/дані;

«1»

- записується

управляюче

слово

чи

слово

стану;

«0»

- записуються

чи

читаються

дані.

![]() -

вх.

готовність

модему.

-

вх.

готовність

модему.

![]() -

вих.

готовність

прийняти

інформацію.

-

вих.

готовність

прийняти

інформацію.

![]() -

вх.

дозвіл

передати

інформацію.

-

вх.

дозвіл

передати

інформацію.

![]() -

вих.

готовність

передати

інформацію.

-

вих.

готовність

передати

інформацію.

TxD - вихідна лінія мікросхеми.

TxRDY - готовність блоку до запису коду по шині даних.

ТхЕ - вих. закінчення видачі коду із регістру блока «1», «0» - при запису кода.

![]() -

синхронізація

блоку

передачі.

-

синхронізація

блоку

передачі.

RxRDY - вих. готовність блоку до читання коду по шині даних.

![]() -

синхронізація

блоку

прийому.

-

синхронізація

блоку

прийому.

SYNDET - вих./вх.

RxD - послідовний вхід.

76

77

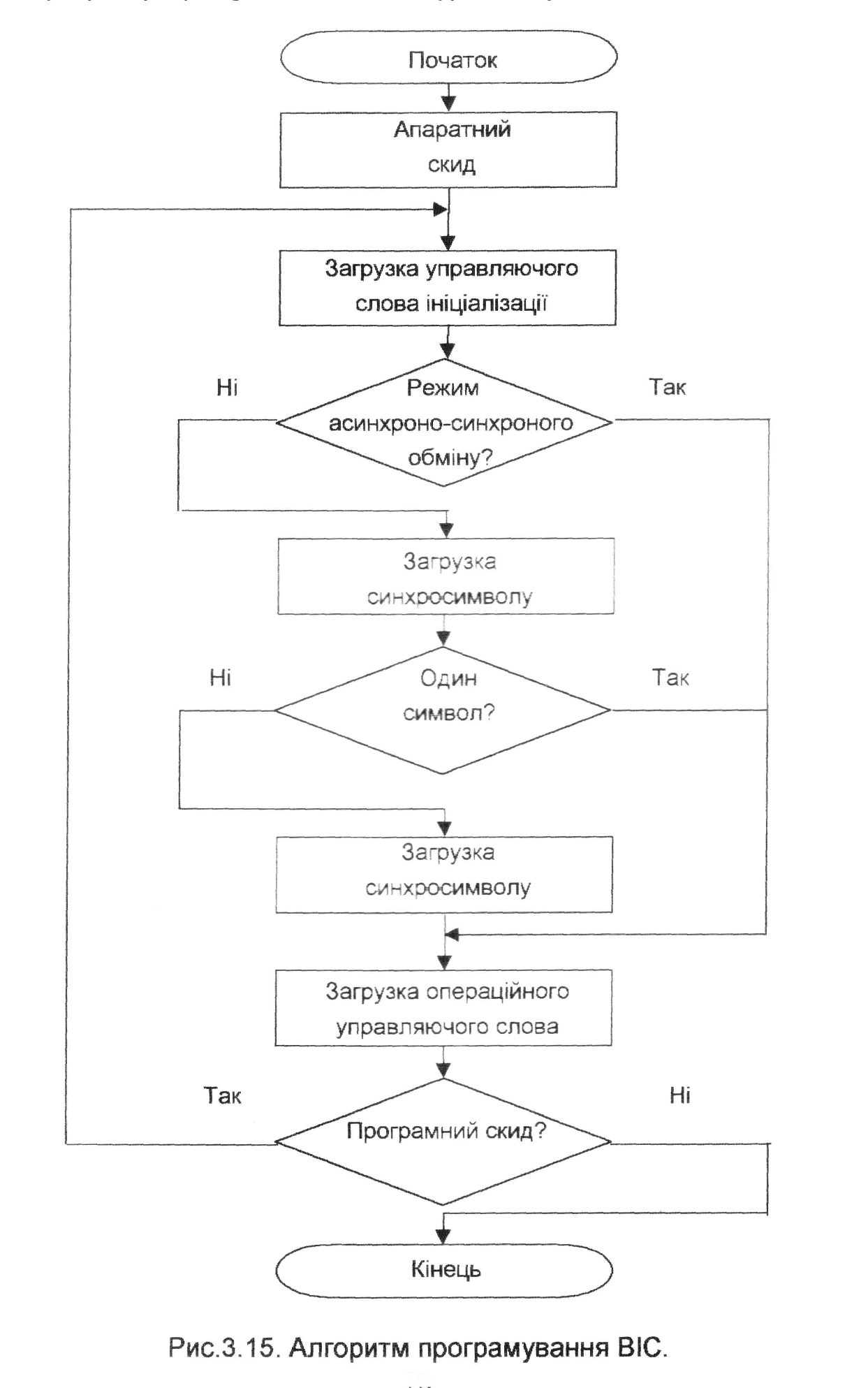

При синхронній передачі існує загальна лінія синхросигналів для джерела і приймача, імпульси служать для виділення бітів в каналі.

При асинхронній передачі джерело помічає початок і кінець слова.

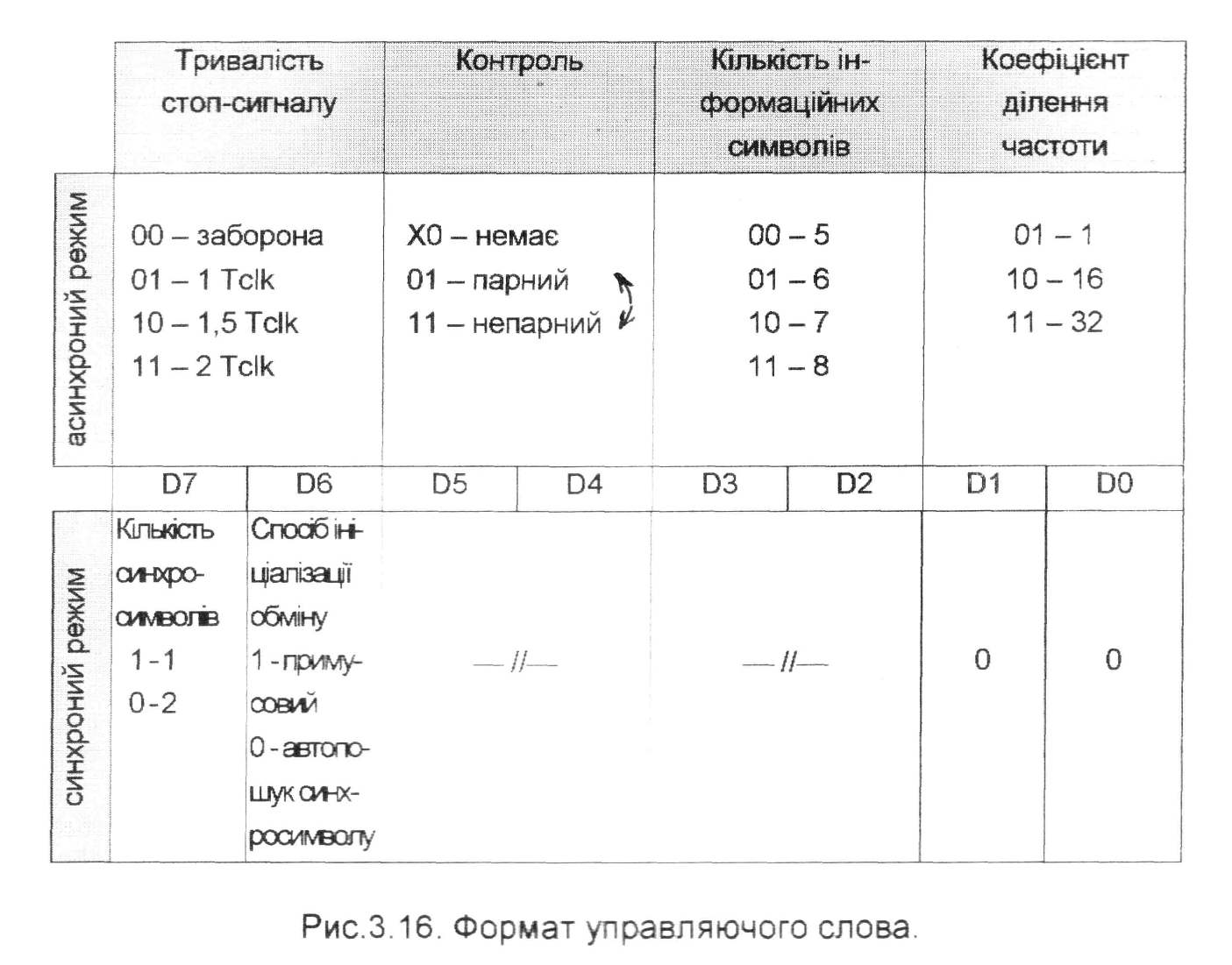

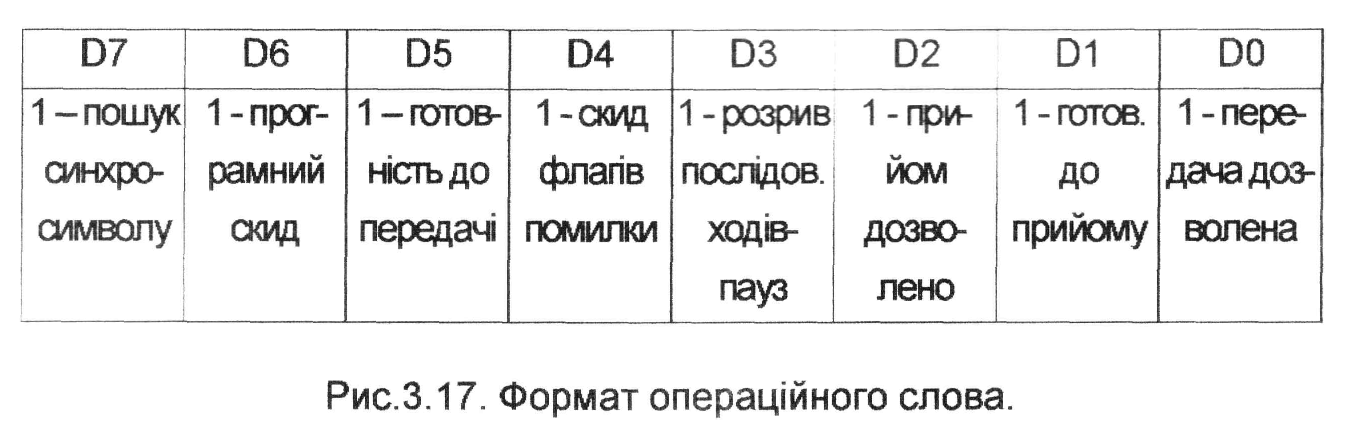

Формат управляючого слова ініціалізації при асинхронно-синхронному та синхронному режимах обміну наведено на рис.3.16.

78

Приклад налагодження УСАПП у асинхронно-синхронному режимі (режимі асинхронного обміну з дуплексним каналом зв'язку, вісім інформаційних розрядів, біт контролю по парності, два стоп-біти, коефіцієнт ділення частоти дорівнює 16):

DI

XRA

OUT ADDR1

OUT ADDR1

OUT ADDR1

MVI А, 40Н

OUT ADDR1 ; програмний скид

MVI A, OFEH ;/11111110 - управляюче слово /

OUT ADDR1

MVI A, 15H ; / 00010101 - операційне слово /

OUT ADDR1 ;

El

RET

Приклад програми налагодження УСАПП у синхронному режимі (режим синхронного прийому з автопошуком синхросимволу, вісім інформаційних розрядів, контроль по парності, синхросимвол 10000000):

DI

XRA

OUT ADDR1

OUT ADDR1

OUT ADDR1

MVI A, 40H

OUT ADDR1 ; програмний скид

MVI F, OBCH ;/10111100 - управляюче слово /

OUT ADDR1

MVI A, 80H ; загрузка синхросимволу

OUT ADDR1

79

MVI A, 94H ; /10010100 - операційне слово /

OUT ADDR1

EI

RET

80