- •Аналого-цифровые преобразователи (ацп) Лекция №1. Параллельные ацп

- •Параллельные ацп

- •Лекция №2. Ацп последовательного приближения

- •Лекция №3. Ацп последовательного счёта

- •Лекция №4. Ацп двойного интегрирования

- •Интегрирующие ацп

- •Лекция №5. Правила преобразования чисел из двоичного кода в двоично-десятичный и наоборот двоично-десятичные коды

- •Преобразование двоично-десятичного кода в двоичный

- •Системы сбора данных Лекция №6. Устройства выборки-хранения (увх)

- •Лекция №7. Аналоговые мультиплексоры. Основные характеристики. Простейшая схема замещения

- •Лекция №8. Системы сбора данных (ссд). Примеры реализации многоканальных ссд

- •Системы сбора данных.

- •Лекция №9. Правила подключения индикатора к мк и порядок передачи в него данных

Оглавление

Аналого-цифровые преобразователи (АЦП) 2

Лекция №1. Параллельные АЦП 2

Лекция №2. АЦП последовательного приближения 4

Лекция №3. АЦП последовательного счёта 6

Лекция №4. АЦП двойного интегрирования 8

Лекция №5. Правила преобразования чисел из двоичного кода в двоично-десятичный и наоборот 11

Системы сбора данных 14

Лекция №6. Устройства выборки-хранения (УВХ) 14

Лекция №7. Аналоговые мультиплексоры. Основные характеристики. Простейшая схема замещения 16

Лекция №8. Системы сбора данных (ССД). Примеры реализации многоканальных ССД 18

Лекция №9. Правила подключения индикатора к МК и порядок передачи в него данных 20

Аналого-цифровые преобразователи (ацп) Лекция №1. Параллельные ацп

Аналого-цифровой преобразователь (АЦП, англ. Analog-to-digital converter, ADC) — устройство, преобразующее входной аналоговый сигнал в дискретный код (цифровой сигнал). Обратное преобразование осуществляется при помощи ЦАП.

АЦП являются устройствами, которые принимают входные аналоговые сигналы и генерируют соответствующие им цифровые сигналы, пригодные для обработки микропроцессорами и другими цифровыми устройствами.

Параллельные ацп

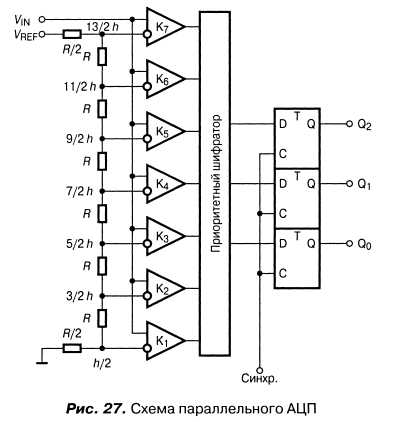

АЦП этого типа осуществляют квантование сигнала одновременно с помощью набора компараторов, включенных параллельно источнику входного сигнала. На Рис. 1.1 показана реализация параллельного метода.

Рассмотрим аналого-цифровое преобразование для 3-разрядного числа. С помощью трех двоичных разрядов можно представить восемь различных чисел, включая нуль. Следовательно, необходимо семь компараторов. Семь соответствующих эквидистантных опорных напряжений образуются с помощью резистивного делителя.

Рис. 1.1. Схема параллельного АЦП

Если приложенное входное напряжение не выходит за пределы диапазона от 5/2h до 7/2h , где h = VREF/7 - квант входного напряжения, соответствующий младшему значащему разряду АЦП, то компараторы с 1-го по 3-й устанавливаются в состояние 1, а компараторы с 4-го по 7-й - в состояние 0. Vref - refernce voltage стабилизированное напряжение используемое для установки входного или выходного напряжения. Преобразование этой группы кодов в трехзначное двоичное число выполняет логическое устройство, называемое приоритетным шифратором, диаграмма состояний которого приведена в Таблице 1.1.

-

Входное напряжение

Состояние компараторов

Выходы

0

0000000

000

1

0000001

001

2

0000011

010

3

0000111

011

4

0001111

100

5

0011111

101

6

0111111

110

7

1111111

111

Таблица 1.1. Таблица состояний параллельного АЦП.

Подключение приоритетного шифратора непосредственно к выходу АЦП может привести к ошибочному результату при считывании выходного кода. Рассмотрим, например, переход от трех к четырем, или, в двоичном коде, от 0112 к 1002. Если старший разряд вследствие меньшего времени задержки изменит свое состояние раньше других разрядов, то временно на выходе возникнет число 111, т.е. семь. Величина ошибки в этом случае составит половину измеряемого диапазона. Так как результаты аналого-цифрового преобразования записываются, как правило, в запоминающее устройство, существует вероятность получения неверной величины. Решить эту проблему можно, например, с помощью устройства выборки и хранения (УВХ). Некоторые ИС параллельных АЦП (например МАХ100) снабжаются быстродействующими УВХ, имеющими время выборки порядка 0.1 нс. Другой путь состоит в использовании кода Грея, характерной особенностью которого является изменение только одной кодовой позиции при переходе от одного кодового значения к другому. Наконец, в некоторых АЦП (например, МАХ1151) для снижения вероятности сбоев при параллельном аналого-цифровом преобразовании используется двухтактный цикл, когда сначала состояния выходов компараторов фиксируются, а затем, после установления состояния приоритетного шифратора, подачей активного фронта на вход синхронизации выходного регистра в него записывают выходное слово АЦП.

Как видно из Таблице 1.1, при увеличении входного сигнала компараторы устанавливаются в состояние 1 по очереди - снизу вверх. Такая очередность не гарантируется при быстром нарастании входного сигнала, так как из-за различия во временах задержки компараторы могут переключаться в другом порядке. Приоритетное кодирование позволяет избежать ошибки, возможной из-за этого обстоятельства, поскольку единицы в младших разрядах не принимаются во внимание шифратором.

Благодаря одновременной работе компараторов параллельный АЦП является самым быстрым. Например, восьмиразрядный преобразователь типа МАХ104 позволяет получить 1 млрд отсчетов в секунду при времени задержки прохождения сигнала не более 1.2 нс. Недостатком этой схемы является высокая сложность. Действительно, N-разрядный параллельный АЦП сдержит 2N-1 компараторов и 2N согласованных резисторов. Следствием этого является высокая стоимость (сотни долларов США) и значительная потребляемая мощность. Тот же МАХ104, например, потребляет около 4 Вт.