Сумматор и фазовращатель

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.

В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.

По способу реализации

• механические

• электромеханические

• электронные

• пневматические

По принципу действия

• на счётчиках, считающие количества импульсов в операндах

• функциональные, выдающие на выходах значения логической функции суммы по модулю и логической функции разряда переноса:

• каждый раз вычисляющие функцию разряда суммы по модулю и функцию разряда переноса

• с таблицами заранее вычисленных значений функции разряда суммы по модулю и значений функции разряда переноса записанных в:

• ПЗУ, ППЗУ (аппаратные) или

• ОЗУ (аппаратные и программные)

По архитектуре

• четвертьсумматоры — бинарные (двухоперандные) сумматоры по модулю без разряда переноса, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма по модулю;[3][неавторитетный источник?][4][неавторитетный источник?]

• полусумматоры — бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (старший разряд);

• полные сумматоры — тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (более старший разряд). Такие сумматоры изначально ориентированы только на показательные позиционные системы счисления.

По способу действия

• Последовательные (одноразрядные), в которых обработка разрядов чисел ведётся поочерёдно, разряд за разрядом, на одном и том же одноразрядном оборудовании;

• Параллельные (многоразрядные), в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование;

По способу организации переноса

• С последовательным переносом;

• С параллельным переносом;

• С условным переносом;

• С групповым переносом.

Аналоговый сумматор

Аналоговый

сумматор — устройство, выполняющее

операцию вида ![]() где —

где —

![]() некоторые

аналоговые величины. Наиболее часто

аналоговые сумматоры используются в

электронной технике.

некоторые

аналоговые величины. Наиболее часто

аналоговые сумматоры используются в

электронной технике.

Сумматоры на операционных усилителях

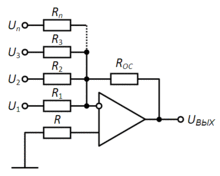

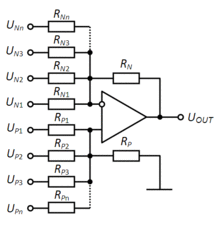

Схема простейшего аналогового сумматора на операционном усилителе приведена на рис. 1. В качестве суммируемых величин выступают входные напряжения U1 ... Un, в качестве результата — выходное напряжение схемы UВЫХ.

Рис. 1. Электронный аналоговый сумматор

Принцип действия

Полагая, что операционный усилитель является идеальным (с бесконечным коэффициентом усиления и нулевыми входными токами), из первого закона Кирхгофа получаем, что ток через сопротивление RОС равен сумме токов через сопротивления R1 ... Rn:

![]()

Выражая токи через напряжения и сопротивления, приходим к выражению

![]()

Таким образом, схема рис. 1 выполняет над входными напряжениями операцию

![]()

В

случае, если

![]() ,,

схема является чистым инвертирующим

сумматором, если же сопротивления имеют

разные значения, получается взвешивающий

сумматор, причём весовые коэффициенты

для каждой входной переменной равны

,,

схема является чистым инвертирующим

сумматором, если же сопротивления имеют

разные значения, получается взвешивающий

сумматор, причём весовые коэффициенты

для каждой входной переменной равны

![]()

Параллельный сумматор

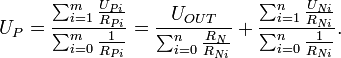

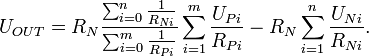

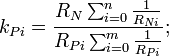

Подключая входные сигналы к инвертирующему и неинвертирующему входам операционного усилителя, можно получить схему, реализующую одновременно сложение и вычитание аналоговых сигналов. Эта схема, называемая параллельным сумматором, изображена на рис. 2. Принцип действия схемы аналогичен принципу действия простейшего сумматора. Полагая, что входные токи операционных усилителей пренебрежимо малы, а потенциалы на его входах равны (UP = UN), получим из первого закона Кирхгофа:

![]()

![]()

![]()

![]()

Перенося в левые части двух последних уравнений члены, содержащие UP, получим:

![]()

![]()

Из обоих уравнений найдём UP и приравняем правые части полученных выражений:

Из последнего выражения находим выходное напряжение схемы:

Таким образом, схема осуществляет сложение напряжений UPi и вычитание напряжений UNi с весовыми коэффициентами, равными

![]()

Рис. 2. Параллельный электронный аналоговый сумматор

Цифровой сумматор

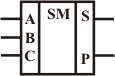

Сумматор - устройство, выполняющее операции арифметического сложения над двоичными числами. Из математических операций над двоичными числами известно, что сумма двух нулей есть нуль, сумма нуля и единицы есть единица, сумма двух единиц есть нуль. Одноразрядный цифровой сумматор имеет три входа: два входа слагаемых и вход переноса (от предыдущего сумматора). При этом правила сложения немного усложняются. Одноразрядный сумматор обозначается так:

Рис. 3 - Одноразрядный цифровой сумматор

Сумматор имеет входы А и В - слагаемые, С - вход переноса, S - выход суммы, Р - выход переноса. Таблица истинности:

Входы Выходы

Слагаемые Вход переноса Сумма Выход переноса

А B C S P

0 0 0 0 0

0 1 0 1 0

1 0 0 1 0

1 1 0 0 1

0 0 1 1 0

0 1 1 0 1

1 0 1 0 1

1 1 1 1 1

На выходе S представляется сумма сложения трех переменных - А, В, С. При переполнении сумматора, т. е. когда в результате сложения формируется единица в старшем разряде выходного числа, на выходе переноса Р формируется уровень лог. 1, который подается на вход переноса С следующего сумматора. В принципе, старшим разрядом суммы является выход переноса Р. В целом работу сумматора полностью иллюстрирует таблица. Из таких одноразрядных сумматоров составляются многоразрядные сумматоры (обычно 4-х разрядные), которые бывают последовательного и параллельного действия. Сумматоры последовательного действия обладают более низким быстродействием.

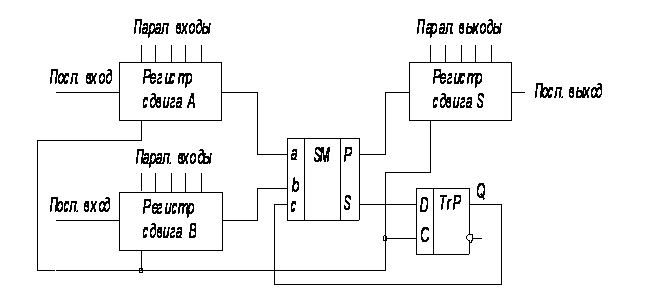

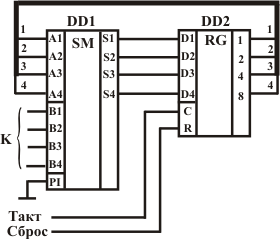

Последовательные сумматоры преобразуют последовательные коды слагаемых в последовательный код суммы этих слагаемых. Сложение начинается с младшего разряда и выполняется поразрядно последовательно за столько тактов, сколько разрядов содержится в числе. В состав многоразрядного сумматора последовательного действия, кроме комбинационного одноразрядного сумматора, применяют три сдвигающих регистра для двух слагаемых A и B и для результата S, триггер переноса TrP и схемы управления вводов и выводов чисел (рисунок 4).

Рис 4. Последовательный n-разрядный сумматор

Два

суммируемых числа загружаются в

регистры A и B по

последовательным и параллельным входам.

Триггер переноса первоначально установлен

в 0, следовательно C=0. сигнал

суммы записывается в регистр сдвига S.

Каждый сигнал переноса, вырабатываемый

сумматором, появляется на выходе P и

запоминается триггером переноса.

Тактовый импульс вводит бит суммы в

регистр S и одновременно

сдвигает на один разряд регистры A и B.

Кроме того, он вносит значение

переноса P и TrP, в

результате чего на входе С всегда

действует значение разряда переноса,

имевшее место при сложении двух предыдущих

разрядов. Так суммируются все разряды

двоичных чисел и результат записывается

в регистр S. Этот результат можно

считать по параллельным или последовательным

выходам. Основное достоинство такого

сумматора – малое количество оборудования;

к недостаткам относится малое

быстродействие, т.к. время суммирования

двух n-разрядных чисел ![]() ,

где T – период следования

тактовых импульсов.

,

где T – период следования

тактовых импульсов.

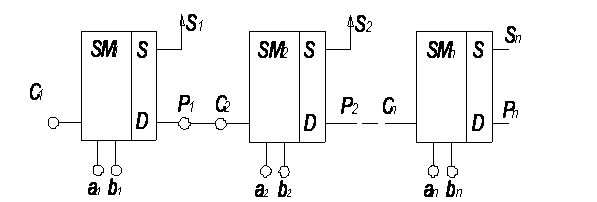

Параллельные многоразрядные сумматоры. Термин «параллельные» подразумевает наличие многих разрядных схем в соответствии с разрядностью операндов и подачу переменных параллельным кодом. Перенос между разрядами может распространяться и последовательно, и параллельно, и комбинированным способом.

Параллельные

многоразрядные сумматоры предназначены

для одновременного суммирования двух

многоразрядных чисел и характеризуется

различными способами передачи сигналов

переноса от младших разрядов к старшим

разрядам сумматора. В параллельных

сумматорах с последовательным переносом

выход переноса P i-го разряда ПОС

связан с входом С i+1-го разряда

ПОС (рисунок 5). При этом максимальная

задержка формирования суммы на выходе

старшего разряда при передаче переноса

из i-го разряда в n-й разряд

определяется суммой задержек переноса

всех предшествующих разрядов и собственной

задержки формирования суммы ![]() ,

где tp, ts –

задержка формирования переноса и суммы

в одноразрядном сумматоре.

,

где tp, ts –

задержка формирования переноса и суммы

в одноразрядном сумматоре.

Рис. 5 Параллельный комбинационный сумматор с последовательным

Десятичный сумматор

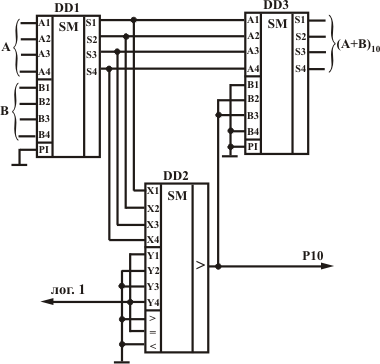

Чаще приходится суммировать десятичные числа. Ниже на рисунке приведена схема сумматора двоично-десятичных чисел на основе двоичных сумматоров.

Рис. 6 - Сумматор двоично-десятичных чисел

Операцию сложения выполняет сумматор DD1. При сумме большей или равной десяти на выходе микросхемы DD2, которая является схемой сравнения входов, формируется сигнал переноса Р10. На второй вход (Y1-Y4) микросхемы DD2 подается двоичный эквивалент числа 9 (1001). Сумматор DD3 осуществляет десятичную коррекцию результата суммирования. При отсутствии сигнала переноса на выходе микросхемы DD3 повторяется код числа, который был на выходе DD1, поскольку на входы В поданы лог. 0. При наличии сигнала переноса Р10=1 на входах В2-В3 устанавливаются лог. 1, что соответствует коду числа 6. Допустим есть числа А=8 и В=4. На выходе сумматора DD1 появляется код числа 12 (8+4=12). На выходе DD2 формируется сигнал переноса, сумматор DD3 выполняет операцию 12+6=18. Числу 18 соответствует код 10010. На выходах S сумматора DD3 устанавливается код 0010 (собственный перенос микросхемы DD3 не учитывается). Поскольку на выходе Р10 число 10, на выходах сумматора число 2 (0010), то в результате получается число 12.

Сумматор-накопитель

Интересными свойствами обладает сумматор-накопитель, показанный на рисунке 6.

Рис. 6 - Сумматор-накопитель

На рисунке показан простейший сумматор-накопитель. На один вход сумматора подается число К, а на второй - число с выхода регистра. В начале работы регистр обнуляется (сброс). Если на входы В сумматора DD1 подать некоторое число К, то при подаче импульса на вход С регистра (такт) в него запишется число К (в начальный момент на выходе регистра лог.0). Это же число К попадет на входы А сумматора и по следующему такту в регистр запишется уже число 2К, которое опять попадет на входы А сумматора. На выходе сумматора появится число 3К и по следующему такту запишется в регистр и т. д. То есть, в сумматоре-накопителе постепенно нарастает число. Когда в сумматоре-накопителе накопленное число превышает его объем, равный 2n-1, на выходе переноса появляется сигнал лог. 1, а на выходах S число nK-2n.

Применение таких сумматоров весьма разнообразно. Если вместо регистра установить ОЗУ (это делается в многоканальных системах), тогда такой узел становится важнейшей частью микропроцессора. Посмотрим на эти свойства сумматора-накопителя. Поскольку сигнал переноса сумматора появляется через W=2n/K тактовых импульсов, то такой сумматор является обратным преобразователем входного числа К в число W. Это число можно подсчитать на счетчике. Ну а если выразить частоту появления имульсов переноса через число К, получится:

![]()

Это значит, что получается преобразователь кода числа К в частоту импульсов. Такой преобразователь можно использовать в электронных музыкальных инструментах (ЭМИ), всяких звонках и т. п.

С помощью сумматоров-накопителей можно производить умножение числа на некоторый постоянный коэффициент, можно сделать квадратичный накопитель и т.д.

Фазовращатель - устройство, осуществляющее поворот фазы электрич. сигнала. Широко используется в разл. радиотехн. устройствах - антенной технике, технике связи, радиоастрономии, измерит. технике и др. (см. также Антенна, Радиоприёмные устройства, Радиопередающие устройства). Ф. подразделяются на фиксированные (с фиксированным фазовым сдвигом) и регулируемые (с регулируемым фазовым сдвигом).

Классификация:

По типу волн

Отражательные

Проходные

По физическому принципу

Механические

Электрические

Электромеханические

По изменению фазы

С плавным изменением

С дискретным изменением

По способу включения в тракт

Коаксиальные

Волноводные

Полосковые

Основные характеристики

Максимальный управляемый фазовый сдвиг

Рабочий диапазон частот

Вносимые потери

Максимальный КСВн

Максимальный уровень мощности

Время переключения

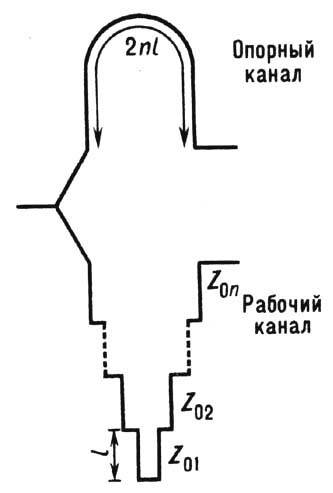

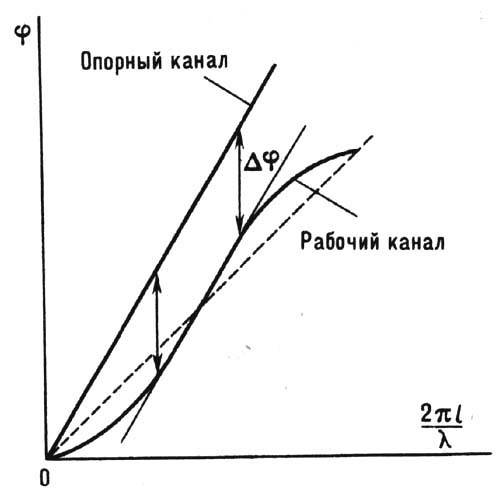

Простейшим фиксированным Ф. является отрезок линии передачи. Фазовый сдвиг, вносимый таким Ф.,

![]()

где l-длина Ф., лямбда - длина волны в линии передачи .В таком Ф. фазовый набег пропорц. рабочей частоте. Диффе-ренц. фазовый сдвиг, являющийся разностью фазовых сдвигов, вносимых трактом с Ф. (р а б о ч и й к а н а л) и трактом без Ф. (о п о р н ы й к а н а л), в этом случае также пропорц. частоте. Введением спец. корректирующих цепей можно получить постоянный в диапазоне рабочих частот фазовый сдвиг в рабочем канале относительно фазового сдвига в опорном канале. В качестве корректирующих цепей используется обычно одна или неск. секций связанных однородных линий, каскадно соединённых между собой, как показано на рис. 1. Соответствующим выбором параметров связанных линий в Ф. может быть получен заданный фазовый сдвиг относительно опорного канала, не изменяющийся в полосе рабочих частот. Типичные фа-зочастотные характеристики Ф. на связанных линиях и линии опорного канала приведены на рис. 2. Для получения фиксированного фазового сдвига, равного 90°, могут использоваться направленные ответвители с равным делением мощности, в выходных плечах к-рых сигналы сдвинуты по фазе относительно друг друга на 90° во всём диапазоне рабочих частот.

Рис. 1. Фазовращатель на связанных линиях передачи.

Рис. 2. Фазочастотные характеристики рабочего и опорного каналов фазовращателя на связанных линиях передачи.

Регулируемые Ф. подразделяются на Ф. с электрич. и "ручным" управлением. В Ф. с "ручным" управлением регулировка фазы может осуществляться за счёт изменения геом. длины линии либо за счёт изменения длины волны в линии. Геом. длина может регулироваться, напр., в телескопич. конструкции линии. Регулировка длины волны в линии может осуществляться регулировкой параметров заполняющей среды, напр., при помощи перемещения в линии диэлектрич. пластины с достаточно высокой ди-электрич. проницаемостью. Электрич. регулировка фазы осуществляется с помощью активных элементов с управляемым сопротивлением, в качестве к-рых могут применяться полупроводниковые диоды.

Рис. 3. Фазовращатель типа периодически нагруженной линии.

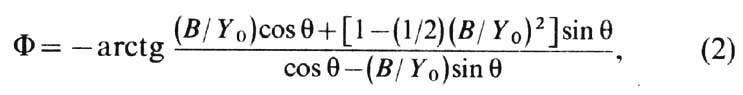

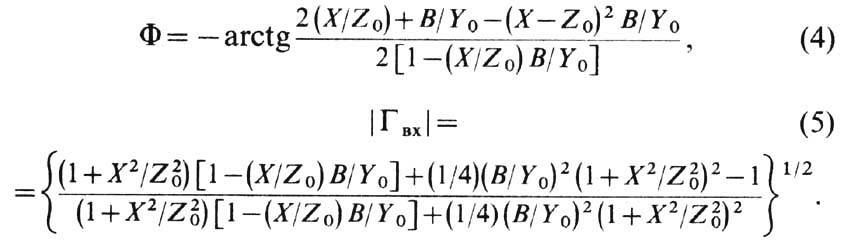

По характеру перестройки фазы Ф. подразделяются на аналоговые и дискретные соответственно с плавной и ступенчатой регулировкой вносимого фазового сдвига. По методу построения-на проходные и отражательные. Ф. проходного типа используют свойство изменения фазы коэф. передачи при изменении нагрузки линии, а Ф. отражательного типа - фазы коэф. отражения. Пример ячейки проходного Ф., выполненного по схеме типа периодически нагруженной линии, приведён на рис. 3. Фазовый сдвиг Ф., вносимый такой ячейкой, и коэф. отражения от входа Гвх определяются ф-лами

где Yо -

волновая проводимость линии, В-реактивная

проводимость нагрузок линии, q=2pl/l

-электрич. длина линии, l-геом.

длина линии. Если ![]() то

ячейка Ф. оказывается согласованной.

При изменении проводимости В в

процессе регулировки вносимого фазового

сдвига возникаем рассогласование. Макс.

величина фазового сдвига в Ф. типа

периодически нагруженной линии

ограничивается допустимым уровнем

рассогласования.

то

ячейка Ф. оказывается согласованной.

При изменении проводимости В в

процессе регулировки вносимого фазового

сдвига возникаем рассогласование. Макс.

величина фазового сдвига в Ф. типа

периодически нагруженной линии

ограничивается допустимым уровнем

рассогласования.

Рис. 4. Фазовращатели с фильтрами верхних и нижних частот Т- и П-типов.

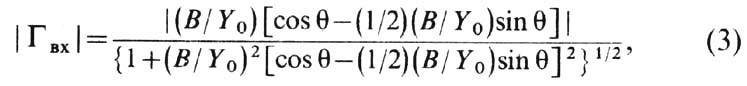

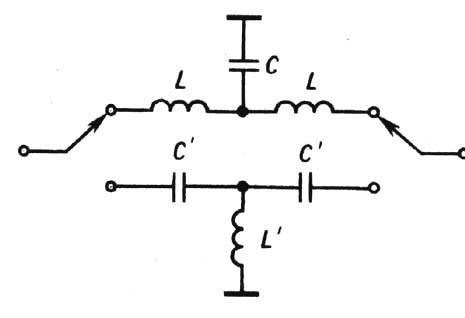

Другой разновидностью проходного Ф. является Ф. с фильтрами верхних (ФВЧ) или нижних (ФНЧ) частот. Схемы таких Ф. с ячейками Т- и П-типов приведены на рис. 4. Фазовый сдвиг и коэф. отражения от входа ячейки Ф. Т-типа определяются ф-лами

Здесь X,

В-соответственно последовательное

реактивное сопротивление и параллельная

реактивная проводимость ячейки, ![]() -волновое

сопротивление линии. Как видно из (5),

Гвх = 0, если

-волновое

сопротивление линии. Как видно из (5),

Гвх = 0, если

![]()

Для Ф. П-типа в ф-лах (4)-(6) X и В меняются местами. Если условие (6) в процессе регулировки выполняется, то Ф. остаётся согласованным во всём диапазоне регулировки фазы. Одновременная регулировка ёмкостных и индуктивных элементов фильтров, при к-рой условие (6) выполняется, затруднительна. Поэтому Ф. с ФВЧ и ФНЧ, как правило, используются для дискретной регулировки фазы. Переключение фазы в таких Ф. осуществляется переключением фильтров ФВЧ и ФНЧ. Схема ячейки дискретного Ф. с ФВЧ и ФНЧ приведена на рис. 5. В каждом из фильтров Ф. условие (6) должно выполняться. Эта схема дискретного Ф. по принципу работы близка к Ф. типа переключаемых каналов. В этих Ф. переключаются не фильтры, а отрезки линий передачи (каналы), имеющие разл. длины.

Рис. 5. Дискретный фазовращатель с фильтрами верхних и нижних частот.

Рабочий канал может содержать описанную выше корректирующую цепочку для выравнивания фазочастотной характеристики.

В Ф. отражательного типа фаза коэф. отражения регулируется сопротивлением оконечной нагрузки линии. Зависимость фазы коэф. отражения от сопротивления нагрузки

![]() определяется

ф-лой

определяется

ф-лой

![]()

Если сопротивление нагрузки линии носит чисто реактивный характер, что, как правило, имеет место в аналоговых Ф., где используются управляющие элементы с малыми активными потерями, такие, как диоды с нелинейной ёмкостью, работающие при обратном смещении р-n-пере-хода, то

![]()

где Хн - реактивное сопротивление нагрузки линии.

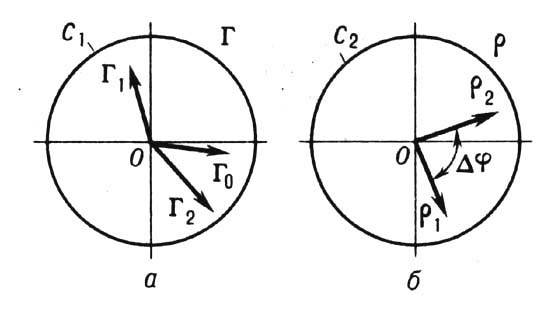

Рис. 6. Комплексные плоскости коэффициентов отражений Г в сечении переключательного элемента (а) и на входе четырёхполюсника (б).

В

дискретных Ф. в качестве управляющих

элементов применяются pin-диоды,

переключательные диоды с Шоттки

барьером и др. В этих

диодах необходимо учитывать активные

потери, к-рые к тому же могут не оставаться

постоянными при переключении. Если

переключат. элемент непосредственно

включить в линию, то фазы и амплитуды

отражённых волн будут определяться

комплексными коэф. отражений Г1 и

Г2, соответствующими сопротивлениям

переключат. элемента в каждом из

состояний![]() На

комплексной плоскости коэф. отражений

Г, показанной на рис. 6 (а), эти коэф.

отражений изображаются

радиус-векторами ОГ1 и ОГ2,

лежащими внутри единичной окружности C1.

Для получения необходимой разности фаз

с пост. значениями амплитуд отражённых

волн в каждом из состояний (или с заданным

отношением амплитуд) перед переключат.

элементом включается спец. четырёхполюсник,

осуществляющий преобразование коэф.

отражения Г1 и Г2 в

сечении переключат. элемента в коэф.

отражения

На

комплексной плоскости коэф. отражений

Г, показанной на рис. 6 (а), эти коэф.

отражений изображаются

радиус-векторами ОГ1 и ОГ2,

лежащими внутри единичной окружности C1.

Для получения необходимой разности фаз

с пост. значениями амплитуд отражённых

волн в каждом из состояний (или с заданным

отношением амплитуд) перед переключат.

элементом включается спец. четырёхполюсник,

осуществляющий преобразование коэф.

отражения Г1 и Г2 в

сечении переключат. элемента в коэф.

отражения![]() и

и ![]() на

входе четырёхполюсника. На комплексной

плоскости коэф. отражений r, показанной

на рис. 6 (б), эти коэф. отражений

изображаются радиус-векторами

на

входе четырёхполюсника. На комплексной

плоскости коэф. отражений r, показанной

на рис. 6 (б), эти коэф. отражений

изображаются радиус-векторами ![]() и

и ![]() внутри

единичной окружности С2.

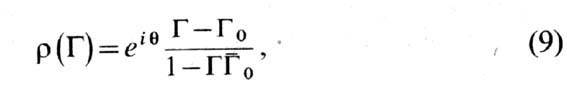

Преобразование единичной окружности

в единичную окружностъ осуществляется

дробно-линейным конформным отображением

вида

внутри

единичной окружности С2.

Преобразование единичной окружности

в единичную окружностъ осуществляется

дробно-линейным конформным отображением

вида

где![]() -точка

внутри единичного круга в комплексной

плоскости Г, переходящая в центр

единичного круга в комплексной плоскости

р;

-точка

внутри единичного круга в комплексной

плоскости Г, переходящая в центр

единичного круга в комплексной плоскости

р;![]() -число,

комплексно сопряжённое с числом

Г0;q-произвольное действит. число,

определяющее поворот конформного

отображения относит. центра r0=0.

Выбором положения точки Г0 в

единичном круге С1 на

комплексной плоскости Г можно добиться

необходимого положения радиус-векторов

r1 и r2 на комплексной

плоскости коэф. отражения. Для этого

должны выполняться условия

-число,

комплексно сопряжённое с числом

Г0;q-произвольное действит. число,

определяющее поворот конформного

отображения относит. центра r0=0.

Выбором положения точки Г0 в

единичном круге С1 на

комплексной плоскости Г можно добиться

необходимого положения радиус-векторов

r1 и r2 на комплексной

плоскости коэф. отражения. Для этого

должны выполняться условия

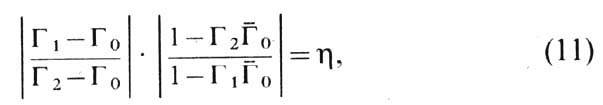

![]()

где

DФ, h -заданные значения сдвига фаз и

отношения амплитуд векторов коэф.

отражения Ф. Поскольку точка Г0 переходит

в центр единичной окружности на

преобразованной плоскости коэф. отражения

r, то она оказывается согласованной в

этой плоскости. Следовательно, ф-ция

четырёхполюсника, включённого перед

переключат. элементом, сводится к

согласованию нек-рого фиктивного комплексного

сопротивления ![]() соответствующего

коэф. отражения Г0. Это фиктивное

сопротивление, называемое

"согласуемый импеданс",

определяется сопротивлениями переключат.

элемента в каждом из состояний и заданными

параметрами Ф. и может быть найдено по

коэф. отражения Г0, определяемому

ф-лами (10), (11). Напр., для Ф. на 180° с равными

амплитудами в каждом из состояний

соответствующего

коэф. отражения Г0. Это фиктивное

сопротивление, называемое

"согласуемый импеданс",

определяется сопротивлениями переключат.

элемента в каждом из состояний и заданными

параметрами Ф. и может быть найдено по

коэф. отражения Г0, определяемому

ф-лами (10), (11). Напр., для Ф. на 180° с равными

амплитудами в каждом из состояний

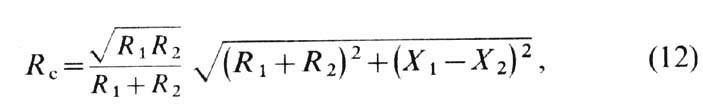

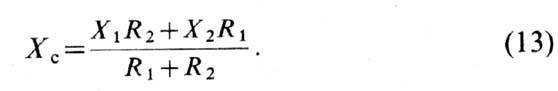

Для обеспечения заданных параметров Ф. в широкой полосе частот необходимо согласование согласуемого импеданса Zc во всей рабочей полосе частот.

Разделение падающей и отражённой волн в Ф. отражат. типа осуществляется при помощи спец. развязывающих устройств, таких, как Y-циркуляторы или направленные ответвители с равным делением мощности в выходных плечах. Работа Ф. отражат. типа с Y-циркулятором основана на однонаправленном прохождении сигнала по Y-циркулятору. Сигнал, поданный на один из входов Y-циркулятора, полностью поступает на др. его вход, к к-рому подключена отражат. ячейка Ф. Отражённый от ячейки сигнал поступает на третий вход Y-циркулятора, являющийся выходом Ф.

В Ф. с направленным ответвителем отражательные ячейки подключают к прямому и ответвлённому плечам. Сигналы, поступающие со входа направленного ответвителя на отражат. ячейки, равны по амплитуде и находятся в квадратуре. Отражённые от отражат. ячеек сигналы поступают на вход и выход Ф. Если отражат. ячейки идентичны, то на входе направленного ответвителя сигналы находятся в противофазе, а на выходе - в фазе и, следовательно, полностью поступают на выход Ф. В качестве развязывающих устройств могут использоваться также кольцевые гибридные соединения длиной 3l/2 Отражат. ячейки подключаются к развязанным входам гибридного соединения. Поскольку поступающий на вход сигнал достигает развязанных входов в фазе, то для обеспечения необходимого 90°-ного фазового сдвига перед одной из отражат. ячеек должен быть установлен дополнительный четвертьволновый отрезок линии либо др. фиксированный Ф. Это при идентичности отражат. ячеек обеспечивает суммирование отражённых сигналов в четвёртом плече гибридного соединения, являющемся выходом Ф., и их отсутствие во входном плече.

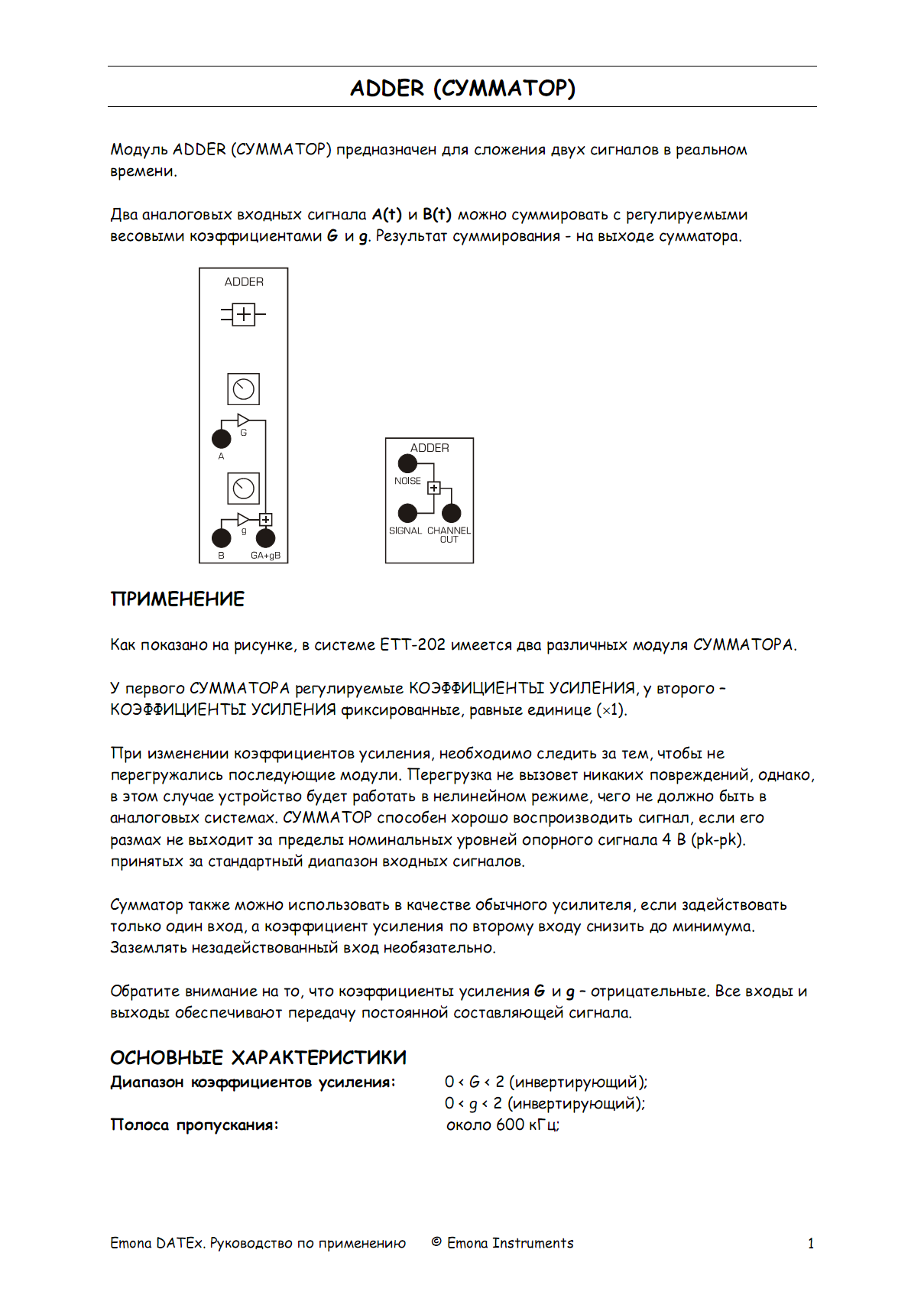

АМПЛИТУДНАЯ МОДУЛЯЦИЯ (2 МЕТОД) И ДЕТЕКТОР ПРОИЗВЕДЕНИЯ АМ СИГНАЛА

Усилители класса С это популярные схемы для коммерческой реализации амплитудной модуляции высокого уровня (например, на конечной стадии в передатчиках). Принципиальное преимущество усилителей такого типа это эффективность, которая теоретически может достигать 90%, хотя на практике несколько меньше.

Когда

усилитель класса С работает с глубинами

модуляции ниже 100%, осуществляются схемы

для уравнения

![]() , которые в Emona

DATEx

реализуются согласно блок схеме:

, которые в Emona

DATEx

реализуются согласно блок схеме:

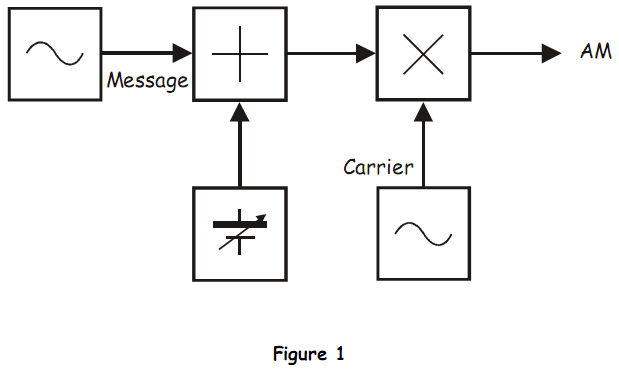

Используя тригонометрические построения (не показанные здесь), уравнение можно переписать в следующем виде:

![]()

Вы можете узнать в первой части уравнения математическую модель DSBSC сигнала. Согласно этому, можно переписать уравнение:

![]()

Это полезно, т.к. дает нам альтернативный метод осуществления АМ – сгенерировать DSBSC сигнал, а после добавить к нему несущую. Блок схема такой реализации представлена на рис.2.

Существенное значение имеют отношения между фазами несущей, используемой при генерации DSBSC сигнала, и добавляемой несущей. Для того чтобы получить АМ сигнал, эти несущие должны быть строго в фазе. Хотя это и не оговорено в уравнение, но подразумевается.

Какими могут быть последствия несовпадения по фазе двух несущих? Во-первых, форма сигнала лишь примерно воспроизводит АМ. Важно, что огибающие больше не являются копией сигнала сообщения, и детектор огибающей в этом случае не подходит для их восстановления. Во-вторых, индекс модуляции «m» сигнала, вычисляемый с помощью измерений с осциллографа, более не имеют силу для последующих вычислений распределения мощности между несущей и боковыми полосами частот.

Детектор огибающей для АМ сигнала

Детектор огибающей – это классический, широко используемый, метод демодуляции АМ. Хотя и не единственный. Детектор произведения (или, более правильно, демодулятор произведения) также может быть использован в целях демодуляции.