- •Задание

- •Учебные вопросы и распределение времени.

- •1. Назначение, состав и основные технические характеристики специализированного вычислителя.

- •1.1. Назначение специализированного вычислителя.

- •1.2. Состав спецвычислителя (св).

- •1.3 Основные технические характеристики св.

- •2. Структурная схема св. Взаимодействие элементов св в режимах "модифицированная запись" и "чтение".

- •2.1 Принцип взаимодействия устройств св

- •2.2 Чтение информации из зу (режим “ Чтение “).

- •Алгоритм взаимодействия устройств св в режиме чтения информации представлен на рис 5.

- •2.3 Запись информации в зу ( режим “ Модифицированная запись”).

- •Структурная схема св. Взаимодействие ВчУ с уо

- •Структурная схема св. Взаимодействие элементов поу св с ВчУ.

2.2 Чтение информации из зу (режим “ Чтение “).

При обращении к ЗУ в режиме чтения информации процессор устанавливает в МА адрес ячейки ЗУ, к которой осуществляется обращение, а по КШУ 1 процессор выдаёт вУК сигнал Тр ОБР 1, который является заявкой процессора на обращении к ЗУ. Полный адрес ячейки ЗУ состоит из адреса модуля и адреса ячейки. Четыре старших разряда магистрали адреса(АМ0…АМ3) подключены к УК. По этим разрядам МА передаётся адрес модуля, где находится ячейка памяти, к которой осуществляется обращение.

Код, содержащийся в старших разрядах магистрали адреса АМ0…АМ3 – номер модуля определённого ЗУ, к которому процессор требует обращения, он передаётся в УК процессором, желающим обратиться к данному модулю памяти одновременно с сигналом ТрОбр1.

УК производит анализ этих сигналов с целью определения, свободен ли в данном такте работы УК требуемый модуль ЗУ, и нет ли в данном такте работы обращения более приоритетного процессора к незанятому модулю ЗУ.

Если требуемый модуль ЗУ свободен, и нет обращения к незанятому модулю со стороны более приоритетного процессора, то УК разрешает процессору, выставившему заявку на обращение к ЗУ, выдачу адреса ячейки ЗУ. Для этого УК выдает в процессор по КШУ 1 сигнал Вд А и запускает в работу требуемый модуль ЗУ путём выдачи по КШУ 2 сигнала ОБР 1.

В результате выдачи этих сигналов производятся следующие действия:

процессор выдаёт в МА адрес требуемой ячейки ЗУ;

в ЗУ возбуждается (начинает работать) схема управления, куда заносится адрес ячейки памяти и формируется сигнал ЗАН, используемый для анализа занятости ЗУ при обращении к нему процессоров (исключается обращение к занятому модулю другого процессора).

примерно через 1 мкс после поступления сигнала ОБР 1 сигнал ЗАН снимается, а через 1,2 мкс ЗУ по КШУ 2 выдаёт в УК сигнал готовности (ГОТ) и в МЧт считанную 36-ти разрядную информацию из ячейки с заданным адресом.

по сигналу ГОТ УК по КШУ 1 выдаёт в процессор, требовавший обращения к ЗУ, сигнал приём слова (ПрС), по которому производится приём считанной информации из МЧт в процессор.

На этом взаимодействие процессора и модуля ЗУ в режиме “Чтение” завершается. Последовательность обмена сигналами управления при взаимодействии процессора с ЗУ в режиме “Чтение” представлена на

рис 2.

Рис.2. Схема обмена сигналами ВчУ-УК-ЗУ в режиме “Чтение”

Алгоритм взаимодействия устройств св в режиме чтения информации представлен на рис 5.

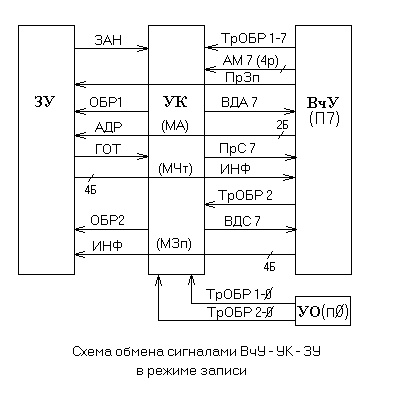

2.3 Запись информации в зу ( режим “ Модифицированная запись”).

Режим записи можно разделить на две фазы. В первой фазе информация считывается из ЗУ, как и в режиме “Чтение”. Отличие от режима “Чтение” состоит в том, что одновременно с выдачей в МА адреса ячейки памяти, процессор выдаёт по специальной шине признак записи (ПрЗп), а в ЗУ момент снятия сигнала ЗАН отсчитывается не от сигнала Обр1, а от сигнала Обр2.

После получения информации из МЧт по сигналу ПрС и обработки её процессор по КШУ 1 выдаёт в УК сигнал Тр Обр 2.

Если в данном такте работы УК не поступил сигнал Тр ОБР 2 от более приоритетного процессора , то УК посылает в процессор по КШУ 1 сигнал “ выдача слова “ (ВдС), а в ЗУ по КШУ 2 – сигнал Обр 2.

В противном случае ( если есть сигнал Тр Обр 2 от более приоритетного процессора ) обслуживание процессора откладывается до следующего такта работы УК. По сигналу ВдС процессор выдаёт в МЗп сформированную для записи в ячейку памяти информацию. На этом процесс обмена информацией в режиме “Модифицированная запись” заканчивается. Последовательность обмена сигналами управления при взаимодействии процессора с ЗУ в режиме “Модифицированная запись” представлена

на рис 3.

Рис.3. Схема обмена сигналами ВчУ-УК-ЗУ в режиме “Модифицированная запись”

Алгоритм взаимодействия устройств СВ в режиме записи информации представлен на рис 6.