- •Раздел 5. Микроконтроллеры arm7 семейства at91sam7 фирмы Atmel

- •Тема 5.1 Общие сведения

- •Тема 5.2 Сравнительный обзор микроконтроллеров с ядром arm7

- •Тема 5.2.1 мк семейства aDuC70xx фирмы Analog Devices

- •Тема 5.2.2 мк семейства lpc2ххх фирмы nxp

- •Тема 5.2.3 мк семейства tms470r1x фирмы Texas Instruments

- •Тема 5.2.4 мк семейства at91sam7s фирмы Atmel

- •Тема 5.3 Процессорное ядро arm7

- •Тема 5.3.1 Конвейер

- •Тема 5.3.2 Режимы работы процессора

- •Тема 5.3.3 Регистры

- •Тема 5.3.4 Регистр текущего состояния программы

- •Тема 2.3.5 Определение режима работы процессора

- •Тема 2.3.6 Обработка исключительных ситуаций

- •Тема 5.3.7 Система команд

Тема 5.3.4 Регистр текущего состояния программы

Помимо регистрового банка процессор имеет дополнительный 32-битный регистр, называемый регистром текущего состояния программы (Current Program Status Register – CPSR). В данном регистре содержится набор флагов, управляющих функционированием ЦПУ ARM7 и отображающих его состояние.

Суммарное количество доступных процессору физических регистров состояния равно 6, так как при переключении между режимами текущее содержимое регистра состояния CPSR автоматически переписывается в один из специальных регистров сохранения состояния программы SPSR_xxx (Saved Program Status Registr), соответствующий новому режиму, и, помимо этого, сохраняется в теневом регистре. При возврате в прежний режим содержимое CPSR автоматически восстанавливается из сохраненной копии в соответствии с таблицей 5.1.

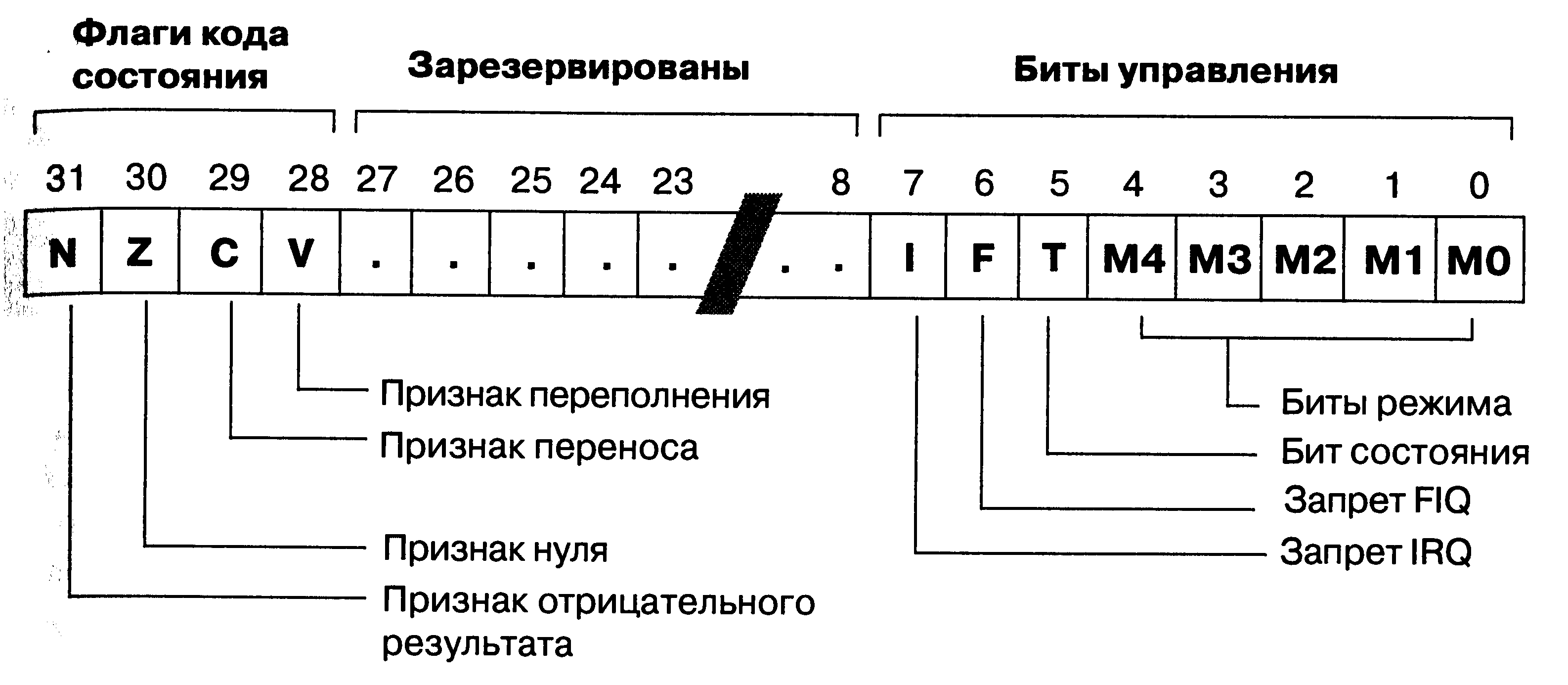

Формат регистра CPSR приведен на рисунке 5.2.

Рисунок 5.2 – Битовая структура регистра состояния CPSR.

Регистр CPSR недоступен для записи в режиме User. Он содержит флаги условий, отображающие результат выполнения команд обработки данных, а также набор пользовательских флагов, определяющих режим работы процессора и управляющих прерываниями.

CPSR содержит следующие биты:

М4 – М0 – определяют режим работы процессора в соответствии с таблицей 2.2;

Т – определяет состояние процессора: ARM (T=0) или Thumb (Т=1);

I, F – маскируют обработку прерываний IRQ и FIQ соответственно. Все периферийные устройства микроконтроллера, способные формировать сигнал прерывания, подключены к этим флагам. Запрет прерывания осуществляется записью в соответствующий разряд 1, а разрешение - 0;

N, Z, C, V – содержат флаги состояния процессора: N – признак отрицательного результата, Z – признак нуля, C – признак переноса, V – признак переполнения.

Тема 2.3.5 Определение режима работы процессора

Режим работы процессора определяется состоянием битов М4 – М0 регистра состояния программы CPSR в соответствии с таблицей 5.3

Таблица 5.3 – Биты режима работы процессора

При запуске процессор начинает работать в режиме Supervisor. Переход в базовый режим User осуществляется путем записи в регистр CPSR содержимого, в котором биты М4 – М0 = 10000. Обратное переключение из режима User в режим Supervisor может быть произведено только при поступлении команды программного прерывания (SWI).

Программа режима Supervisor получает доступ ко всем регистрам режима User при переходе в режим System, записав в регистр CPSR значене битов М4 – М0 = 11111.

Переход в режимёы IRQ, FIQ, Abort, Undefined происходит автоматически при поступлении соответствующих запросов прерывания или при возникновении соответствующего события.

Тема 2.3.6 Обработка исключительных ситуаций

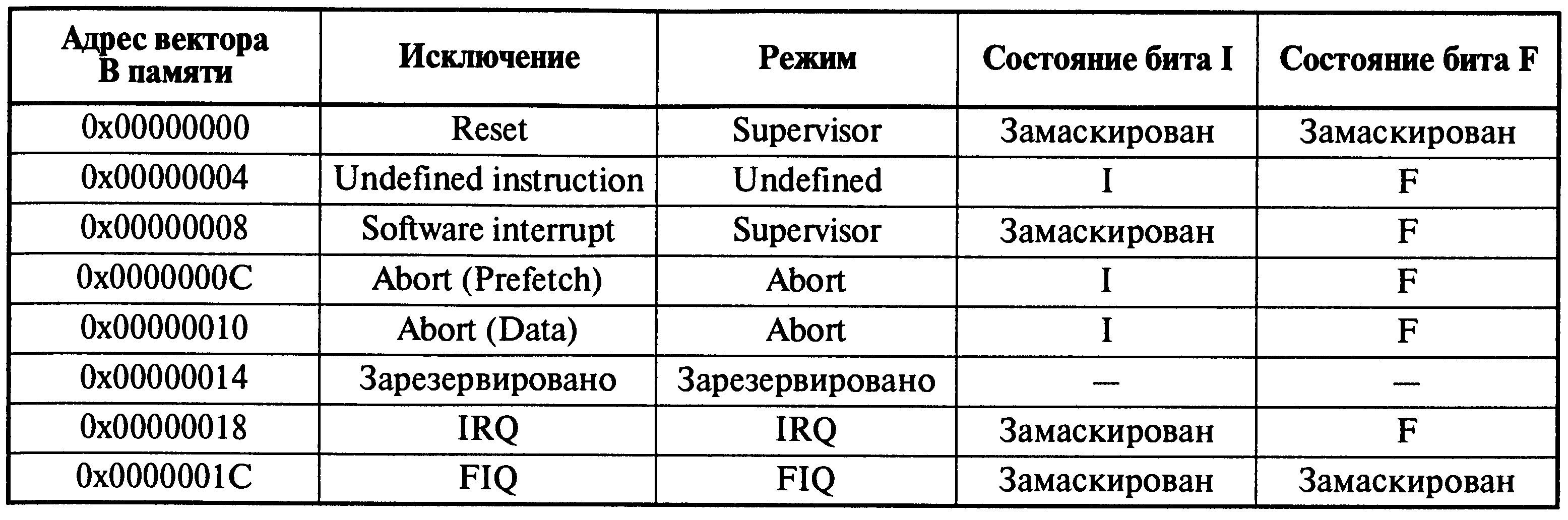

При поступлении внешнего запроса прерывания или обнаружения ошибки, т.е. возникновении исключительной ситуации (исключения), процессор начинает работать в соответствующем данному исключению режиме: IRQ, FIQ, Abort или Undefined. При этом в счетчик команд РС загружается адрес соответствующего вектора прерывания. Таблица векторов начинается с нулевого адреса, первым в таблице расположен вектор сброса, а за ним остальные векторы. Каждый вектор соёдержит 4 байта, которые являются адресами первой команды соответствующего обработчика прерывания. Адреса векторов прерываний приведены в таблице 5.4.

Таблица 5.4 Векторы исключений ARM7TDMI

Вектор по адресу 0х00000014 в таблице векторов отсутствует. Этот вектор использовался в ранних версиях процессоров ARM. В процессорах ARM7 этот адрес сохранен, чтобы обеспечить программную совместимость между различными архитектурами ARM.

Таблица исключений не содержит специальных векторов прерываний по запросам внешних устройств, т.к. в микроконтроллерах на основе процессорного ядра ARM7TDMI имеется значительное количество периферийных устройств. Поэтому в состав микроконтроллера входит специальный прерываний, задачей которых является трансляция запросов от любого периферийного устройства в запрос IRQ или FIQ. После такой трансляции программа-обработчик должна самостоятельно определить источник запроса, используя регистры контроллера прерываний.

При переходе в режим обработки исключения процессором соблюдается следующая последовательность действий:

1. Адрес следующей команды (PC + 4 или РС + 8 в зависимости от исключения) автоматически сохраняется в соответствующем регистре связи LR (R14_xxx);

2. Содержимое регистра текущего состояния программы CPSR автоматически копируется в соответствующий выбранному режиму регистр сохранения состояния программы SPSR_xxx;

3. Значение битов М4 – М0 в CPSR автоматически устанавливается в соответствии с новым режимом работы процессора (происходит смена рабочего режима), в результате чего регистры R13, R14 заменяются соответствующими регистрами этого режима;

4. В счетчик команд РС заносится адрес вектора прерывания режима исключительной ситуации. При этом могут быть также запрещены (маскированы) некоторые исключения, возникновение которых может нарушить процесс обработки, создав неуправляемое вложение исключений.

С вектора прерывания программа может перейти к выполнению подпрограммы обработки исключительной ситуации.

Исключение всегда обрабатывается в состоянии ARM, не зависимо от того в каком состоянии процессор находился в предыдущем режиме. Если же процессор находился в состоянии Thumb, то переключение в состояние ARM произойдет автоматически в тот момент, когда адрес вектора исключения будет загружен в РС.

Система команд ARM не содержит в своем составе специализированных команд для выхода из обработчика прерывания и возврата в основную программу. Поэтому для выполнения возврата блок обработчика исключения должен произвести следующие действия:

1. Восстановить содержимое регистра статуса CPSR из регистра SPSR_xxx;

2. Разрешить прерывания, запрещенные при входе в текущий обработчик;

3. Загрузить в PC адрес возврата из регистра связи LR с вычитанием смещения с помощью команды выхода из соответствующего прерывания.

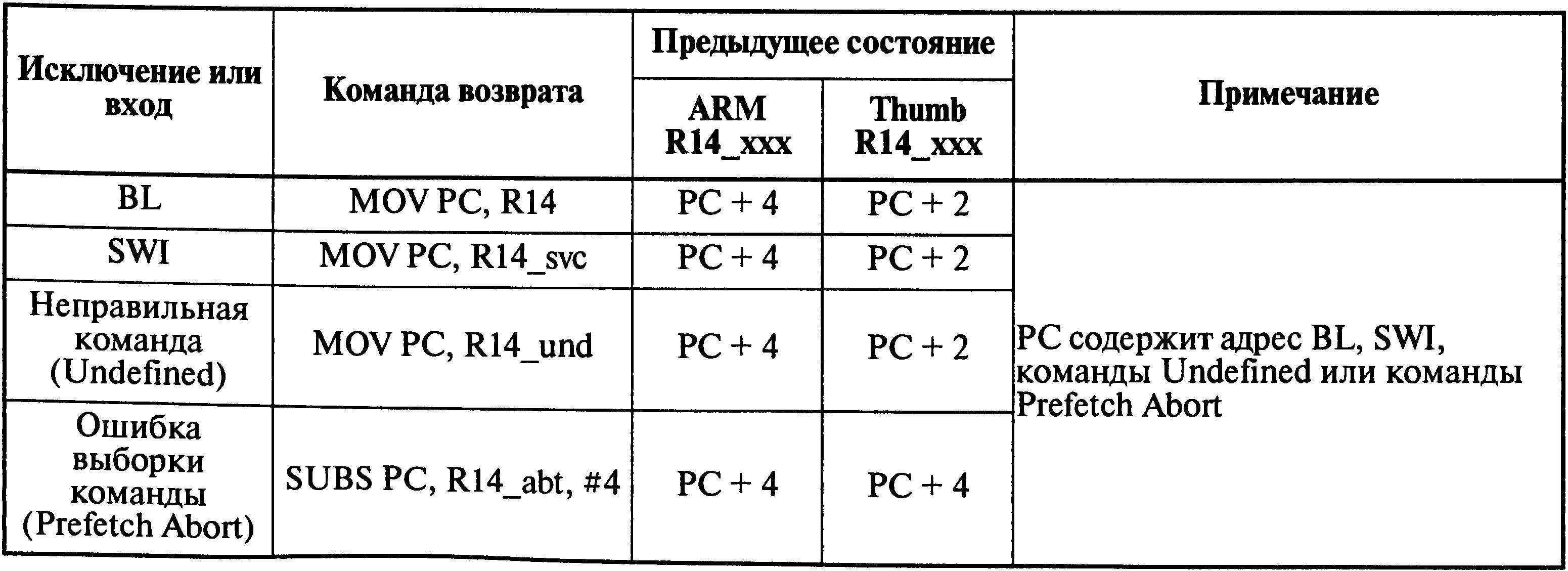

Загрузка в РС адреса возврата для каждого исключении производится командами, приведенными в таблице 5.5.

Таблица 5.5 Обработка исключений ARM7TDMI

При возврате из режимов FIQ, RIQ, Abort необходимо производить корректировку адреса возврата, т.к. после обработки этих исключений процессор должен вернуться к выполнению команды, вызвавшей это прерывание, а в регистре LR храниться адрес следующей команды. Корректировка адреса хранящегося в регистре связи при выходе их обработчика прерывания может быть произведена с помощью команды вычитания SUBS.

При одновременном возникновении нескольких исключительных ситуаций используется метод приоритетов. Приоритеты прерываний приведены в таблице 1.2.

Таблица 5.6 Приоритеты прерываний

Каждый источник исключительной ситуации имеет фиксированный приоритет. Встроенные периферийные устройства обслуживаются прерываниями IRQ и FIQ. Приоритеты прерываний от периферийных устройств можно назначить внутри этих групп.

Reset – генерируется при подаче сигнала запуска (подача и снятие сигнала сброса с активным низким уровнем) на вывод процессора nRESET. Процессор переходит в режим Supervisor и начинает выполнение программы с адреса памяти 0х00000000.

Data Abort – ошибка при обращении к данным (фиксируется контроллером прерываний). Процессор переходит в режим Abort. Когда генерируется исключение Data Abort, последующие действия ядра зависят от текущей на данный момент команды:

FIQ – генерируется при подаче сигнала прерывания высокого уровня. Процессор переходит в режим FIQ. При поступлении данного сигнала в регистровом банке происходит переключение регистров R8 – R14 на R8_fiq – R14_fiq, что позволяет сократить или исключить операции сохранения содержимого регистров в стеке и за счет этого обеспечить наименьшее время реакции на прерывание.

IRQ – возникает при подаче низкоуровневого сигнала прерывания. Процессор переходит в режим IRQ. Прерывания IRQ имеют более низший приоритет по отношению к прерываниям FIQ.

Prefetch Abort – ошибка при выборке команды (фиксируется контроллером прерываний). Ядро отмечает предварительно выбранную команду как недопустимую, но не генерирует исключения, пока команда не достигнет в конвейере стадии выполнения. Если эта команда не выполняется по причине выполнения перед ней команды перехода, но тем не менее находится в конвейере, исключение не генерируется. При генерации исключения Prefetch Abort процессор переходит в режим Abort.

Undefined Instruction – выборка неправильного кода команды. Когда процессор сталкивается с командой, которую ни он, ни какой-либо из сопроцессоров в системе не могут обработать, ядро переходит в режим Undefined.

Software Interrupt – программное прерывание по команде SWI. Процессор переходит в режим Supervisor. Программное прерывание используется, как правило, для вызова функций ОС.

В некоторых случаях, например при возникновении сигнала быстрого прерывания FIQ, может оказаться критичным время реакции на прерывание. Значение времени реакции может находиться в некотором возможном диапазоне. Когда прерывания FIQ разрешены, максимальное время реакции на FIQ (для самого “плохого” случая) складывается из следующих временных значений:

- самое длинное время запроса, которое может потребоваться на реакцию синхронизатора. Это время составляет два процессорных цикла;

- время на завершение самой длинной команды. Самая длинная команда – LDM, которая загружает все регистры, включая РС. Равно 20 процессорным циклам в системе с нулевым ожиданием;

- время для входа в обработчик Data Abort. Это время составляет три процессорных цикла;

- время для входа в обработчик FIQ. Это время составляет два процессорных цикла.

Таким образом, полное время ожидания для самого “плохого” случая составляет 27 циклов процессора.

При вычислении максимального времени ожидания IRQ необходимо учитывать, что обработка прерывания FIQ, имеющая более высокий приоритет, может задержать вход в обработчик IRQ.

Минимальное время ожидания для FIQ и RIQ – это самое короткое время запроса, которое может потребоваться на реакцию синхронизатора, сложенное с временем необходимым для входа в обработчик прерывания, что в сумме составляет 4 процессорных цикла для “классического” процессора ARM.