- •1. Вычислительный цикл процессора.

- •2. Вентили и логические элементы.

- •3. Понятие архитектуры и микроархитектуры. Классификация вычислительных средств по архитектуре (классификация Флинна).

- •4. Микропроцессор (мп). Состав и основные функции. Процессоры risc и cisc.

- •5. Архитектура ia-32. Режимы работы процессора.

- •6. Архитектура ia-32. Особенности представления информации.

- •7. Архитектура ia-32. Регистры общего назначения и сегментные регистры.

- •8. Архитектура ia-32. Регистры смещений и регистр флагов.

- •9. Архитектура ia-32. Организация памяти.

- •10. Архитектура ia-32. Организация прерываний.

- •11. Ассемблер. Области применения. Достоинства и недостатки.

- •12. Ассемблер. Структура программы. Модель памяти small.

- •13. Ассемблер. Основные типы предложений.

- •14. Ассемблер. Описание сегмента данных.

- •15. Ассемблер. Способы адресации памяти.

- •16. Ассемблер. Команды пересылки данных. Арифметические команды

- •17. Ассемблер. Команды переходов. Процедуры.

- •18. Ассемблер. Команды управления циклами. Команды прерывания.

- •19. Запоминающие устройства. Иерархичная организация памяти. Основные показатели быстродействия системы памяти.

- •20. Физические основы работы внутренней памяти. Энергозависимая память.

- •21. Внутренняя энергонезависимая память.

- •22. Аппаратно-программные методы ускорения обработки данных. Распараллеливание операции

- •23. Аппаратно-программные методы ускорения обработки данных. Кэширование памяти.

- •24. Кэш прямого отображения. Наборно-ассоциативный и ассоциативный кэш.

- •25. Микроархитектурные особенности процессоров x86 I-V поколений.

- •26. Микроархитектурные особенности процессоров x86 VI поколений.

- •27. Микроархитектура NetBurst и Intel Core.

- •28. Архитектура ia-64.

28. Архитектура ia-64.

Архитектура IA-64 (не путать с 64-битной x86-64)

Процессоры Intel Itanium, Itanium 2.

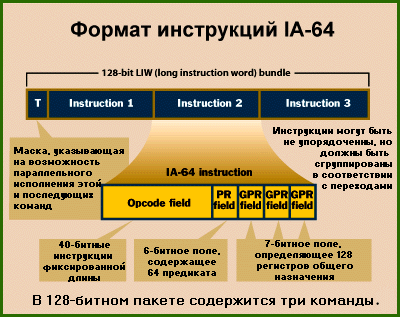

Разработана совместно компаниями Intel и HP. Имеет VLIW (Very Long Instruction Word) архитектуру (некий компромисс между CISC и RISC). Основная идея – все принципы повышения производительности, отмеченные выше, реализуются не аппаратно (увеличение сложности логики), а программно, с помощью компиляторов. Программист пишет инструкции с помощью команд x86 (или более высокоуровневого программирования), эти инструкции с помощью специального программного обеспечения низкого уровня транслируются в длинные слова регулярной структуры длиной 128 бит (по три инструкции x86 в одно 128 битое слово), которые и исполняются процессорным ядром.

Каждая длинная команда содержит шаблон (template) длиной в несколько бит, помещаемый в него компилятором, который указывает процессору, какие из команд могут выполняться параллельно. То есть процессору не нужно анализировать поток команд в процессе выполнения для выявления "скрытого параллелизма" (что существенно упрощает его аппаратную реализацию). Определение наличия параллелизма возлагается на компилятор, который и помещает эту информацию в код программы. Каждая команда содержит три 7-битных поля регистра общего назначения (РОН). 128 РОН.

Для устранения негативного влияния условных переходов компиляторы используют технологию "отмеченных команд" (predication). Когда процессор встречает "отмеченное" ветвление, он начинает одновременно выполнять все ветви. После того, как будет определена "истинная" ветвь, процессор сохраняет необходимые результаты и сбрасывает остальные.

Компиляторы для IA-64 будут также просматривать исходный код с целью поиска команд, использующих данные из памяти. Найдя такую команду, они будут добавлять пару команд - команду предварительной загрузки (speculative loading) и проверки загрузки (speculative check). Во время выполнения программы первая из команд загружает данные в память до того, как они понадобятся программе. Вторая команда проверяет, успешно ли произошла загрузка, перед тем, как разрешить программе использовать эти данные. Предварительная загрузка позволяет уменьшить потери производительности из-за задержек при доступе к памяти, а также повысить параллелизм.

Российская разработка – процессор Эльбрус Е2К, выполненная под руководством члена-корреспондента РАН Б.А.Бабаяна, тоже имело VLIW архитектуру.

Процессоры RISC архитектуры

Семейство PowerPC

Первый процессор Power 601 разработан альянсом фирм IBM/Apple/Motorola в 1993 г. Особенности:

32-рярядный, шина адреса тоже 32 разрядная (до 4 ГБ адресуемой памяти), шина данных – 64 разрядная. Тактовая частота – 50, 66 и 80 МГц. Все команды имеют один формат (трехоперандный). В RISC архитектуре данные в исполнительные блоки могут загружаться только из регистров, поэтому способов адресации не много. Инструкции разделены на два типа: команды обмена данными между регистрами и памятью и команды выполнения арифметических действий. Имеются три исполнительных устройства: целочисленное (IU), обработки чисел с плавающей запятой (FPU) и обработки переходов (BPU) – предсказывающий условные переходы. Все исполнительные устройства могут работать параллельно. За один такт могло выполняться до 3-х инструкций. Имелся раздельный кэш для команд и данных по 32 КБ (16+16). Существовал буфер команд (до 8 команд) в пределах которого, последние 4 команды могли выполнятся с нарушением предписанной последовательности их выполнения с целью эффективной загрузки исполнительный блоков. Затем были выпущены модели 602, 603, 604 и различные их модификации, отличающиеся, в основном, частотой, энергопотреблением, размерами КЭШа. Эти процессоры использовались, в основном в семействе персональных компьютеров PowerMac фирмы Apple.

МП Power 620

Полностью 64 разрядный процессор.

Размеры КЕШ-памяти увеличены до 32 Кб каждая. Появилась внешняя кэш-память второго уровня до 128 МБ. Введены усовершенствования в исполнительные блоки, особенно блока для работы с числами с плавающей запятой. Реализован механизм переименования регистров. Тактовая частота увеличена до 133 МГц. Адресная шина – 128 бит, шина данных – 40 бит. За один такт выполнялось до 4-х инструкций.

МП Power 750

Кэш второго уровня стал внутренним (работающим на полной тактовой частоте процессора) объемом до 1 МБ. Были эволюционно усовершенствованы исполнительные блоки. Частоты достигли 300-600 МГц.

МП POWER4 и POWER5

Разработан в 2001 г. Представляет собой два процессорных ядра на одном кристалле. Процессоры содержат раздельную кэш-память команд и данных 1-го уровня объемом по 64 Кбайт каждая. Кроме того, имеется разделяемая (общая) кэш-память 2-го уровня на кристалле (объемом 1,4 Мбайт) и внешняя кэш-память 3-го уровня (32 Мбайт). Для создания мультипроцессорных конфигураций имеются специальные линки с высокой пропускной способностью (частота более 500 МГц, ширина 128 бит). Теги кэш-памяти 3-го уровня расположены внутри кристалла, что ускоряет реализацию протокола когерентности. Скорость передачи данных между кэш-памятью 3-го уровня и основной памятью может достигать 12,8 Гбайт/с. Развитием этого процессора стал МП POWER5. Тактовая частота POWER5 составляет от 1,5 до 1,9 ГГц. Одно из главных новшеств это интегрированная кэш-память 3-го уровня объемом 36 Мбайт. Также был проведен ряд усовершенствований, направленных, в основном на повышение масштабируемости. Эти процессоры активно применяются для создания суперкомпьютеров и больших ВМ.

Менее популярными RISC процессорами являются МП семейства SPARC (Масштабируемая процессорная архитектура) фирмы SUN Microsystems. Это свободный стандарт, ориентированный на работу в ОС UNIX и языки программирования C. К его разработке могут присоединяться другие фирмы-изготовители процессоров. Это гарантирует им мощную поддержку со стороны ПО. Примерно такая же концепция использовалась при разработке процессоров Alpha фирмы DEC.