- •Часть 1: схемотехника дискретных цифровых устройств

- •160905 (201300) - «Техническая эксплуатация транспортного

- •Дополнительная

- •Введение

- •Раздел 1. Основы цифровой электроники

- •1.1. Арифметические и логические основы цифровой электроники

- •Тема 1. Дискретные бинарные сигналы и двоичные цифровые коды

- •1.1. Цифровая электроника.

- •1.2. Цифровой двоичный (бинарный) сигнал и двоичные коды.

- •1.3. Запись положительных чисел в виде двоичных кодов.

- •1.4. Двоичные коды чисел со знаком.

- •1.5. Восьмиричная и шестнадцатиричная кодировка чисел и перекодировка двоичных кодов.

- •Тема 2. Арифметика числовых двоичных и двоично-десятичных кодов

- •2.1. Арифметические операции над двоичными числовыми кодами.

- •Тема 3. Логические операции над двоичными кодами

- •3.1. Простейшие логические операции.

- •3.2. Базисы цифровых логических устройств. Комбинированные логические элементы.

- •Тема 4. Микросхемы логических операций

- •1.2. Анализ и синтез цифровых логических устройств

- •Тема 5. Алгебра логики для анализа и синтеза

- •5.1. Алгебра логики, ее законы и постулаты в виде тождеств.

- •5.2. Анализ цифровых комбинационных устройств азбукой логики.

- •5.3. Цели и этапы синтеза цифрового комбинационного устройства.

- •5.4. Составление уравнения состояний выхода по таблице истинности.

- •5.5. Минимизация уравнения состояний выхода с помощью карт Карно.

- •5.6. Пример синтеза цифрового логического устройства.

- •5.7. Пример синтеза с минимизацией картами Карно.

- •Раздел 2. Типовые функциональные узлы логических устройств цифовой электроники

- •2.1. Комбинационные цифровые устройства

- •Тема 6. Дешифраторы

- •6.1. Определение и классификация дешифраторов.

- •6.2. Принципы построения дешифратора двоичных кодов.

- •6.3. Примеры микросхемного исполнения дешифраторов и наращивания их разрядности.

- •Тема 7. Шифраторы

- •7.1. Определение и классификация шифраторов.

- •7.2. Принципы построения шифратора в двоичный код.

- •7.3. Примеры микросхемного исполнения шифраторов и наращивания их разрядности.

- •7.4. Использование пары шифратор-дешифратор в линиях связи.

- •Тема 8. Универсальный преобразователь двоичных кодов. Логическая программируемая матрица (лпм)

- •8.1.Принцип универсального преобразования кодов.

- •8.2. Принципы построения двухступенчатых схем преобразователей двоичных кодов.

- •8.3. Логические программируемые матрицы (лпм).

- •8..4. Пример микросхемного многоэтапного преобразования кодов и наращивания разрядности преобразования.

- •Тема 9. Двоичные сумматоры

- •9.1. Одноразрядные и многоразрядные последовательные сумматоры.

- •9.2. Принципы построения полного одноразрядного двоичного сумматора

- •Тема 10. Компараторы числовых двоичных кодов

- •10.1. Принцип сравнения многоразрядных числовых двоичных кодов.

- •10.2. Принципы построения компараторов двоичных числовых кодов.

- •Тема 11. Арифметико-логические устройства

- •Тема 12 мультиплексоры

- •12.1. Определение и классификация мультиплексоров.

- •12.2. Принципы построения мультиплексора.

- •12.3. Микросхемное исполнение мультиплексоров и наращивание их разрядности.

- •12.4. Использование мультиплексора для реализации логической переключательной функции.

- •Тема 13. Демультиплексоры

- •13.1. Определение и классификация демультиплексоров.

- •13.2. Принципы построения демультиплексора.

- •13.3. Микросхемное исполнение демультиплексоров и наращивание их разрядности.

- •Тема 14. Мультиплексированние и демультиплексирование линий цифровой связи

- •14.1. Цель и принцип мультиплексирования линии передачи цифровых данных.

- •14.2. Способы минимизации количества линий связи при мультиплексированной передаче цифровых данных.

- •2.2. Последовательностные цифровые устройства

- •Тема 15. Классификация и обозначения триггеров

- •Тема 16. Триггеры с потенциальным управлением

- •Тема 17. Триггеры с динамическим управлением

- •17.1. Двухтактные триггеры с динамическим управлением.

- •17.2. Однотактный d-триггер Веба.

- •17.3. Примеры микросхемного исполнения триггеров.

- •Тема 18. Регистры для записи и хранения двоичных кодов

- •18.1. Определение и классификация регистров.

- •18.2. Параллельная потенциальная запись кода в регистр.

- •18.3. Динамическая параллельная запись кода в регистр.

- •18.4. Сдвиговой регистр с параллельным или последовательным считыванием кодов и с динамическим входом управления записью.

- •18.5. Реверсивный сдвиговой регистр.

- •18.5. Примеры микросхемного исполнения регистров.

- •Тема 19. Счетчики импульсов с последовательным переносом

- •19.1. Определение и классификация счетчиков импульсов.

- •19.2. Счетчик Джонсона на базе сдвигового регистра.

- •19.3. Асинхронные счетчики импульсов с весовым кодом показаний и последовательным переносом.

- •19.3.1. Суммирующий счетчик.

- •19.3.2. Вычитающий счетчик.

- •19.4. Быстродействие счетчиков с последовательным переносом.

- •Тема 20. Счетчики импульсов с параллельным и сквозным переносом

- •20.1. Определение и особенности счетчиков импульсов с параллельным и сквозным переносом.

- •20.2. Суммирующие счетчики импульсов с параллельным переносом.

- •20.3. Суммирующие счетчики со сквозным переносом.

- •20.4 Вычитающие счетчики с параллельным или сквозным переносом.

- •Тема 21. Счетчики-делители частоты импульсов с произвольным коэффициентом пересчета

- •21.1. Определение и классификация счетчиков-делителей частоты импульсов с произвольным коэффициентом пересчета.

- •21.2. Счетчики импульсов с ограничением предела счета «сверху» с помощью дешифратора показаний счетчика.

- •21.3. Счетчики-делители частоты импульсов с ограничением предела счета «снизу» дешифратором нулевого состояния триггеров.

- •Тема 23. Цифровые автоматы

- •23.1. Понятие о цифровом автомате, его логической схеме и графе его состояний.

- •23.2.Методика анализа и синтеза цифрового автомата.

- •23.3. Пример реализации цифрового автомата в виде декадного счетчика-делителя с нулевым исходным показанием.

- •Тема 24. Микросхемы счетчиков импульсов

- •24.1. Каскадирование микросхем счетчиков.

- •24.2. Микросхемы счетчиков импульсов и счетчиков-делителей частоты импульсов.

- •24.3.Способы управления коэффициентом деления микросхемных счетчиков и счетчиков-делителей.

- •Раздел 3. Элементная база цифровой электроники

- •Тема 25. Базовые логические элементы (блэ), их характеристики и параметры

- •25.1. Понятие базового логического элемента.

- •25.2. Статическая характеристики и статические параметры блэ.

- •25.3. Динамические характеристики и параметры блэ.

- •25.4. Релейные, диодные и непосредственно связанные транзисторные логические элементы (нстл).

- •25.5. Диодно-транзисторные блэ, их статические и динамические параметры.

- •Тема 26.Блэ транзисторно-транзисторной логики (ттл)

- •26.1. Блэ ттл с логикой и-не.

- •26.2. Блэ ттл с логикой и-или-не.

- •26.3. Статические и динамические параметры блэ ттл.

- •26.4. Модификации инверторов блэ ттл.

- •Тема 27. Блэ на транзисторах и диодах шотки (ттлш и дтлш)

- •27.1. Транзисторы Шотки.

- •27.2. Энергосберегающие и быстродействующие блэ ттлш и дтлш.

- •Тема 28. Блэ эмиттерно-связанной логики (эсл)

- •28.1. Электронный ключ с переключением тока.

- •Тема 29. Логические элементы интегрально-инжекционной технологии (и2л)

- •Тема 30. Блэ на полевых транзисторах

- •30.1. Электронные ключи на полевых транзисторах.

- •30.2. Блэ на моп-транзисторах.

- •Тема 31. Сравнительные статические и динамические параметры блэ различных технологий.

- •3.2. Схемотехника устройств адресного хранения цифровых кодов

- •Тема 32. Структура и параметры устройств адресного хранения цифровых кодов

- •32.1. Классификация устройств памяти.

- •32.2. Комплексирование микросхем в устройствах адресного хранения цифровых кодов.

- •32.3. Структура микросхем адресуемой памяти большого объема.

- •Тема 33. Ячейки памяти

- •33.1. Принципы построения ячеек памяти пзу.

- •33.2. Принципы построения ячеек памяти ппзу.

- •33.3. Принципы построения ячеек памяти озу.

- •Раздел 4. Формирователи, генераторы и преобразователи сигналов цифровых уровней

- •4.1. Формирователи и генераторы импульсов

- •Тема 34. Формирователи цифровых сигналов

- •34.2. Формирователи стробов.

- •Тема 35. Генераторы импульсных цифровых сигналов

- •35.1. Определения и классификация.

- •35.2. Ждущие генераторы импульсов (одновибраторы).

- •35.3. Автогенераторы импульсов (мультивибраторы).

- •35.4. Микросхемы генераторов импульсов.

- •Тема 36. Универсальный микросхемный интервальный таймер

- •4.2. Сопряжение цифровых устройств с периферий-ными устройствами

- •Тема 37. Решения проблем сопряжения цифровых устройств с периферийными устройствами

- •37.1. Периферия цифровых устройств.

- •37.2. Сопряжение цифровых устройств с позиционными и нажимными датчиками.

- •37.3. Сопряжение цифровых устройств с знакосинтезирующими индикаторами.

- •37.4 Сопряжение цифровых устройств с мощными релейными исполнительными устройствами. Дистанционное управление цифровыми устройствами.

- •Тема 38. Проблемы и принципы сопряжения цифровых устройств с аналоговой периферией

- •Тема 39. Цифро-аналоговые преобразователи (цап)

- •39.1. Принципы построения цап.

- •39.2. Цап с весовыми резисторами.

- •39.3. Цап на основе матрицы r-2r.

- •39.4. Микросхемное исполнение цап.

- •Тема 40. Аналого-цифровые преобразователи (ацп)

- •40.1. Ацп последовательного счета с цап.

- •40.2. Ацп последовательного счета с двойным интегрированием.

- •40.3. Ацп поразрядного уравновешивания (поразрядного кодирования).

- •40.4. Ацп параллельного сравнения.

- •40.4. Микросхемное исполнение ацп.

- •Заключение

- •1.1. Арифметические и логические основы цифровой электроники

- •2.1. Комбинационные цифровые устройства

- •2.2. Последовательностные цифровые устройства

- •3.2. Схемотехника устройств адресного хранения цифровых кодов

- •4.1. Формирователи и генераторы импульсов

- •4.2. Сопряжение цифровых устройств с периферийными устройствами

25.3. Динамические характеристики и параметры блэ.

Динамические характеристики БЛЭ определяют по искажениям формы импульса на выходе логического элемента относительно формы входного импульса.

Определение искажений осуществляется путем сравнения осциллограмм входного и выходного импульса БЛЭ. Входной сигнал в виде импульса подается на один из входов логического элемента, а на другие входы подается постоянное напряжение, уровень которого должен обеспечить возможность изменения выходного сигнала при воздействии этого импульса.

На Рис.64b показаны типичные осциллограммы при импульсном воздействии на один из входов БЛЭ с выходным инвертором (например, на логический элемент И-НЕ при подаче на остальные входы напряжения уровня логической «единицы»).

По осциллограммам определяются динамические параметры БЛЭ, к которым относятся задержка фронта импульса tФ и задержка среза tC импульса, как правило, отличающиеся друг от друга, поэтому может использоваться среднеарифметическое значение этих задержек.

Производной от среднего времени задержки БЛЭ является обратная ей максимально допустимая частота переключения БЛЭ.

Для логических устройств, срабатывающих на положительный или отрицательный перепад логических уровней, важными дополнительными динамическими параметрами является максимально допустимая длительность перепада уровней, называемая, соответственно, максимальной длительностью фронта или максимальной длительностью среза входного импульса.

Динамические параметры БЛЭ, также как и статические параметры, зависят от величины нагрузки выхода БЛЭ и дестабилизирующих факторов, поэтому их определяют при максимально неблагоприятных, но допустимых значениях этих факторов.

25.4. Релейные, диодные и непосредственно связанные транзисторные логические элементы (нстл).

Исторически первыми в качестве электрически управляемых логических элементов стали использоваться электромеханические реле.

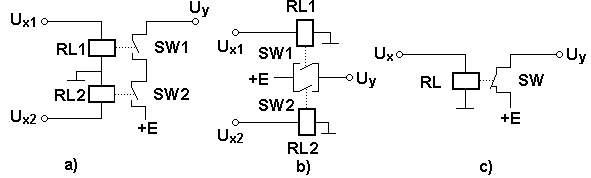

На Рис.65 показаны схемы подключения таких реле с нормально разомкнутыми контактами для реализации логической операции И (Рис.65а) и логической схемы ИЛИ (Рис.65b). Как видно из рисунков, логика формирования выходного сигнала UY от источника напряжения +Е контактами реле из входных сигналов UX, подаваемых на обмотки реле, определяется последовательной или параллельной схемой включения контактов реле.

Рис.65

При использовании реле с нормально замкнутым контактом реализуется логическая операция НЕ (Рис.65с).

Достоинствами релейных логических схем является возможность работы при высоких уровнях выходных логических сигналов, а также возможность работы в условиях высокого уровня помех и наличия широкодиапазонных дестабилизирующих факторов. В релейных БЛЭ легко реализуются высокие коэффициенты объединения по входу и коэффициенты разветвления по выходу.

В современной технике большие габариты и вес релейных логических схем, а также их низкое быстродействие обеспечивают им весьма узкую область применения, например - в мощной силовой электроавтоматике.

Простейшие электронные малогабаритные логические элементы могут быть реализованы с использованием диодной схемотехники.

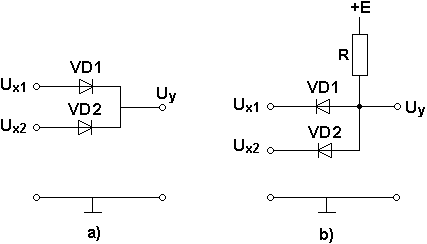

БЛЭ диодной схемотехники включают в себя логические схемы ИЛИ и логические схемы И, принцип включения диодов в которых показан на Рис.66а и Рис.66b, соответственно.

Рис.66

В схеме на Рис.66а диоды при объединении нескольких источников входных сигналов на общую нагрузку выполняют роль элементов, предохраняющих входные цепи с низким уровнем логического сигнала от проникновения с этой нагрузки сигналов высоких логических уровней.

В схеме на Рис.66b только отсутствие токов через все диоды при высоких логических уровнях их входных сигналов или при разрыве входных соединительных проводов приводит к высокому уровню выходного сигнала.

Схемы диодной логики легко реализуются на диодах в виде отдельных электронных приборов. Уровни входных сигналов определяются типом используемых диодов, а быстродействие ограничено только быстродействием этих приборов и временем перезаряда паразитных внутрисхемных емкостей.

Но схемы диодной логики не позволяют получить ни высокий коэффициент объединения по входу из-за влияния числа входных диодов и разброса их токов на логические уровни выходных сигналов, ни высокий коэффициент разветвления по выходу из-за шунтирования сопротивлением нагрузки входных диодных цепей.

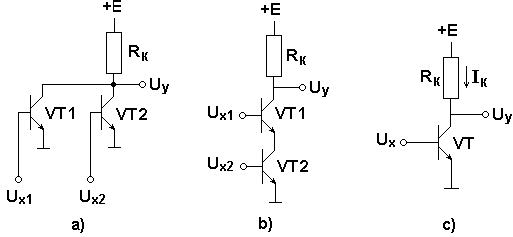

На Рис.67 показаны схемы логических элементов непосредственно связанной транзисторной логики (НСТЛ), реализующих логическую операцию ИЛИ-НЕ (вариант а), логическую операцию И-НЕ (вариант b), а также транзисторный вариант логической операции НЕ (вариант с).

Рис.67

Транзисторы НСТЛ могут иметь два состояния: транзистор закрыт – минимальный ток коллектора, но максимальное напряжение UY (логическая «единица»), транзистор открыт - максимальный ток коллектора с насыщением при минимальном напряжении UY (логический «ноль»).

Насыщение транзистора в открытом состоянии является средством борьбы с, так называемыми, дестабилизирующими факторами.

К таким факторам относят, в частности, нестабильность источника электропитания, технологический разброс параметров транзисторов и резисторов, а также температурная нестабильность этих параметров.

Логические элементы НСТЛ, по аналогичным диодной логике причинам, имеют малые коэффициенты объединения по входу и коэффициенты разветвления по выходу.

В частности, при закрытом транзисторе инвертора увеличивающийся ток I k из-за увеличения тока нагрузки снижает уровень выходного сигнала логической «единицы».

БЛЭ НСТЛ на биполярных транзисторах не нашли широкого применения, несмотря на простоту их реализации на отдельных электронных приборах.