- •Часть 1: схемотехника дискретных цифровых устройств

- •160905 (201300) - «Техническая эксплуатация транспортного

- •Дополнительная

- •Введение

- •Раздел 1. Основы цифровой электроники

- •1.1. Арифметические и логические основы цифровой электроники

- •Тема 1. Дискретные бинарные сигналы и двоичные цифровые коды

- •1.1. Цифровая электроника.

- •1.2. Цифровой двоичный (бинарный) сигнал и двоичные коды.

- •1.3. Запись положительных чисел в виде двоичных кодов.

- •1.4. Двоичные коды чисел со знаком.

- •1.5. Восьмиричная и шестнадцатиричная кодировка чисел и перекодировка двоичных кодов.

- •Тема 2. Арифметика числовых двоичных и двоично-десятичных кодов

- •2.1. Арифметические операции над двоичными числовыми кодами.

- •Тема 3. Логические операции над двоичными кодами

- •3.1. Простейшие логические операции.

- •3.2. Базисы цифровых логических устройств. Комбинированные логические элементы.

- •Тема 4. Микросхемы логических операций

- •1.2. Анализ и синтез цифровых логических устройств

- •Тема 5. Алгебра логики для анализа и синтеза

- •5.1. Алгебра логики, ее законы и постулаты в виде тождеств.

- •5.2. Анализ цифровых комбинационных устройств азбукой логики.

- •5.3. Цели и этапы синтеза цифрового комбинационного устройства.

- •5.4. Составление уравнения состояний выхода по таблице истинности.

- •5.5. Минимизация уравнения состояний выхода с помощью карт Карно.

- •5.6. Пример синтеза цифрового логического устройства.

- •5.7. Пример синтеза с минимизацией картами Карно.

- •Раздел 2. Типовые функциональные узлы логических устройств цифовой электроники

- •2.1. Комбинационные цифровые устройства

- •Тема 6. Дешифраторы

- •6.1. Определение и классификация дешифраторов.

- •6.2. Принципы построения дешифратора двоичных кодов.

- •6.3. Примеры микросхемного исполнения дешифраторов и наращивания их разрядности.

- •Тема 7. Шифраторы

- •7.1. Определение и классификация шифраторов.

- •7.2. Принципы построения шифратора в двоичный код.

- •7.3. Примеры микросхемного исполнения шифраторов и наращивания их разрядности.

- •7.4. Использование пары шифратор-дешифратор в линиях связи.

- •Тема 8. Универсальный преобразователь двоичных кодов. Логическая программируемая матрица (лпм)

- •8.1.Принцип универсального преобразования кодов.

- •8.2. Принципы построения двухступенчатых схем преобразователей двоичных кодов.

- •8.3. Логические программируемые матрицы (лпм).

- •8..4. Пример микросхемного многоэтапного преобразования кодов и наращивания разрядности преобразования.

- •Тема 9. Двоичные сумматоры

- •9.1. Одноразрядные и многоразрядные последовательные сумматоры.

- •9.2. Принципы построения полного одноразрядного двоичного сумматора

- •Тема 10. Компараторы числовых двоичных кодов

- •10.1. Принцип сравнения многоразрядных числовых двоичных кодов.

- •10.2. Принципы построения компараторов двоичных числовых кодов.

- •Тема 11. Арифметико-логические устройства

- •Тема 12 мультиплексоры

- •12.1. Определение и классификация мультиплексоров.

- •12.2. Принципы построения мультиплексора.

- •12.3. Микросхемное исполнение мультиплексоров и наращивание их разрядности.

- •12.4. Использование мультиплексора для реализации логической переключательной функции.

- •Тема 13. Демультиплексоры

- •13.1. Определение и классификация демультиплексоров.

- •13.2. Принципы построения демультиплексора.

- •13.3. Микросхемное исполнение демультиплексоров и наращивание их разрядности.

- •Тема 14. Мультиплексированние и демультиплексирование линий цифровой связи

- •14.1. Цель и принцип мультиплексирования линии передачи цифровых данных.

- •14.2. Способы минимизации количества линий связи при мультиплексированной передаче цифровых данных.

- •2.2. Последовательностные цифровые устройства

- •Тема 15. Классификация и обозначения триггеров

- •Тема 16. Триггеры с потенциальным управлением

- •Тема 17. Триггеры с динамическим управлением

- •17.1. Двухтактные триггеры с динамическим управлением.

- •17.2. Однотактный d-триггер Веба.

- •17.3. Примеры микросхемного исполнения триггеров.

- •Тема 18. Регистры для записи и хранения двоичных кодов

- •18.1. Определение и классификация регистров.

- •18.2. Параллельная потенциальная запись кода в регистр.

- •18.3. Динамическая параллельная запись кода в регистр.

- •18.4. Сдвиговой регистр с параллельным или последовательным считыванием кодов и с динамическим входом управления записью.

- •18.5. Реверсивный сдвиговой регистр.

- •18.5. Примеры микросхемного исполнения регистров.

- •Тема 19. Счетчики импульсов с последовательным переносом

- •19.1. Определение и классификация счетчиков импульсов.

- •19.2. Счетчик Джонсона на базе сдвигового регистра.

- •19.3. Асинхронные счетчики импульсов с весовым кодом показаний и последовательным переносом.

- •19.3.1. Суммирующий счетчик.

- •19.3.2. Вычитающий счетчик.

- •19.4. Быстродействие счетчиков с последовательным переносом.

- •Тема 20. Счетчики импульсов с параллельным и сквозным переносом

- •20.1. Определение и особенности счетчиков импульсов с параллельным и сквозным переносом.

- •20.2. Суммирующие счетчики импульсов с параллельным переносом.

- •20.3. Суммирующие счетчики со сквозным переносом.

- •20.4 Вычитающие счетчики с параллельным или сквозным переносом.

- •Тема 21. Счетчики-делители частоты импульсов с произвольным коэффициентом пересчета

- •21.1. Определение и классификация счетчиков-делителей частоты импульсов с произвольным коэффициентом пересчета.

- •21.2. Счетчики импульсов с ограничением предела счета «сверху» с помощью дешифратора показаний счетчика.

- •21.3. Счетчики-делители частоты импульсов с ограничением предела счета «снизу» дешифратором нулевого состояния триггеров.

- •Тема 23. Цифровые автоматы

- •23.1. Понятие о цифровом автомате, его логической схеме и графе его состояний.

- •23.2.Методика анализа и синтеза цифрового автомата.

- •23.3. Пример реализации цифрового автомата в виде декадного счетчика-делителя с нулевым исходным показанием.

- •Тема 24. Микросхемы счетчиков импульсов

- •24.1. Каскадирование микросхем счетчиков.

- •24.2. Микросхемы счетчиков импульсов и счетчиков-делителей частоты импульсов.

- •24.3.Способы управления коэффициентом деления микросхемных счетчиков и счетчиков-делителей.

- •Раздел 3. Элементная база цифровой электроники

- •Тема 25. Базовые логические элементы (блэ), их характеристики и параметры

- •25.1. Понятие базового логического элемента.

- •25.2. Статическая характеристики и статические параметры блэ.

- •25.3. Динамические характеристики и параметры блэ.

- •25.4. Релейные, диодные и непосредственно связанные транзисторные логические элементы (нстл).

- •25.5. Диодно-транзисторные блэ, их статические и динамические параметры.

- •Тема 26.Блэ транзисторно-транзисторной логики (ттл)

- •26.1. Блэ ттл с логикой и-не.

- •26.2. Блэ ттл с логикой и-или-не.

- •26.3. Статические и динамические параметры блэ ттл.

- •26.4. Модификации инверторов блэ ттл.

- •Тема 27. Блэ на транзисторах и диодах шотки (ттлш и дтлш)

- •27.1. Транзисторы Шотки.

- •27.2. Энергосберегающие и быстродействующие блэ ттлш и дтлш.

- •Тема 28. Блэ эмиттерно-связанной логики (эсл)

- •28.1. Электронный ключ с переключением тока.

- •Тема 29. Логические элементы интегрально-инжекционной технологии (и2л)

- •Тема 30. Блэ на полевых транзисторах

- •30.1. Электронные ключи на полевых транзисторах.

- •30.2. Блэ на моп-транзисторах.

- •Тема 31. Сравнительные статические и динамические параметры блэ различных технологий.

- •3.2. Схемотехника устройств адресного хранения цифровых кодов

- •Тема 32. Структура и параметры устройств адресного хранения цифровых кодов

- •32.1. Классификация устройств памяти.

- •32.2. Комплексирование микросхем в устройствах адресного хранения цифровых кодов.

- •32.3. Структура микросхем адресуемой памяти большого объема.

- •Тема 33. Ячейки памяти

- •33.1. Принципы построения ячеек памяти пзу.

- •33.2. Принципы построения ячеек памяти ппзу.

- •33.3. Принципы построения ячеек памяти озу.

- •Раздел 4. Формирователи, генераторы и преобразователи сигналов цифровых уровней

- •4.1. Формирователи и генераторы импульсов

- •Тема 34. Формирователи цифровых сигналов

- •34.2. Формирователи стробов.

- •Тема 35. Генераторы импульсных цифровых сигналов

- •35.1. Определения и классификация.

- •35.2. Ждущие генераторы импульсов (одновибраторы).

- •35.3. Автогенераторы импульсов (мультивибраторы).

- •35.4. Микросхемы генераторов импульсов.

- •Тема 36. Универсальный микросхемный интервальный таймер

- •4.2. Сопряжение цифровых устройств с периферий-ными устройствами

- •Тема 37. Решения проблем сопряжения цифровых устройств с периферийными устройствами

- •37.1. Периферия цифровых устройств.

- •37.2. Сопряжение цифровых устройств с позиционными и нажимными датчиками.

- •37.3. Сопряжение цифровых устройств с знакосинтезирующими индикаторами.

- •37.4 Сопряжение цифровых устройств с мощными релейными исполнительными устройствами. Дистанционное управление цифровыми устройствами.

- •Тема 38. Проблемы и принципы сопряжения цифровых устройств с аналоговой периферией

- •Тема 39. Цифро-аналоговые преобразователи (цап)

- •39.1. Принципы построения цап.

- •39.2. Цап с весовыми резисторами.

- •39.3. Цап на основе матрицы r-2r.

- •39.4. Микросхемное исполнение цап.

- •Тема 40. Аналого-цифровые преобразователи (ацп)

- •40.1. Ацп последовательного счета с цап.

- •40.2. Ацп последовательного счета с двойным интегрированием.

- •40.3. Ацп поразрядного уравновешивания (поразрядного кодирования).

- •40.4. Ацп параллельного сравнения.

- •40.4. Микросхемное исполнение ацп.

- •Заключение

- •1.1. Арифметические и логические основы цифровой электроники

- •2.1. Комбинационные цифровые устройства

- •2.2. Последовательностные цифровые устройства

- •3.2. Схемотехника устройств адресного хранения цифровых кодов

- •4.1. Формирователи и генераторы импульсов

- •4.2. Сопряжение цифровых устройств с периферийными устройствами

5.7. Пример синтеза с минимизацией картами Карно.

В качестве примера использования карт Карно для преобразования неполной таблицы истинности можно рассмотреть реализацию шифратора входных позиционных сигналов «1» в код управления четырехразрядной светодиодной шкалой.

Таблица истинности работы такого шифратора:

-

Входы

Выходы

X4

X3

X2

X1

Y4

Y3

Y2

Y1

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

1

1

0

0

1

1

1

0

1

1

1

1

Таблица, описывающая логику работы шифратора неполная, поскольку содержит только пять строк, соответствующих пяти из 16-ти возможных комбинаций входных сигналов. Это означает, что значения выходных сигналов при неуказанных ситуациях несущественны, так как их не будет на входах.

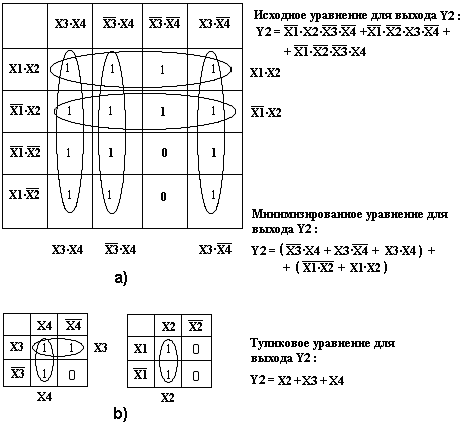

На Рис.8а, в качестве примера, показана заполненная карта Карно для выхода «Y2.

Рис.8

Пять значений пересечений строк и столбцов, заданные таблицей состояний этого выхода, выделены жирным шрифтом.

Остальные значения пересечений, указанные обычным шрифтом, проставлены таким образом, чтобы обеспечить полное «склеивание» выделенных жирным шрифтом значений «1» в своих строках или столбцах. Для этого произведено дополнение этих строк и столбцов значениями «1».

Результат «склеивания» полного столбца проставлен под соответствующим столбцом, а результат «склеивания» полной строки проставлен справа от соответствующей строки.

На Рис.8а «склеиваются» только полные строки и столбцы.

Для дальнейшего преобразования полученного после «склеивания» минимизированного уравнения необходимо использовать или алгебру логики или составить новые карты Карно для составляющих минимизированного уравнения состояний выхода Y2,которые выделены скобками. Эти составляющие имеют только два аргумента.

Преобразовав картами Карно скобки минимизированного уравнения, содержащие пары аргументов, как это показано на Рис.7b, можно получить следующее минимально возможное (тупиковое) уравнение: Y = X2 + X3 + X4.

Вопросы для самопроверки

1. Каковы основные этапы синтеза цифрового комбинационного устройства, и какие условия могут быть поставлены при его синтезе?

2. Каким образом по таблице истинности составляется уравнение состояний выхода цифрового комбинационного устройства в НДФ и НКФ?

3. Каковы два способа минимизации уравнения состояний выхода?

4. Как составляется и заполняется бланк Карты Карно при четном и нечетном числе аргументов уравнения состояний выхода, а также при полной и неполной таблице истинности, описывающей логику цифрового комбинационного устройства?

5. Почему одно и тоже значение «1» в карте Карно может использоваться при «склеивании» нескольких смежных строк и столбцов?

6. Какой результат при преобразовании карты Карно дают следующие строки:

содержащие только значения «1»;

содержащие только значения «0»;

содержащие четное число подряд стоящих значений «1», если остальные значения равны «0»;

содержащие нечетное число подряд стоящих значений «1», если остальные значения равны «0»?

7. Каков простейший вариант реализации логической операции «Исключающее ИЛИ» на базе логических элементов И-НЕ?

8. Какую логику будет иметь схема, соединения в которой соответствуют реализации логической операции «Исключающее ИЛИ» на элементах логических операций И-НЕ (см. Рис.7b), если в ней заменить эти элементы на элементы логических операций ИЛИ-НЕ?