- •Введение

- •В описании каждой лабораторной работы сформулированы ее цели, приводятся схемы и описание их работы, а также контрольные вопросы для подготовки к защите лабораторной работы. Лабораторная работа №1

- •Сельсинное измерительное устройство

- •Контрольные вопросы

- •Лабораторная работа №2

- •Контрольные вопросы

- •Лабораторная работа №3 Фазочувствительный выпрямитель

- •Фазочувствительный выпрямитель

- •Контрольные вопросы

- •Лабораторная работа №4 Задатчик интенсивности. Согласующий усилитель

- •Задатчик интенсивности

- •Согласующий усилитель

- •Контрольные вопросы

- •Лабораторная работа №5

- •Устройство сравнения

- •Устройство гальванической развязки

- •Контрольные вопросы

- •Лабораторная работа №6 блок регулятора

- •Блок регулятора

- •Контрольные вопросы

- •Библиографический список

- •Оглавление

Контрольные вопросы

1. Назначение фазочувствительного выпрямителя.

2. Назначение сумматора.

3. Работа типового фазочувствительного выпрямителя.

4. Работа двухполупериодного ключевого демодулятора.

5. Назначение перемычек в схеме выпрямителя.

6. Какие обратные связи имеет выпрямитель?

7. Диаграммы работы фазочувствительного выпрямителя.

8. Назначение двухполупериодного ключевого демодулятора.

9. Назначение реверсивного усилителя мощности.

10. Чем производится установка требуемого коэффициента мощности?

11. Защита от перенапряжений ОУ в режиме насыщения.

12. Устройство и назначение ключей в демодуляторе

Лабораторная работа №4 Задатчик интенсивности. Согласующий усилитель

Цель работы: Изучить назначение, работу задатчика интенсивности и соголасующего усилителя.

Задатчик интенсивности

Задатчик интенсивности предназначен для преобразования входного напряжения, приложенного скачком, в линейно зависимое от времени выходное напряжение, знак которого соответствует знаку, а установившееся напряжение - уровню входного напряжения. Темп изменения напряжения определяется только параметрами схемы задатчика.

В схемах управления электроприводами наибольшее распространение получил задатчик интенсивности, принципиальная схема которого и графические зависимости, поясняющие его работу, даны на рис.14.

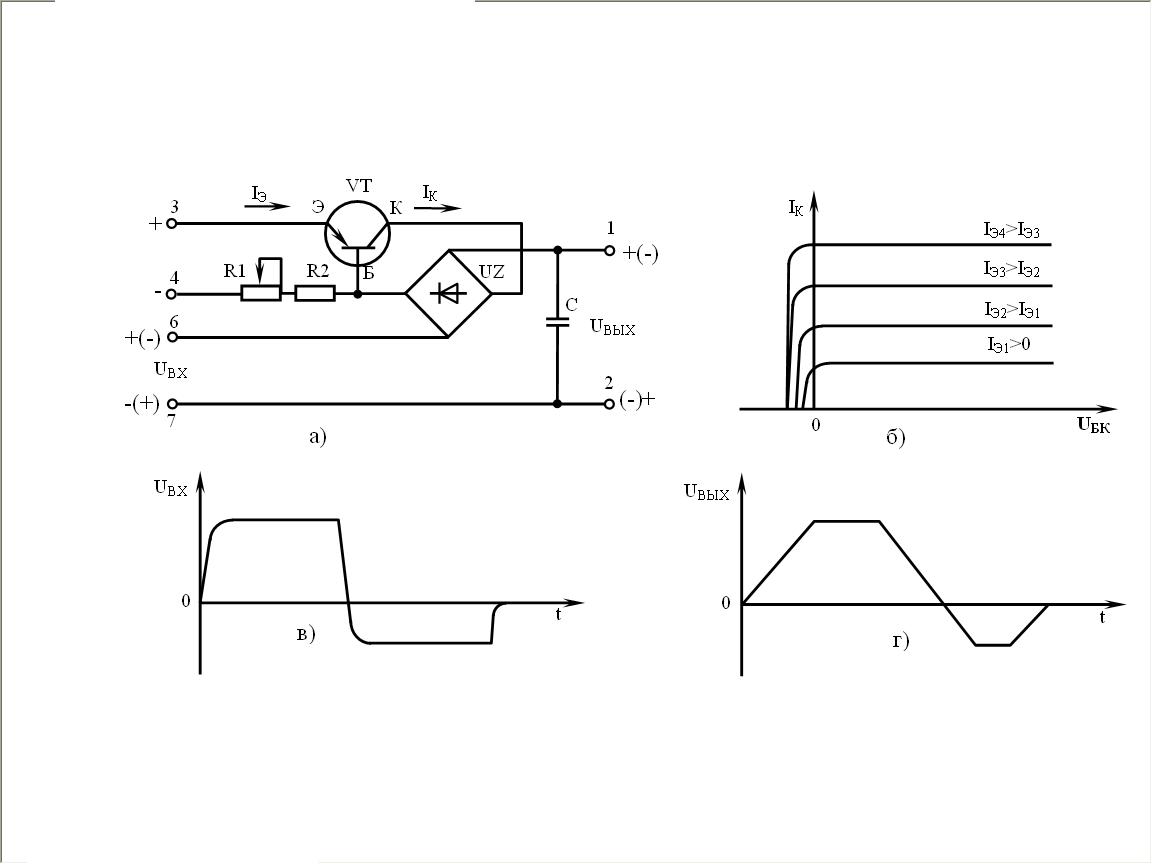

В данном случае используется один транзистор VT р-п-р проводимости, включенный по схеме с общей базой (рис. 14, а), для которой выходные характеристики Iк = f(UБК) при IЭ = const расположены практически параллельно оси абсцисс (рис. 14, б). Ток коллектора IК почти не зависит от напряжения база - коллектор UБК, а определяется током эмиттера IК, причем ІК = ІЭ.

Таким образом, транзистор VT работает как источник тока, значение которого может устанавливаться регулировкой сопротивления R1 или напряжения питания Un.

Рис.14 Принципиальная схема задатчика интенсивности АЈ (а), коллекторные характеристики транзистора VT (б), временная диаграмма uвх(t) (в) и соответствующая зависимость uвых(t) (г).

Ток коллектора IК вызывается входным напряжением Uвх, которое поступает на выводы 6, 7 с выхода фазочувствительного выпрямителя с той же нумерацией выводов. Если пренебречь током нагрузки схемы, то IК полностью будет протекать через накопительный конденсатор С, включенный последовательно в цепь коллектора через выпрямительный мост UZ, и вызовет его заряд. Напряжение на конденсаторе является выходным напряжением АЈ и изменяется по закону:

![]() (1)

(1)

В пределе конденсатор С может зарядиться только до Uвх, т. е. Uвых = Uвх, гдеUвых - установившееся значение выходного напряжения при Uвх = const.

На рис. 14, в и г показаны соответственно зависимости Uвх(t) и Uвых(t) данного задатчика интенсивности. На практике при отборе мощности в нагрузку, если ток нагрузки соизмерим с IК, зависимость (1) нарушается и uвых(t) носит экспоненциальный характер. Кроме того, при uвх=0 uвых может отличаться от нуля на значение прямого падения напряжения на диодах выпрямительного моста UZ.

Рис. 15 Принципиальная схема задатчика интенсивности АJ (а), временная диаграмма uВХ(t) (б) и соответствующие ей зависимости ua(t) (в) и uВЫХ(t) (г).

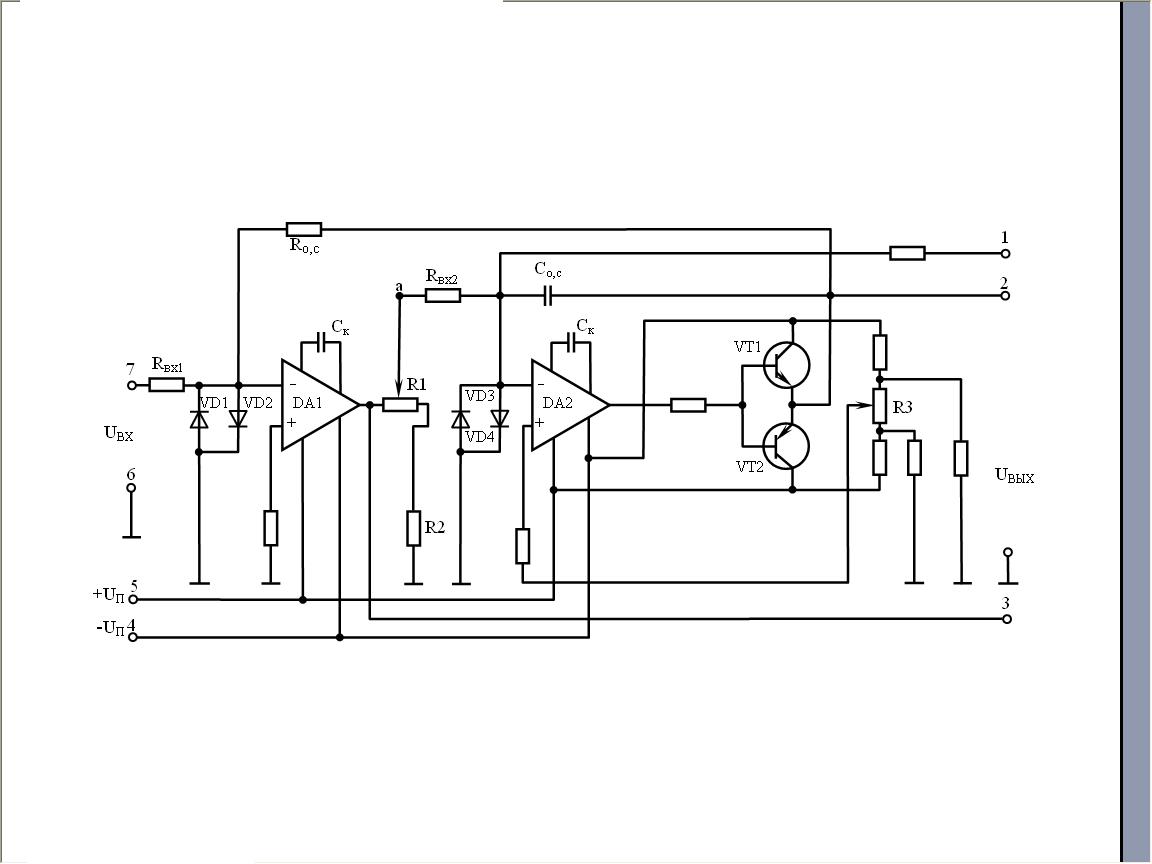

В схемах управления электроприводами реализованных с применением интегральных ОУ, используется более сложная и более совершенная принципиальная схема задатчика интенсивности AJ, которая вместе с поясняющими ее работу временными диаграммами представлена на рис. 15. Схема состоит из последовательно включенных компаратора и интегратора, охваченных отрицательной ОС. Компаратором является ОУ DA1, цепь ОС которого разорвана. Инвертирующий вход DA1 связан через резистор с общей точкой схемы, а на (+) вход через резисторы Rвх1 и Rо,с поданы соответственно напряжения uвх и uвых задатчика интенсивности.

Операционный усилитель DA1 в такой схеме включения представляет собой неинвертирующий компаратор, реализующий следующую дискретную функцию:

![]() (2)

(2)

где uвыхDA1 – напряжение выхода DA1; UвыхDAтах – максимальное напряжение выхода микросхемы; sign - знаковая функция.

Напряжение с выхода компаратора поступает на регулируемый делитель R1, R2, а с движка резистора R1 – на вход интегратора. Интегратор выполнен на последовательно включенных ОУ DA2 и реверсивном транзисторном усилителе мощности (VT1, VT2), охваченных общей отрицательной ОС через конденсатор Со,с. В ОУ DA2 для подачи входного сигнала использован (–) вход, а на (+) вход с движка R3 подано напряжение смещения, служащее для установки нуля ОУ DA2 и, следовательно, задатчика интенсивности в целом.

Напряжение на выходе интегратора является выходным для блока AJ и с учетом того, что |ua| = const определяется выражением:

![]() (3)

(3)

где ua – напряжение в точке а схемы, пропорциональное uвыхDA1; Uвых0 – начальное выходное напряжение.

Из (3) следует, что темп изменения выходного напряжения задатчика интенсивности определяется постоянной времени интегратора Rвх2Cо,с и входным напряжением интегратора uа.

Для регулирования производной выходного напряжения предусмотрено переменное сопротивление R1. Как и в других схемах, ОУ снабжены конденсаторами коррекции Ск и диодами защиты входных цепей VD1—VD.

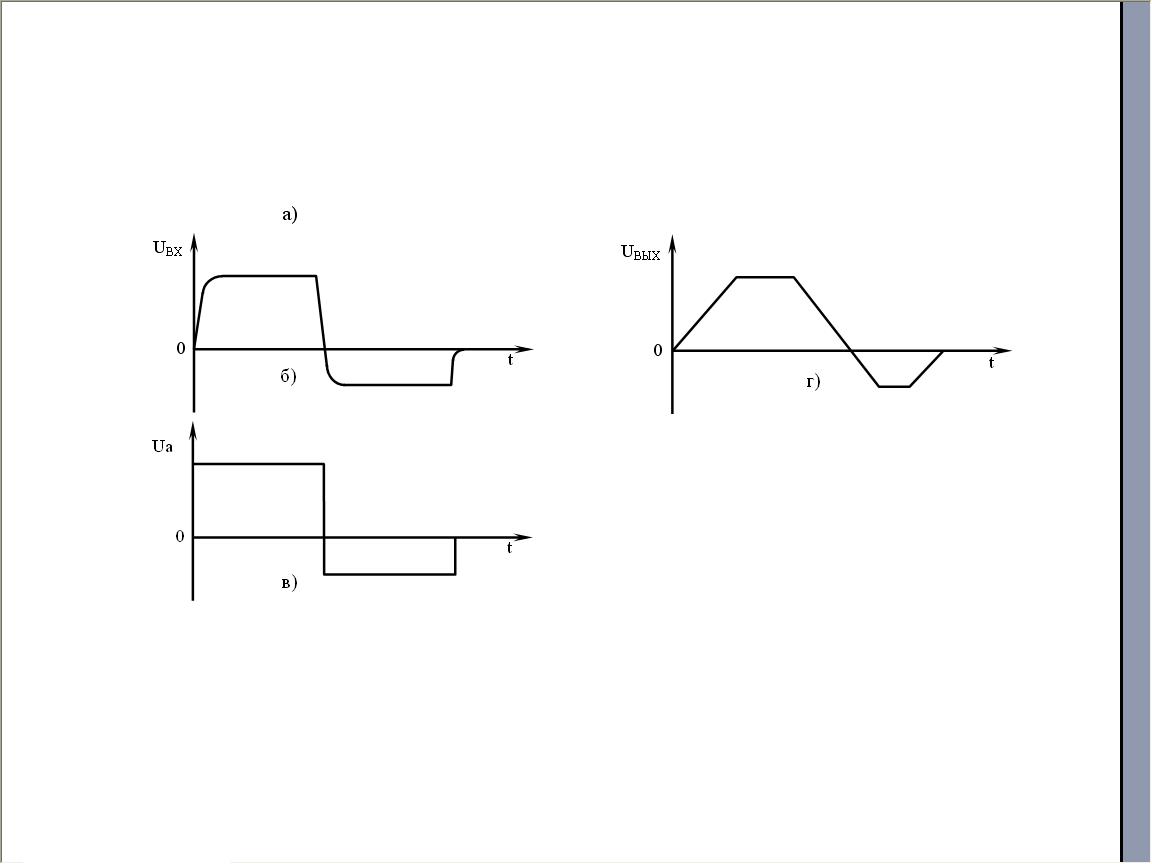

На рис. 15, б приведены временные зависимости входного напряжения, аналогичного показанному на рис. 1,в, и соответствующие ему зависимости uа(t) (рис. 15, в) и uвых(t) (рис. 15, г), принятые при нулевых начальных условиях (Uвых0 = 0). В отличие от рассмотренной выше схемы данный задатчик интенсивности в пределах допустимой мощности нагрузки обеспечивает практически идеальную линейную зависимость выходного напряжения от времени.

Рис. 16 Принципиальная схема задатчика интенсивности АЈ.

В установившихся режимах, когда Uвых

имеет противоположный знак и

практически не отличается от Uвх

по модулю, поддержание Uвых

= = const происходит при

непрерывном с высокой частотой

переключения компаратора из одного

устойчивого состояния в другое. Уровень

отклонения Uвых от

заданного значения Uвх

для применяемых схем не превышает

десятков милливольт, статический

коэффициент передачи по напряжению

схемы задатчика интенсивности равен

![]() .

.

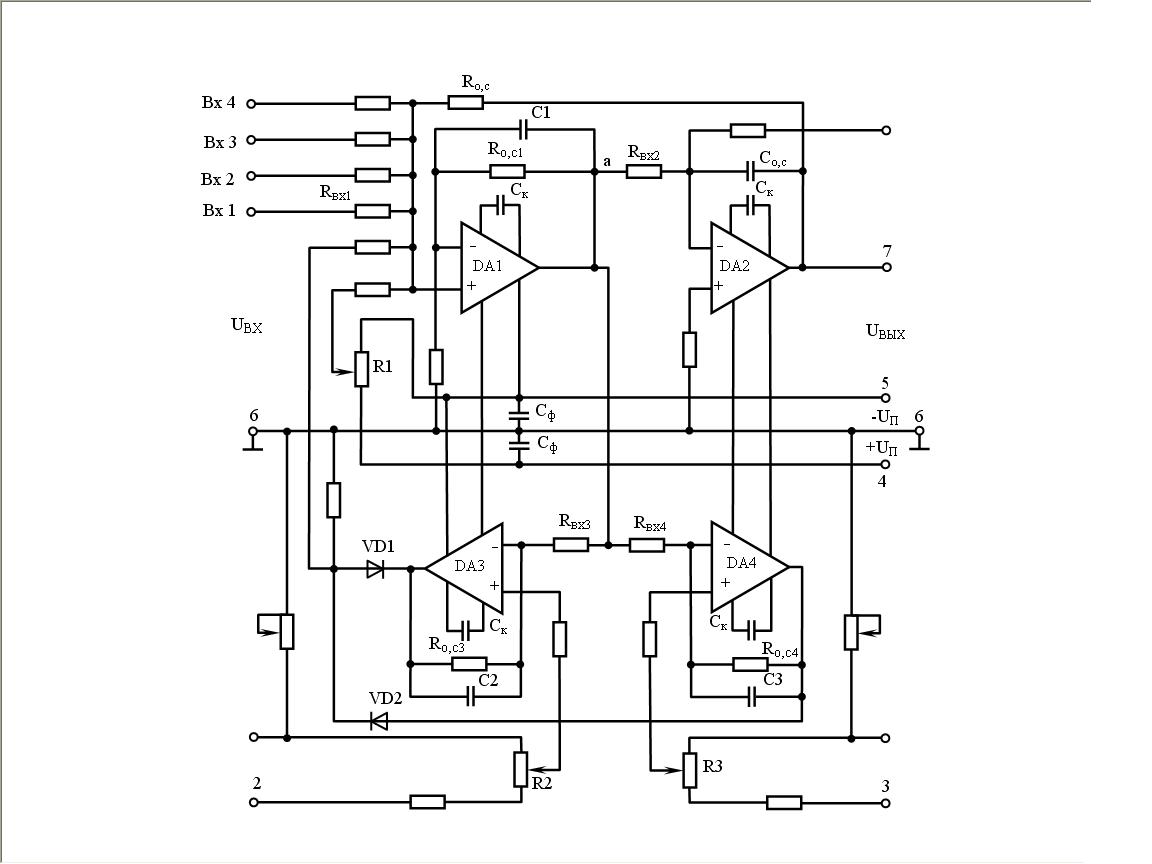

В схеме управления электроприводом роторного колеса экскаватора ЭРШРД-5250, реализованной с применением интегральных ОУ, имеются три задатчика интенсивности с одинаковой принципиальной схемой, которая изображена на рис. 16. Она имеет более широкие функциональные возможности, так как позволяет оперативно внешним электрическим сигналом регулировать темп изменения выходного сигнала задатчика интенсивности.

Схема состоит из усилителя, интегратора и регулируемого двухполярного ограничителя выходного сигнала нуль–органа. Интегратор собран на ОУ DA2 по той же схеме, которая рассмотрена выше, и напряжение на его выходе, являющееся выходом задатчика интенсивности, изменяется по закону. Усилитель выполнен на ОУ DA1, в отличие от предыдущей схемы является не компаратором, а суммирующим усилителем с коэффициентом передачи по первому входу Ro.c1/Rвх1 около 100.

Регулируемый двухполярный ограничитель собран на ОУ DA8, DA4 и обеспечивает усилителю DA1 жесткую отрицательную ОС по напряжению с отсечкой. Выход DA1 (точка а) подключен через резисторы Rвх, Rвх4 на (–) входы усилителей DA3, DA4, которые имеют коэффициенты усиления Rо,с/Rвх3 и Rо,с4/Rвх4 около 100. На (+) входы этих ОУ поступают сигналы опорных напряжений, снимаемых с движков регулируемых резисторов R2, R3, причем с R2 поступает положительное, а с R3 — отрицательное напряжение.

Данные напряжения усиливаются DA3 и DA4, но благодаря наличию диодов VD1, VD2 не проходят на вход DA1. Если напряжение на выходе DA1 uа под действием uвх достигает уровня ограничения, создаваемого опорным напряжением, то в зависимости от полярности uа появляется на выходе DA3 отрицательное напряжение или положительное напряжение на выходе DA4, которое подается на вход DA1 через открывшийся диод VD1 или VD2. Цепь ОС ограничения замыкается и благодаря ее большому коэффициенту uа поддерживается на уровне, примерно равном уставке ограничения, настроенной резистором R2 или R3.

Таким образом, при подаче напряжения uвх под действием нормированного напряжения uа на выходе интегратора напряжение uвых изменяется во времени линейно. По достижении этим напряжением уровня входного сигнала вступает в действие задержанная ОС через резистор Ro.c, выходное напряжение DA1 уменьшается, отключается ОС усилителя DA1 с отсечкой, снижается темп изменения uвых. При uвых/Rо,с= uвх/Rвх1 достигается ua= 0 и процесс интегрирования прекращается.

Если производная duвых/dt устанавливается жестко, то вывод 2 задатчика следует подключить к выводу 4, а вывод 3 — к выводу 5, тогда в цепи ограничения будут поданы соответственно напряжения питания микросхем +Uп и –Uп. Так сделано в блоках AJ2 и AJ3 схемы управления электроприводом. Когда требуется автоматическая корректировка производной duвых/dt, то на выводы 2 и 3 подключают регулируемое напряжение указанной выше полярности. В блоке АЈ1 по команде реле К2 скачком либо обеспечивается установленный настройкой R3 темп изменения uвых (при uвх>0), либо этот темп снижается практически до нуля.

Задатчик интенсивности имеет четыре входа с одинаковыми коэффициентами передачи.

С помощью резистора R, производится установка uвых= 0 при отсутствии входного сигнала. Конденсаторы Ск корректируют частотные характеристики ОУ DA1—DA4, а конденсаторы С1— СЗ при больших коэффициентах усиления DA1, DA3 и DA4 обеспечивают устойчивость работы схемы ограничения. Конденсаторы Сф выполняют роль развязывающих фильтров в цепях питания.