- •По производственно-технологической практике

- •Общие сведения о предприятии

- •Электротехническое:

- •Водородная энергетика:

- •1.Характеристика подразделения

- •1.1.Общие сведения о подразделении

- •1.2. Основные характеристики выпускаемой продукции

- •1.3. Программное, техническое и метрологическое обеспечение подразделения и используемая техническая документация

- •2.Результаты выполнения задания на практику

- •2.1. Методика получения результатов

- •2.2. Построение и отладка системы диагностирования в сапр QuartusIi.

- •2.3. Анализ полученных результатов

- •3.Заключение

- •4. Список литературы

2.2. Построение и отладка системы диагностирования в сапр QuartusIi.

САПР QuartusII предназначен для автоматизации проектирования логических устройств на элементной базе фирмы Altera. В системе предусмотрено составление проекта с использованием библиотеки компонентов, отладку проекта моделированием, программирование выбранной микросхемы. Многие задачи по проектированию логических устройств по оптимизации структуры, минимизации логических функций и т. д. автоматизированы и не требуют участия разработчика.

При создании проекта была выбрана программируемая логическая интегральная микросхема (ПЛИС) семейства Cyclone с именем EP1C12Q240C7. На вход схемы для анализа будут подаваться сигналы с датчиков напряжения, имеющего так называемую «мавзолейную» форму (см. рис 3). Необходимо непрерывно во времени производить анализ и сравнение реального напряжения инвертора с эталонным и с напряжением при всех возможных неисправностях.

Для осуществления этой задачи сперва необходимо составить банк моделей обрывов транзисторов, взятых отдельно или попарно и коротких замыканий. При создании этих моделей были созданы компоненты (модули) с помощью языка высокого уровня VerilogHDL. Каждый компонент имитирует напряжение на выходе инвертора при той или иной неисправности высчитывая значения Х1…Х6. Например, описание модуля, соответствующего обрыву транзистора A выглядит так:

Module A_XX(u1,u2,u3,u4,u5,u6, res1,res2,res3); /*объявление модуля и его портов */

output reg [18:0] res1, res2, res3; //объявление входных и выходных портов//

input u1,u2,u3,u4,u5,u6;

integer m1,m2,m3,m4,m5,m6, n1,n2,n3,n4,n5,n6, k1,k2,k3,k4,k5,k6;

always begin // начало процесса выполняемого модулем

m1=u1*(-3302); // вычисление промежуточных коэффициентов

m2=u2*(-3302); /* все коэффициенты aj умножены на 1000 для того, чтобы не

использовать тип данных real */

m3=u3*3313;

m4=u4*6089;

m5=u5*(-6098);

m6=u6*(-3339);

n1=u1*630;

n2=u2*640;

n3=u3*2770;

n4=u4*(-2780);

n5=u5*(-366);

n6=u6*2418;

k1=u1*630;

k2=u2*640;

k3=u3*2770;

k4=u4*5546;

k5=u5*(-358);

k6=u6*(-5908);

res1=m1+m2+m3+m4+m5+m6; //получение уровней фазных напряжений

res2=n1+n2+n3+n4+n5+n6;

res3=k1+k2+k3+k4+k5+k6;

end // завершение процесса, выполняемого модулем

endmodule // завершение описания модуля

На входе модели – импульсы на включение транзисторов (см. рис. 2). Они обеспечивают одинаковую частоту смены уровней на выходе модели и инвертора.

Следующим шагом является реализация схемы сравнения реального напряжения с напряжением на выходе моделей. Оно осуществляется единовременно для всех моделей и выполняется с заданной точностью (те с учетом возможных погрешностей). Результатом сравнения является флаг, который обращается в единицу при равенстве уровней во все моменты времени.

Далее из всех флагов формируется массив, который дает нам точное представление о том, как работает в данный момент инвертор. Таким образом, при появлении неисправности в работе инвертора на пульт оператора приходит сообщение о ней с информацией о том, что именно отказало.

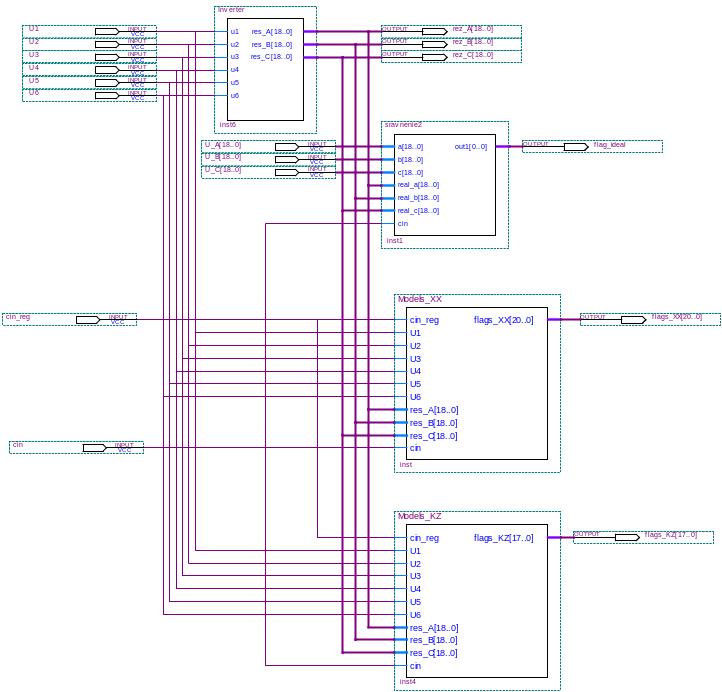

При этом общая структура

проекта имеет следующий вид:

Рис. 5 Общая схема проекта

Как видно, она содержит 6 входов для управляющих импульсов и 2 входа для тактовых генераторов, определяющих моменты времени, в которые будет происходить сравнение. Модуль «Invertor»имитирует работу инвертора, что необходимо для моделирования. Модули «Models_XX» и «Models_KZ» содержат схемы для обрывов и КЗ соответственно.

На рис. 6 (см. приложение) показана структура блока с моделями ХХ и схемами сравнения.