- •Архитектура неймановского компьютера

- •Магистральная архитектура мини- и микро- компьютеров

- •Архитектура универсальных компьютеров – мейнфреймов(селекторные, мультиплексные каналы)

- •Синхронизация пк. Деление и умножение опорной частоты

- •Кэш процессора. Кэш прямого отображения

- •Кэш процессора. Наборно-ассоциативный кэш

- •Кэш процессора. Полностью ассоциативный кэш

- •Политика записи кэШа. Уровни Кэша.

- •Ядро процессора. Понятие конвейера. Нелинейный конвейер.

- •Ядро процессора. Понятие конвейера. Конфликты в конвейере.

- •Ядро процессора. Понятие конвейера. Понятие суперскалярного процессора.

- •Сегментно-страничная организация памяти

- •Подсистема ввода-вывода. Параллельный обмен

- •Подсистема ввода-вывода. Параллельный обмен

- •Прерывания. Виды прерываний. Перехват прерываний

Подсистема ввода-вывода. Параллельный обмен

Подсистема ввода/вывода обеспечивает связь МП с внешними устройствами, к которым будем относить:

устройства ввода/вывода (УВВ): клавиатура, дисплей, принтер, датчики и т. п.;

внешние запоминающие устройства (ВЗУ).

ПВВ в общем случае должна обеспечивать выполнение следующих функций:

согласование форматов данных, поскольку процессор всегда выдает/принимает данные в параллельной форме, а некоторые ВУ — в последовательной. С этой точки зрения различают устройства параллельного и последовательного обмена. В рамках параллельного обмена не производится преобразование форматов передаваемых слов, в то время как при последовательном обмене осуществляется преобразование параллельного кода в последовательный и наоборот;

организация режима обмена — формирование и прием управляющих сигналов, идентифицирующих наличие информации на различных шинах, ее тип, состояние ВУ (Готово, Занято, Авария), регламентирующих временные параметры обмена. По способу связи процессора и ВУ (активного и пассивного) различают синхронный и асинхронный обмены.

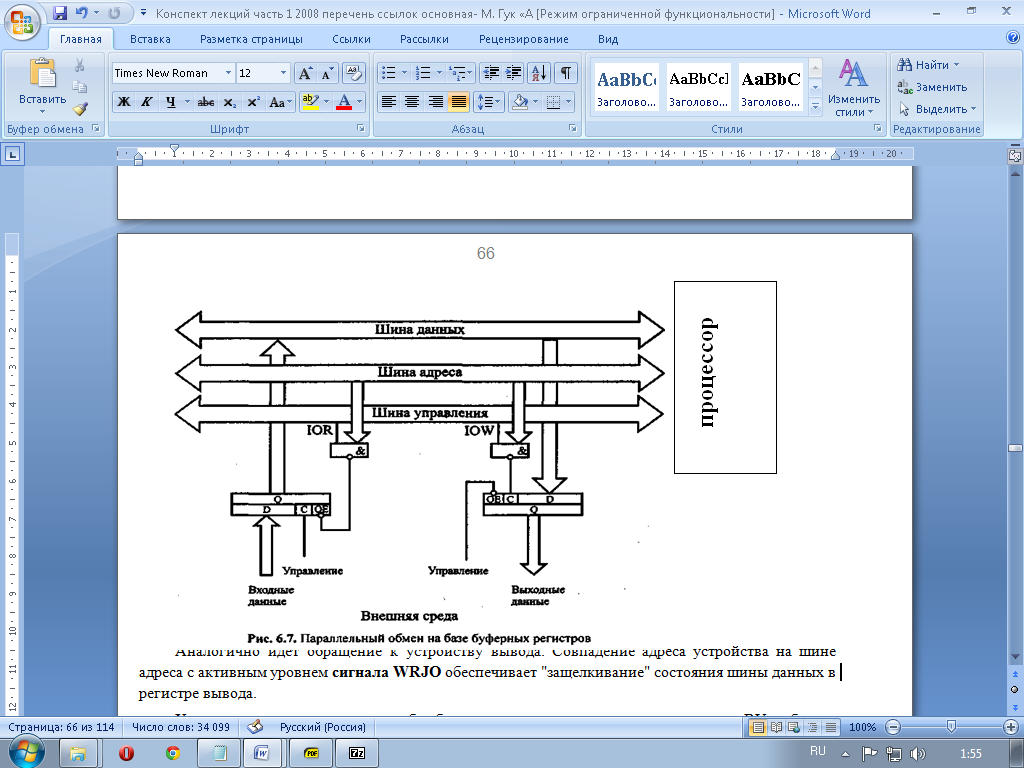

Простейшая подсистема параллельного обмена должна обеспечить лишь дешифрацию адреса ВУ и электрическое подключение данных ВУ к системной шине данных DB по соответствующим управляющим сигналам.

При обращении процессора (он в подобных циклах играет роль активного устройства) к устройству ввода, адрес соответствующего регистра помещается процессором на шину адреса и формируется управляющий сигнал RDIO. Дешифратор адреса, включающий и линию RDIO, при совпадении адреса и управляющего сигнала активизирует выходные линии регистра и его содержимое поступает по шине данных в процессор. Аналогично идет обращение к устройству вывода. Совпадение адреса устройства на шине адреса с активным уровнем сигнала WRJO обеспечивает "защелкивание" состояния шины данных в регистре вывода. При таком способе обмена процессор не анализирует готовность ВУ к обмену, а длительность существования адреса, данных и управляющего сигнала целиком определяется тактовой системой процессора и принятым алгоритмом командного цикла. Напомним, что такой способ обмена называется синхронным. Синхронный обмен реализуется наиболее просто, но он возможен только с устройствами, всегда готовыми к обмену, либо процессор должен перед выполнением команды ввода/вывода программными средствами убедиться в готовности ВУ к обмену (обычно в этом случае предварительно анализируется состояние флага готовности, формируемого ВУ). Кроме того, быстродействие ВУ, взаимодействующее с процессором в синхронном режиме, должно гарантировать прием/выдачу данных за фиксированное время, выделенное процессором на цикл обмена.

Подсистема ввода-вывода. Параллельный обмен

Подсистема ввода/вывода обеспечивает связь МП с внешними устройствами, к которым будем относить:

устройства ввода/вывода (УВВ): клавиатура, дисплей, принтер, датчики и т. п.;

внешние запоминающие устройства (ВЗУ).

ПВВ в общем случае должна обеспечивать выполнение следующих функций:

согласование форматов данных, поскольку процессор всегда выдает/принимает данные в параллельной форме, а некоторые ВУ — в последовательной. С этой точки зрения различают устройства параллельного и последовательного обмена. В рамках параллельного обмена не производится преобразование форматов передаваемых слов, в то время как при последовательном обмене осуществляется преобразование параллельного кода в последовательный и наоборот;

организация режима обмена — формирование и прием управляющих сигналов, идентифицирующих наличие информации на различных шинах, ее тип, состояние ВУ (Готово, Занято, Авария), регламентирующих временные параметры обмена. По способу связи процессора и ВУ (активного и пассивного) различают синхронный и асинхронный обмены.

При организации последовательного обмена ключевыми могут считаться две проблемы:

синхронизация битов передатчика и приемника;

фиксация начала сеанса передачи.

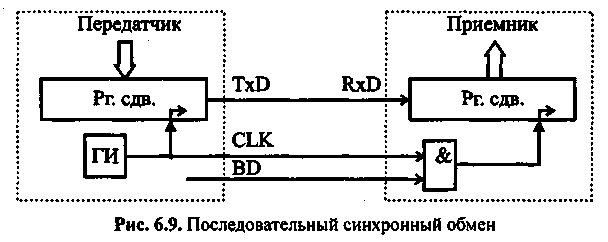

Различают два способа передачи последовательного кода: синхронный и асинхронный.

При синхронном методе передатчик генерирует две последовательности — информационную TxD И синхроимпульсы CLK, которые передаются на приемник по разным линиям. Синхроимпульсы обеспечивают синхронизацию передаваемых битов, а начало передачи отмечается по-разному.

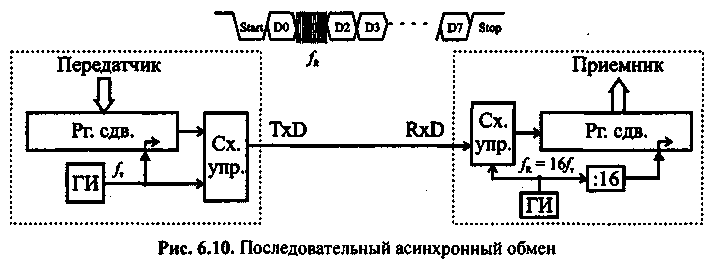

При асинхронном способе обмена можно ограничиться одной линией — данных. Для надежной синхронизации обмена в асинхронном режиме:

передатчик и приемник настраивают на работу с одинаковой частотой;

передатчик формирует стартовый и столовый биты, отмечающие начало и конец посылки;

передача ведется короткими посылками (5—9 битов), а частоты передачи выбираются сравнительно низкими.