- •Архитектура неймановского компьютера

- •Магистральная архитектура мини- и микро- компьютеров

- •Архитектура универсальных компьютеров – мейнфреймов(селекторные, мультиплексные каналы)

- •Синхронизация пк. Деление и умножение опорной частоты

- •Кэш процессора. Кэш прямого отображения

- •Кэш процессора. Наборно-ассоциативный кэш

- •Кэш процессора. Полностью ассоциативный кэш

- •Политика записи кэШа. Уровни Кэша.

- •Ядро процессора. Понятие конвейера. Нелинейный конвейер.

- •Ядро процессора. Понятие конвейера. Конфликты в конвейере.

- •Ядро процессора. Понятие конвейера. Понятие суперскалярного процессора.

- •Сегментно-страничная организация памяти

- •Подсистема ввода-вывода. Параллельный обмен

- •Подсистема ввода-вывода. Параллельный обмен

- •Прерывания. Виды прерываний. Перехват прерываний

Синхронизация пк. Деление и умножение опорной частоты

Системный тактовый генератор генерирует сигналы синхронизации для работы микропроцессора, всех контроллеров и системной шины. Для обеспечения высокой стабильности тактовых частот и их независимости от температуры применяются кварцевые резонаторы, то есть кристаллы кварца, имеющие высокостабильную частоту собственных колебаний. Как правило, в состав системной платы входит несколько кварцевых резонаторов, каждый из которых обеспечивает свой тактовый сигнал. Тактовую частоту процессора можно выбирать путем установки перемычек на системной плате. Поскольку быстродействие различных компонентов (процессора, памяти, адаптеров для шин ISA, EISA, VLB, PCI) существенно различается, в компьютерах на процессорах класса 486 и старше применяется деление опорной частоты для синхронизации шин ввода/вывода и внутреннее умножение частоты в процессорах.

Различают следующие частоты:

HostBusClock- частота системной шины (внешняя частота шины процессора). Эта частота является опорной для всех других.

CPUClock,илиCoreSpeed- внутренняя частота процессора, на которой работает его вычислительное ядро. Современные технологии позволили существенно повысить предельные частоты интегральных компонентов, в связи с чем широко применяется внутреннее умножение частоты на 1,5,2,2,5, 3,3,5, 4 и некоторые другие значения.

PCIBusClock- частота шины PCI, которая должна составлять 25-33,3 МГц (спецификация PCI-2.1 допускает частоту до 66,6 МГц). Она обеспечивается делением Host Bus Clock на 2 (реже на 3).

VLB Bus Clock -частота шины VLB, определяемая аналогично PCIBusClock. Платы с шиной VLBобычно имеют джампер, переключаемый в зависимости от того, превышает ли системная частота значение 33,3 МГц.

ISABusClock, илиATCLK-частота шины ISA, которая должна быть близка к 8 МГц. Она обычно задается в BIOSSetupчерез коэффициент деления системной частоты.

Кроме этих тактовых частот на системной плате присутствуют и другие - для синхронизации СОМ-портов, CMOS-часов, таймера, НГМД и других периферийных адаптеров.

Кэш процессора. Кэш прямого отображения

Кэш микропроцессора — сверхоперативная память, используемый микропроцессором компьютера для уменьшения среднего времени доступа к компьютерной памяти.

Кэш память состоит из 2х блоков:

1. собственно самой памяти в качествеве, которой используют статическую память.

2. кэш контроллера, которая обрабатывает запросы процессора.

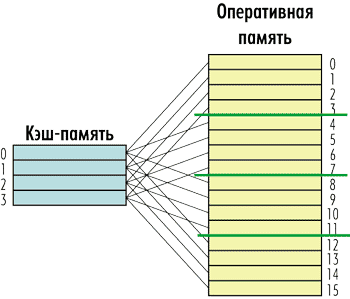

В зависимости от способа определения взаимного соответствия строки кэша и области основной памяти различают три архитектуры кэш-памяти: кэш прямого отображения (direct-mapped cache), полностью ассоциативный кэш (fully associative cache) и их комбинация - частично-ассоциативный или наборно-ассоциативный кэш (set-associative cache).

КЭШ память прямого отображения. Для анализа наличия ячейки в КЭШ памяти, КЭШ контроллер делит адрес запрошенной ячейки на 3 части: Старшая(тег), средняя(номер строки), младшая(смещение). Блок памяти состоит из 2-х массивов: Один маленький одномерный — предназначен для хранения тега, а другой двумерный массив — содержит сами значения ячеек. Тот или иной блок будет всегда помещаться в строго определенную строку кэша, при необходимости заменяя собой хранящийся там другой блок. Когда ЦП обращается к кэшу за необходимым блоком, для определения удачного обращения или кэш-промаха достаточно проверить тег лишь одной строки.

Количество ячеек одномерного массива равно количеству строк в двумерном массиве. Т.е. каждой ячейке соответствует своя строка. Строкой в английской терминологии называется кэш линия, она может быть размером 16, 32, 64,128, 256, байт (размер одной строки). Размер строки задается разрядностью младшей компоненты адреса, т.е. смещением. Кол-во строк задается разрядностью средней компоненты адреса. Размер кэшируемой оперативной памяти обычно меньше всей адресуемой оперативной памяти.

Достоинства заключается в том, что при его реализации требуется относительно небольшие объемы оборудования (транзисторов).

Недостатки: В некоторых случаях возникает неблагоприятная ситуация, когда КЭШ контроллер многократно перезаписывает одни и те же страницы памяти. Что катастрофически сказывается на быстродействии процессора. Этот недостаток устраняется применением оптимизирующих компиляторов, что в большинстве случаев нереально.