- •Архитектура неймановского компьютера

- •Магистральная архитектура мини- и микро- компьютеров

- •Архитектура универсальных компьютеров – мейнфреймов(селекторные, мультиплексные каналы)

- •Синхронизация пк. Деление и умножение опорной частоты

- •Кэш процессора. Кэш прямого отображения

- •Кэш процессора. Наборно-ассоциативный кэш

- •Кэш процессора. Полностью ассоциативный кэш

- •Политика записи кэШа. Уровни Кэша.

- •Ядро процессора. Понятие конвейера. Нелинейный конвейер.

- •Ядро процессора. Понятие конвейера. Конфликты в конвейере.

- •Ядро процессора. Понятие конвейера. Понятие суперскалярного процессора.

- •Сегментно-страничная организация памяти

- •Подсистема ввода-вывода. Параллельный обмен

- •Подсистема ввода-вывода. Параллельный обмен

- •Прерывания. Виды прерываний. Перехват прерываний

Архитектура неймановского компьютера

Исторически неймановская архитектура компьютера является первой классической вычислительной архитектурой. Основные принципы организации неймановських компьютеров:

использования двоичной системы исчисления для представления информации;

программы и данные записываются в двоичном коде с использованием форматов одинаковой длины, которая разрешает сохранять их в общих запоминающих устройствах и над командами программы делать операции как над числами;

управления вычислительным процессом осуществляется централизованно путем последовательного выполнения команд. Каждая команда руководит выполнением одной операции и передает управления следующей команде;

память компьютера имеет линейную организацию, то есть она состоит из последовательно пронумерованных ячеек;

для управления используется язык машинных команд, которым отвечают элементарные операции, которые последовательно выполняются над элементарными операндами.

Перечисленные принципы обеспечивают построение алгоритмически универсальных компьютеров простой архитектуры с минимальными аппаратурными затратами. Такую архитектуру имели компьютеры первых генераций.

Выполнения программы и управления основными узлами компьютера осуществляет процессор. Программы и данные сохраняются в оперативной памяти. Входная информация (программы и данные) вводится через устройство ввода (обычно клавиатура), результаты работы программы выводятся на устройство вывода (устройство печати).

При повышении производительности процессора эта архитектура стала неэффективной, так как электромеханические устройства ввода-вывода остались медленно действующими устройствами. Кроме того, скорость введения определяется скоростью человека-оператора, который принципиально не может быть увеличена выше физиологических границ.

Следующие архитектурные решения в построении компьютеров все большее отходили от традиционных неймановских принципов.

Магистральная архитектура мини- и микро- компьютеров

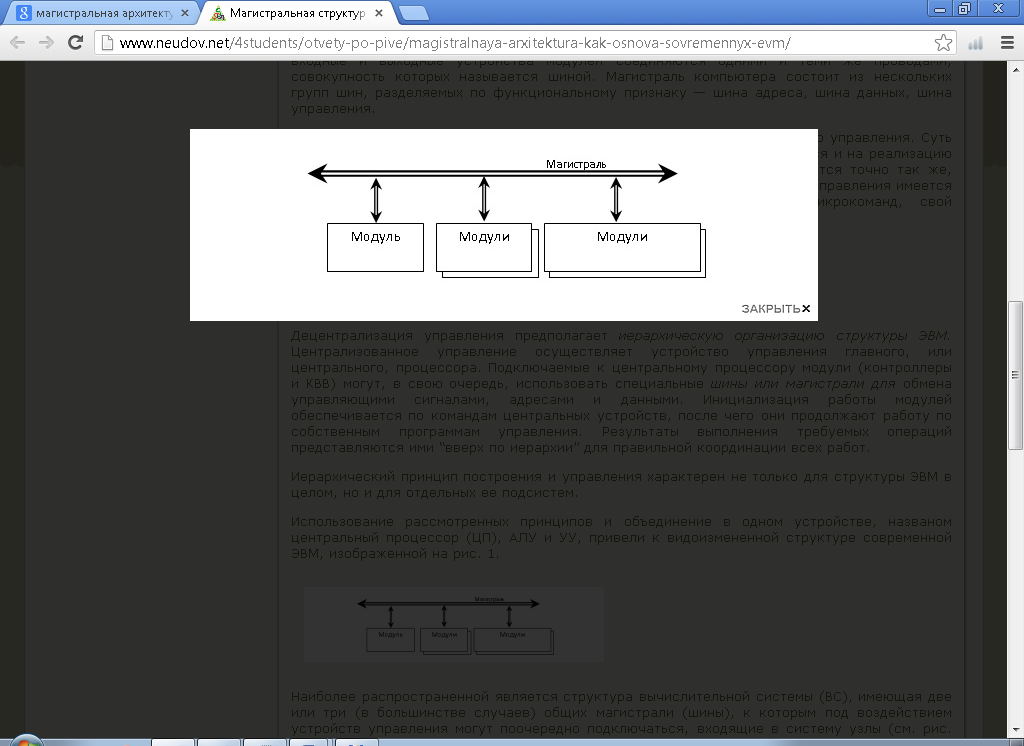

Магистральность – это способ соединения между различными модулями компьютера, когда входные и выходные устройства модулей соединяются одними и теми же проводами, совокупность которых называется шиной. Магистраль компьютера состоит из нескольких групп шин, разделяемых по функциональному признаку — шина адреса, шина данных, шина управления.

Децентрализация управления предполагает иерархическую организацию структуры ЭВМ. Централизованное управление осуществляет устройство управления главного, или центрального, процессора. Подключаемые к центральному процессору модули (контроллеры и КВВ) могут, в свою очередь, использовать специальные шины или магистрали для обмена управляющими сигналами, адресами и данными. Инициализация работы модулей обеспечивается по командам центральных устройств, после чего они продолжают работу по собственным программам управления. Результаты выполнения требуемых операций представляются ими “вверх по иерархии” для правильной координации всех работ.

Использование рассмотренных принципов и объединение в одном устройстве, названом центральный процессор (ЦП), АЛУ и УУ, привели к видоизмененной структуре современной ЭВМ

Наиболее распространенной является структура вычислительной системы (ВС), имеющая две или три (в большинстве случаев) общих магистрали (шины), к которым под воздействием устройств управления могут поочередно подключаться, входящие в систему узлы.

Обработку информации осуществляет ЦП, синхронизируемый тактовыми импульсами устройства синхронизации. Обмен информацией между МП и остальными блоками ВС осуществляется по трем магистралям (шинам): адресной, данных и управляющей. Магистраль адреса (МА, ША) служит для передачи кода адреса, по которому производится обращение к устройствам памяти ввода-вывода и прочим внешним устройствам. Обрабатываемая информация и результаты вычислений передаются по магистрали данных (МД, ШД). Магистраль управления (МУ) передает управляющие сигналы на все блоки ВС, настраивая устройства, участвующие в выполняемой команде, на нужный режим работы.

Использование в ВС трех магистралей обеспечивает высокое быстродействие и упрощает процесс вычисления. Возможно построение ВС с одной или двумя магистралями, по которым последовательно передаются код адреса и обрабатываемая информация, но при этом значительно возрастает время выполнения команды и усложняется организация обмена информацией между узлами.