3.9.3 Режим i2c

USART в режиме I2C обеспечивает интерфейс между микроконтроллером MSP430 и I2C–совместимыми устройствами, подключенными через 2-х проводную последовательную шину. Поддержка режима I2C реализована только в USART0. I2C контроллер обеспечивает следующие характеристики:

поддержка спецификации I2C v2.1 Philips Semiconductor

- Формат передачи байт/слово;

- 7-разрядный и 10-разрядный режимы адресации устройств;

- Общий вызов;

- Старт/рестарт/стоп;

- Режим - ведущий передатчик/ведомый приемник;

- Режим - ведущий приемник/ведомый передатчик;

- Поддержка стандартного режима до 100 кбод и быстрого режима до 400

кбод;

Встроенная память FIFO для буферирования чтения и записи;

Программируемый генератор скорости;

16-разрядный доступ к данным для увеличения пропускной способности шины;

Автоматический подсчет количества байт данных;

Возможность работы в режимах пониженного энергопотребления;

Расширенные возможности прерываний.

3.9.3.1 Общие сведения о шине i2c

Шина I2C (Inter-Integrated Circuit) разработана фирмой Philips в начале 1980-х годов как простая шина внутренней связи для создания управляющей электроники. Используется для соединения низкоскоростных периферийных компонентов с материнской платой, встраиваемыми системами и мобильными телефонами.

Данные по шине I2C передаются с помощью двух проводов – SDA (Serial DAta) и SCL (Serial CLock). По линии SDA передаются собственно данные бит за битом, линия SCL используется для тактирования данных линии SDA. Обе линии являются двунаправленными и должны подключаться к напряжению питания через резисторы номиналом в несколько кило-Ом. Линии SDA и SCL соединяются с одноименными выводами микросхем, подключенных к I2C шине. Эти выводы используют схематехнику открытого стока, поэтому низкий уровень напряжения на шине формируется открытыми ключами микросхем, а высокий – внешними подтягивающими резисторами.

В обмене данными по шине, как правило, принимают участие два устройства – ведущее (master) и ведомое (slave). Различают два типа транзакций по шине – запись и чтение. При записи данные на линии SDA формируются ведущим устройством, при чтения – ведомым. Импульсы тактирования в любом случае передаются ведущим устройством шины. При отсутствии транзакций на шине выходные ключи всех абонентов I2C заперты, и на линиях SDA/SCL поддерживается напряжение высокого уровня.

Каждая транзакция начинается стартовым состоянием (Start condition), за которым следует произвольное количество информационных кадров, передаваемых/принимаемых ведущим устройством, и завершается стоповым состоянием (Stop condition).

Стартовое состояние генерируется мастером шины и представляет собой переключение линии SDA из состояния «1» в состояние «0» при высоком потенциале на линии SCL. Стоповое состояние также формируется мастером, и представляет собой переключение линии SDA из состояния «0» в состояние «1» при высоком потенциале на линии SCL.

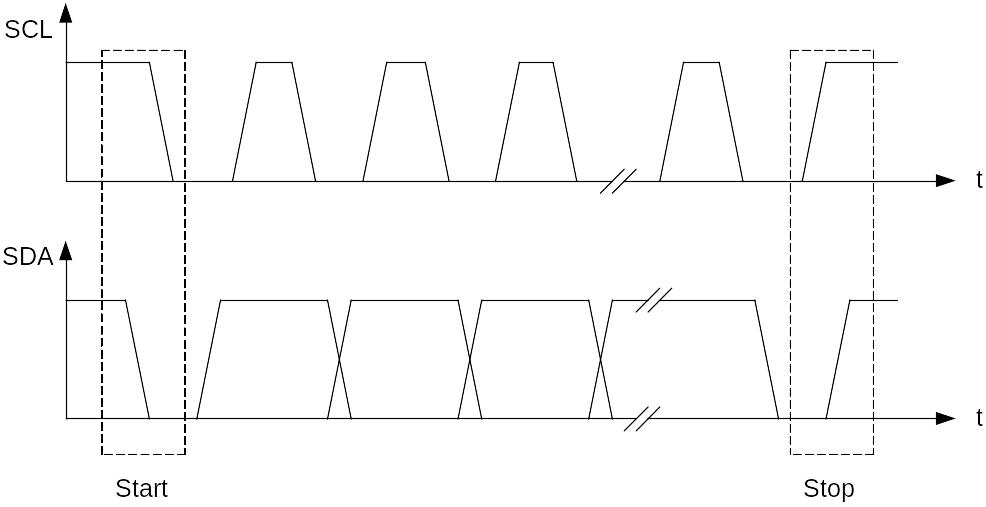

Информационный кадр представляет собой 8 бит данных, передаваемых от передатчика к приемнику, и 9-го бита подтверждения (Acknowledge), передаваемого приемником к передатчику. Байт данных передается последовательно, начиная со старшего бита по линии SDA, и сопровождается импульсами синхронизации по линии SCL. При передаче данных изменение состояние линии SDA разрешено только при низком потенциале на линии SCL. Бит подтверждения формируется приемником, имеет низкий уровень, и также сопровождается импульсом ни линии SCL. Временная диаграмма тактирования шины I2C изображена на рисунке 1.

Рисунок 1. Временная диаграмма тактирования I2C.

Для скорости передачи 100 kHz время удержания сигнала SCL в состоянии низкого уровня, а также время стартового и стопового состояния, не должно быть меньше 4.7 µs, время высокого уровня на лини SCL не должно быть меньше 4 µs. Для скорости 400 kHz эти времена соответственно уменьшаются. В том случае, если ведомое устройство не успевает обрабатывать данные со скоростью, предложенной мастером, оно имеет возможность удерживать линию SCL в низком состоянии до момента готовности приема следующего бита.

Каждое устройство, подключенное к I2C шине, должно иметь свой уникальный адрес, с помощью которого мастер может обратиться к нему. Стандарт I2C определяет два вида адресации устройств – 7-ми битный адрес и 10-ти битный адрес.

7-ми битный режим адресации позволяет объединять на шине I2C до 128 устройств. В этом режиме мастер после генерации стартового состояния всегда передает байт адреса ведомого. В этом случае 7-ми битный адрес передается в битах 7..1 передаваемого байта. Состояние бита 0 (R/W бит) этого байта определяет тип транзакции - значение логического нуля означает, что мастер будет передавать данные ведомому устройству, значении логической единицы означает, что мастер хочет читать данные от ведомого устройства. После передачи адресного байта, мастер генерирует девятый импульс на линии SCL, ожидая бит подтверждения приема от адресуемого устройства. В том случае, если какое-либо устройство на шине распознало свой адрес, оно выставляет на линии SDA низкий уровень на время длительности бита подтверждении. Анализируя состояние бита подтверждения, мастер может определить, присутствует ли на шине устройство с заданным адресом или нет.

В том случае если бит R/W был равен нулю и подтверждение получено, мастер передает данные ведомому устройству байт за байтом, при этом ведомый каждый раз при получении байта подтверждает его прием. Если по каким-либо причинам, ведомый не может принять байт, подтверждение не передается. Для того чтобы завершить сеанс записи данных, мастер генерирует стоповое условие, после чего освобождает шину.

Для чтения данных мастер после стартового условия передает байт адреса с установленным битом R/W. После получения подтверждения мастер переводит свой вывод SDA в высокоимпеданчное состояние и начинает принимать данные от ведомого, подтверждая в 9-м бите прием байта. Цикл чтения завершаться генерацией мастером стопового условия. Однако ведомое устройство, как правило, не имеет информации о том, сколько байт данных потребуется мастеру. Поэтому после приема последнего байта, мастер в качестве подтверждения передает ведомому устройству логическую единицу, уведомляя его, тем самым, об окончании транзакции. В ответ на это, ведомый переводит свой вывод SDA в высокоимпедансное состояние, позволяя мастеру сформировать стоповый переход.

Последовательность записи/чтения данных при 7-ми битном адресе приведена на рис.2.

![]()

Рисунок 2. Формат передачи данных при 7-ми битном адресе.

На ри.2 приняты следующие обозначения:

S – стартовое состояние;

Address – 7 бит адреса;

R/W – бит чтения/записи;

A – бит подтверждения;

DATA – байт данных;

P – стоповое состояние.

10-ти битный режим адресации применяется реже. Он отличается от 7-ми битного тем, что после стартового состояния мастер передает всегда два адресных байта. Первый адресный байт имеет следующую структуру:

Биты 7..3 – содержат фиксированный код 11110;

Биты 2,1 – содержат старшие биты 10-ти битного адреса ведомого устройства;

Бит 0 – бит чтения/записи (R/W бит).

Второй адресный байт содержит восемь младших бит 10-ти битного адреса ведомого устройства.

Как отмечалось выше, при наиболее распространенном 7-ми битном режиме адресации, к I2C шине теоретически можно подключить до 128 устройств. Однако, некоторые значения адресов, согласно спецификации I2C, зарезервированы для специальных целей.

Так, например, адресный байт с кодом 11110ххb, указывает, что далее будет использоваться 10-ти битный режим адресации.

Особые функции имеет значение адреса, равное 0000000b. Этот адрес при сброшенном R/W бите (значение первого байта 00h), используется для общего вызова ведомых устройств (General Call). На этот запрос подтверждением приема адреса могут ответить любые ведомые устройства, способные обрабатывать общий вызов. Обычно после первого нулевого байта мастер посылает второй байт, уточняющий цели общего вызова. Некоторые коды второго байта зарезервированы для сброса, перепрограммирования адреса ведомого и т.д. (см. The I2C-bus Specification version 2.1).

Нулевой адрес при установленном R/W бите (значение первого байта 01h) зарезервирован для посылки так называемого стартового байта (START byte). Посылка этого кода не подразумевает подтверждения приема от какого-либо ведомого устройства. Смысл использования стартового байта заключается в следующем. В том случае, если в качестве ведомого устройства выступает микроконтроллер без аппаратной поддержки I2C шины, его программное обеспечение должно, с одной стороны выполнять задачу, специфическую для данного устройства, а с другой - программно поддерживать протокол I2C. Для этого необходимо, например, чтобы программа микроконтроллера периодически опрашивала вход SDA для регистрации стартового состояния шины. Т.к. тактовая частота шины достаточно велика (100kHz например), частота опроса, также должна быть высокой, что может привести к сокращению временных ресурсов, требуемых для выполнения основной функции микроконтроллера. Для решения этой проблемы, спецификация I2C предлагает следующий алгоритм. Микроконтроллер опрашивает вход SDA с относительно низкой частотой, например - 20kHz. Ведущее устройство, учитывая, что на шине имеются медленные устройства, посылает стартовый байт (код 01h), что по существу является длинной последовательностью нулей, которая может быть обнаружена даже при относительно низкой частоте опроса. Обнаружив стартовый байт, ведомый микроконтроллер должен прервать выполнение своей фоновой задачи и увеличить частоту опроса линии SDA, чтобы надежно зафиксировать следующие стартовое состояние, и работать согласно протоколу шины. Таким образом, стартовый байт может использоваться ведущим устройством для «привлечения внимания» медленных устройств на шине.