- •Восьмеричный код

- •Двоично-десятичный код

- •Шестнадцатеричный код

- •Перевод чисел из разных систем счисления

- •Математические операции над двоичными числами

- •Базисные элементы

- •Базис "и-не"

- •Базис или-не

- •Триггер Шмидта

- •Счетчики с параллельным переносом

- •Реверсивный счетчик

- •Семисегментный дешифратор

- •Регистр хранения

- •Регистр сдвига

- •Регистр последовательных приближений

- •Статическое озу

- •Динамическое озу

- •Масочное пзу

- •Программируемое пзу

- •Программируемая логическая матрица

- •Репрограммируемое пзу

- •Вычитатель

- •Десятичный сумматор

- •Сумматор-накопитель

- •Параллельные ацп

- •Последовательные ацп

- •Последовательно-параллельные ацп

- •Увеличить

- •Simm-модули

Базисные элементы

Очевидно, базис происходит от слова "база". Абсолютно в дырочку. Намек понятен? Базисом называется совокупность элементов, с помощью которых схемотехнически можно реализовать устройство любой сложности. Простым языком, базис - это те элементы, при помощи которых можно сделать любое устройство (речь идет о цифровой технике). Да да, абсолютно любое и самое интересное, что этих базисных элементов всего 2. На их основе можно сделать все вышеперечисленные элементы и еще кучу других, что, собственно, и делается.

Базис "и-не"

И-НЕ - это схема И и схема НЕ, сложенные вместе. Операция, которую производит такой элемент называется инверсией логического умножения или отрицанием логического умножения, ну или инверсией конъюнкции и еще красивым словосочетанием штрих Шеффера. Штрих кого-то там называется потому, что в виде формулы операция И-НЕ записывается так: y = x1 | x2. Вертикальная черта между иксами и есть штрих какого-то Шеффера.

Логический элемент И-НЕ обозначается так:

Таблица истинности для него:

x2 |

x1 |

y |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Суть ясна? Сначала вроде как умножаем (логически), а потом все это отрицаем (тоже логически). Если к элементу И (см. выше) прилепить на выход инвертор, то получим такой вот элемент И-НЕ. Ну и кто уже догадался, если к элементу И-НЕ прилепить на выход инвертор, то получим элемент И. Если у элемента И-НЕ замкнуть входы, то получится тот самый инвертор.

Базис или-не

Здесь все по аналогии с элементом И-НЕ. Операция, выполняемая элементом ИЛИ-НЕ называется инверсией логического сложения или инверсией дизъюнкции и еще красивым словосочетанием стрелка Пирса. Стрелка потому, что в виде формулы функция записывается так: y = x 1↓ x2. Символ между иксами и есть стрелка какого-то Пирса.

Обозначается элемент ИЛИ-НЕ так:

Таблица истинности:

x2 |

x1 |

y |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

Аналогично, если к выходу элемента ИЛИ-НЕ прилепить инвертор, то получится элемент ИЛИ.

Существует помимо перечисленных еще куча других элементов, рассматривать их будем по ходу дела. Эти элементы представляют собой комбинацию вышеперечисленных. Ну а напоследок рассмотрим элемент "ИСКЛЮЧАЮЩЕЕ-ИЛИ".

Операция, выполняемая таким элементом называется сложение по модулю два и обозначается плюсиком в кружочке, т. е. вот таким символом ⊕. В виде уровнения функция записывается так: X1⊕X2. Читается это, как "либо икс один, либо икс два". Обозначение элемента ИСКЛЮЧАЮЩЕЕ-ИЛИ следующее:

Таблица истинности:

x2 |

x1 |

y |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Кстати, этот элемент можно заменить логическими элементами И, ИЛИ, НЕ, поскольку

![]()

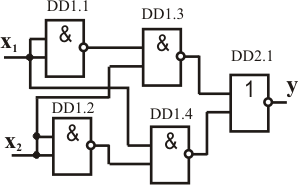

Для пущей наглядности составим схему из базисных элементов (И-НЕ, ИЛИ-НЕ).

Вот вам и применение законов алгебры логики. Где это может пригодиться? Ну допустим, собираете вы какую-то схему с использованием цифровых микросхем, среди которых есть логический элемент ИСКЛЮЧАЮЩЕЕ-ИЛИ (или два), а у вас его нет. Ну в падлу идти в магазин или где-то ковыряться в платах. А тут бах, под рукой завались микросхем с логикой И-НЕ, ИЛИ-НЕ, например 155ЛА3. Таким образом, зная свойства цифровых устройств и основы булевой алгебры, недостающий элемент легко заменяется другими. К тому же, подобный метод имеет и обратное направление, т. е. если в какой-то схеме стоит изображенная на рисунке часть, она легко заменяется на один элемент ИСКЛЮЧАЮЩЕЕ-ИЛИ (а вдруг автор схемы торопился и не догадался сам этого сделать). Причем схемотехническая часть может быть любой, главное, чтобы выполнялось условие сложения по модулю два. Идея ясна? Подобным принципом менять можно почти все, суть в том, чтобы максимально упростить схемотехнику при сохранении ее простоты и легкоповторяемости.

В предыдущих главах рассматривались логические элементы, у которых состояние сигналов на выходе определяется состоянием сигналов на входе. В триггере состояние на выходах определяется не только состоянием на входах, но и от состояния на выходах.

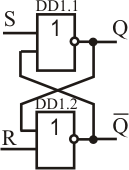

Триггер - это устройство, обладающее двумя состояниями устойчивого равновесия. Триггер еще можно назвать устройством с обратными связями. На рисунке изображена схема триггера на логических элементах ИЛИ-НЕ.

Рис. 1 Схема простейшего RS-триггера

Такая схема называется асинхронным RS-триггером. Первый (сверху) выход называется прямым, второй - инверсным. Если на оба входа (R и S) подать лог. нули, то состояние выходов определить невозможно. Триггер установится как ему заблагорассудится, т. е. в произвольное состояние. Допустим, на выходе Q присутствует лог. 1, тогда на выходе не Q (Q с инверсией) обязательно будет лог. 0. И наоборот. Чтобы установить триггер в нулевое состояние (когда на прямом выходе лог. 0, на инверсном - лог. 1) достаточно на вход R подать напряжение высокого уровня (про уровни напряжений здесь). Если высокий уровень подать на вход S, то это переведет его в состояние 1, или как говорят, в единичное состояние (на прямом выходе лог. 1, на инверсном - лог. 0). И в том, и в другом случаях напряжение соответствующего уровня может быть очень коротким импульсом - на грани физического быстродействия микросхемы. То есть, триггер обладает двумя устоячивыми состояниями, причем эти состояния зависят от ранее воздействующих сигналов, что позволяет сделать следующий вывод - триггер является простейшим элементом памяти. Буквы R и S по-буржуйски set - установка, reset - сброс (предустановка). На рис. 2 RS-триггер показан в "микросхемном исполнении".

Рис. 2 RS-триггер в интегральном исполнении

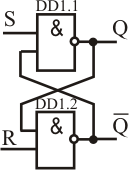

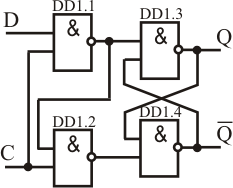

RS-триггер можно соорудить и на элементах И-НЕ, как показано на рисунке 3. Такая конструкция встречается довольно часто.

Рис. 3 RS-триггер на логических элементах И-НЕ

Принцип работы такой же, как у триггера на элементах ИЛИ-НЕ, за исключением инверсии управляющих сигналов, т. е. установка и сброс триггера производится не лог. 1, а лог. 0. Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными.

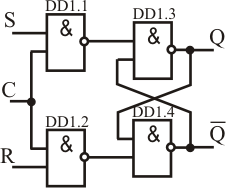

Если схему асинхронного триггера немного дополнить, то получим вот такое:

Рис. 4 Синхронный RS-триггер на логических элементах И-НЕ

В таком триггере вводится дополнительный вход С, называемый тактовым или синхронизирующим. Изменение состояний триггера происходит при подаче сигналов лог. 1 на входы R и S и последующим воздействием на вход С тактового (синхронизирующего) импульса. Если на тактовый вход импульс не воздействует, то состояние триггера не изменится. Другими словами, изменение состояния триггера происходит под действием синхроимпульса, поэтому такие триггеры называются синхронными.

D-триггер

D-триггер отличается от синхронного RS-триггера тем, что у него только один информационный вход D. D-триггер показан на рисунке 5.

Рис. 5 D-триггер на логических элементах И-НЕ

Если на вход D подать логическую единицу, затем на вход С подать импульс, то на выходе Q (прямой выход) установится лог. 1. Если на вход D подать лог. 0, на С импульс, то на Q установится лог. 0. Т. е. D-триггер осуществляет задержку информации, поступающей на вход D. При чем эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульса триггер переключится, т. е. если на выходе был лог. 0, то станет лог. 1. При следующем импульсе триггер снова переключится, т. е. лог. 1 сменится лог. 0. Таким образом, триггер осуществляет деление частоты входных импульсов на 2 (ведь уровень сигнала на выходе меняется в два раза реже). В таком режиме D-триггер называют счетным или Т-триггером. Этот режим (режим деления частоты) используется довольно широко.

Нетрудно заметить, что для RS-триггера (рис. 1) существует запрещенная комбинация, когда на оба входа поданы лог. 1, на его выходах также устанавливаются лог. 1 и триггер перестает выполнять свои функции (зависает). Поэтому придумали так называемый JK-триггер. У него три входа - J, K, C. Вход J вместо R, вход К вместо S, С так и остается - синхронизацией. Если на вход J подана лог. 1, на К - лог. 0 или наоборот, то он работает как синхронный RS-триггер, если на оба входа J и К поданы лог. 1, то он работает как счетный Т-триггер.