- •Восьмеричный код

- •Двоично-десятичный код

- •Шестнадцатеричный код

- •Перевод чисел из разных систем счисления

- •Математические операции над двоичными числами

- •Базисные элементы

- •Базис "и-не"

- •Базис или-не

- •Триггер Шмидта

- •Счетчики с параллельным переносом

- •Реверсивный счетчик

- •Семисегментный дешифратор

- •Регистр хранения

- •Регистр сдвига

- •Регистр последовательных приближений

- •Статическое озу

- •Динамическое озу

- •Масочное пзу

- •Программируемое пзу

- •Программируемая логическая матрица

- •Репрограммируемое пзу

- •Вычитатель

- •Десятичный сумматор

- •Сумматор-накопитель

- •Параллельные ацп

- •Последовательные ацп

- •Последовательно-параллельные ацп

- •Увеличить

- •Simm-модули

Увеличить

Рис. 2 - Схема ДПФ-фильтра

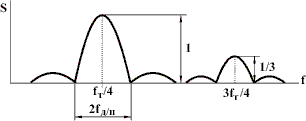

Рис. 3 - Частотная характеристика ДПФ-фильтра

Входной сигнал поступает на аналого-цифровой преобразователь, а с него на два блока схем ИСКЛЮЧАЮЩЕЕ-ИЛИ. На двух триггерах и элементе ИСКЛЮЧАЮЩЕЕ-ИЛИ собран генератор двух опорных сигналов, сдвинутых на 90°. Один из них поступает на первый блок схем ИСКЛЮЧАЮЩЕЕ-ИЛИ, а другой - на второй.

В этих блоках производится умножение на +1 или -1 (т. е. передача с инверсией или без неё). Сумматор и регистр в каждом канале образуют сумматор-накопитель, который накапливает сумму по каждому импульсу частоты дискретизации fд. Через n тактов накопления результаты заносятся в функциональный преобразователь X/Y, который выполняет операцию (X2 + Y2)1/2, где X и Y - результаты суммирования на выходах сумматоров-накопителей. С выхода функционального преобразователя цифровой код поступает на цифро-аналоговый преобразователь, на выходе которого образуется аналоговый сигнал.

Частотная характеристика ДПФ-фильтра показана на рис. 3. Ширина полосы пропускания определяется примерно как fд/n, а резонансная частота fрез = fт/4 (поскольку тактовая частота fт делится триггерами в 4 раза). У такого ЦФ имеются побочные резонансы на частотах 3fрез, 5fрез, 7fрез, ... с относительными уровнями 1/3, 1/5, 1/7, ... Для получения более приемлимой формы частотной характеристики устанавливают несколько ДПФ-фильтров со сдвинутыми друг относительно друга частотами fт и результаты их вычислений объединяют на сумматоре. В этом случае общая частотная характеристика определяется как сумма частотных характеристик (рис. 3).

БПФ-фильтры

Алгоритм БПФ состоит из р этапов, на каждом из которых n входных отсчетов (а затем и их промежуточных результатов) умножаются на комплексные коэффициенты Wk. Эти коэффициенты можно определить так:

Wk = cos(360°k/n) + jsin(360°k/n),

где k = 0, 1, 2, ..., n-1.

Например, при n=8 W0=1; W1=0,7+j0,7; W2=j; W3=-0,7+j0,7; W4=-1; W5=-0,7-j0,7; W6=-j; W7=0,7-j0,7.

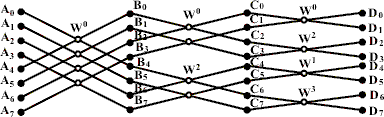

Базовая операция БПФ имеет вид X=A+WkB; Y=A-WkB, где А, В - значения входного сигнала. Операции над значениями входного сигнала проводятся в p=log2n этапов (например, при n=8, р=3). На рис. 4 показана схема выполнения операций при 8-точечном БПФ. На первом этапе из значений входного сигнала А0...А7 образуются комбинации:

B0 = A0 + W0A4; B1 = A1 + W0A5,...

На втором этапе из полученных значений В0...В7 формируются комбинации:

C0 = B0 + W0B2; C1 = B1 + W0B3,...

И, наконец, на третьем этапе формируются комбинации:

D0 = C0 + W0C1; D1 = С0 + W0C1 и т. д.

Рис. 4 - Схема выполнения операций при БПФ

Числа D0...D7 являются выходными числами БПФ-фильтра - отсчетами спектра сигнала.

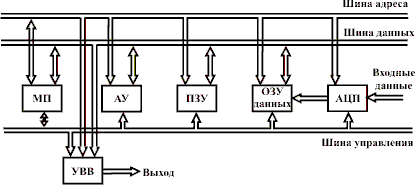

В данном случае БПФ-фильтр является блоком из 8 фильтров. Аппаратурная реализация БПФ-фильтров довольно сложна. Чаще всего их реализуют в микропроцессорном исполнении. Общая структура вычислителя БПФ на микропроцессоре показана на рис. 5.

Рис. 5 - Структура вычислителя БПФ

Аналоговый сигнал, который необходимо анализировать, поступает на аналого-цифровой преобразователь (АЦП), с которого записывается в ОЗУ данных. Микропроцессор (МП) производит операции вычисления по программе, записанной в ПЗУ. Для ускорения вычисления можно использовать специализированное арифметическое устройство (АУ). Выдача результатов вычислений потребителю (ЭВМ, устройство отображения) производится через устройство ввода-вывода (УВВ). При обработке сигналов работа вычислителя состоит из трех этапов: прием входной информации, выполнение БПФ, выдача обработанной информации.

DRAM (Dynamic Random Access Memory) - динамическое запоминающее устройство с произвольным порядком выборки.

В этих устройствах для хранения одного бита используется один транзистор и пара конденсаторов. Так что в линейке 256 Mb применяется более 256 000 000 транзисторов. В этом разделе есть статья о динамических ОЗУ, поэтому особо на структуре останавливаться не будем.

Транзистор каждого регистра используется для чтения состояния смежного конденсатора. Конденсатор заряжен - значит в ячейке записана 1, нет - значит 0. Все просто. Но есть неприятная тема: заряды постепенно с конденсаторов стекают и память должна постоянно регенерироваться. Если хотя бы на долю секунды питание прекратиться или заглючит система регенерации - все, данных нет!

Динамическое ОЗУ со времени своего появления прошло несколько стадий роста, и процесс ее совершенствования не останавливается. За свою десятилетнюю историю DRAM меняла свой вид несколько раз. Вначале микросхемы динамического ОЗУ производились в DIP-корпусах. Затем их сменили модули, состоящие из нескольких микросхем: SIPP, SIMM и, наконец, DIMM и RIMM.

DIP- корпус —это исторически самая древняя реализация DRAM. DIP-корпус соответствует стандарту IC. Обычно это маленький черный корпус из пластмассы, по обеим сторонам которого располагаются металлические контакты

Микросхемы (по-другому, чипы) динамического ОЗУ устанавливаются так называемыми банками. Банки бывают на 64, 256 Кбайт, 1 и 4 Мбайт. Каждый банк состоит из девяти отдельных одинаковых чипов. Из них восемь чипов предназначены для хранения информации, а девятый чип служит для проверки четности остальных восьми микросхем этого банка.

Чипы памяти бывают одно и четырехразрядными, и иметь емкость 64 Кбит, 256 Кбит, 1 и 4 Мбит.

Следует отметить, что памятью с DIP-корпусами комплектовались персональные компьютеры с микропроцессорами i8086/88, i80286 и, частично, i80386SX/DX. Установка и замена этого вида памяти была нетривиальной задачей. Мало того, что приходилось подбирать чипы для банков памяти одинаковой разрядности и емкости. Приходилось прилагать усилия и смекалку, чтобы чипы правильно устанавливались в разъемы. К тому же необходимо было не разрушить контакты механически, не повредить их инструментом, статическим электричеством, грязью и т.п. Поэтому уже в компьютерах с процессором i80386DX эти микросхемы стали заменять памяти SIPP и SIMM.

Одной из незаслуженно забытых конструкций модулей памяти являются SIPP-модули. Эти модули представляют собой маленькие платы с несколькими напаянными микросхемами DRAM.

SIPP происходит от буржуйских слов Single Inline Package. SIPP-модули соединяются с системной платой с помощью контактных штырьков. Под контактной колодкой находятся 30 маленьких штырьков (рис. 1), которые вставляются в соответствующую панель системной платы.

Модули SIPP имели определенные вырезы, которые не позволяли вставить их в разъемы неправильным образом. По некоторым мнениям, этот вид модулей лидировал по простоте их установки на системную плату

Рис. 1 - Модуль SIPP