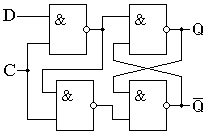

3. Синхронний d-тригер

D-тригер (D від англ. Delay - затримка або від data - дані) - запам'ятовує стан входу і видає його на вихід. D-тригери мають, як мінімум, два входи: інформаційний D і синхронізації С. Після приходу активного фронту імпульсу синхронізації на вхід С D-тригер відкривається. Збереження інформації в D-тригерах відбувається після спаду імпульсу синхронізації С. Так що інформація на виході залишається незмінною до приходу чергового імпульсу синхронізації, D-тригер називають також тригером із запам'ятовуванням інформації або тригером-засувкою.

D-тригер в основному використовується для реалізації засувки. Так, наприклад, для зняття 32 біт інформації з паралельної шини, беруть 32 D-тригера і об'єднують їх входи синхронізації для управління записом інформації в засувку, а 32 D входи під'єднують до шини.

Схема та таблиця станів зображена на рис. 3.

|

|

||||||||||||||||||

а) |

б) |

Рис. 3 Схема (а) та таблиця істинності (б) синхронного D-тригера

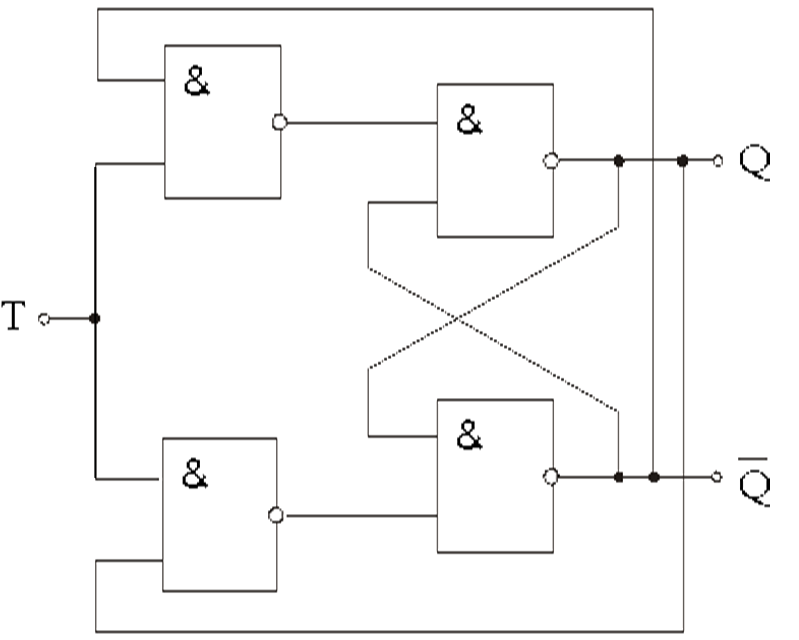

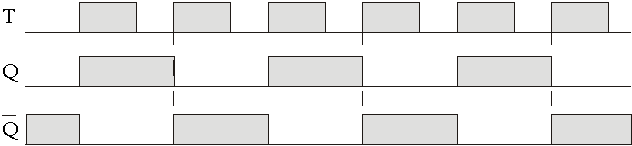

4. Т-тригер

Т-тригер - це лічильний тригер. У Т-тригера є тільки один вхід. Після поступання на цей вхід імпульсу, стан Т-тригера змінюється на прямо протилежний. Лічильним він називається тому, що він ніби підраховує кількість імпульсів, що надійшли на його вхід. Лічити цей тригер вміє тільки до одного. При отриманні другого імпульсу T-тригер знову скидається в початковий стан.

Т-тригери бажано будувати тільки на базі двоступеневих тригерів. Використання двох тригерів дозволяє уникнути самозбудження схеми, оскільки лічильні тригери будуються за допомогою схем зі зворотним зв'язком.

На рис. 4 зображено схему (а) та часові діаграми (б) Т-тригера, що побудований на основі RS-тригера.

|

|

а) |

б) |

Рис. 4 Схема (а) та часові діаграми (б) Т-тригера

Також Т-тригер можна синтезувати з будь-якого двоступінчастого тригера. Т-тригер часто застосовують для зниження частоти в 2 рази, при цьому на Т вхід подають одиницю, а на С - сигнал з частотою, яка буде поділена на 2.

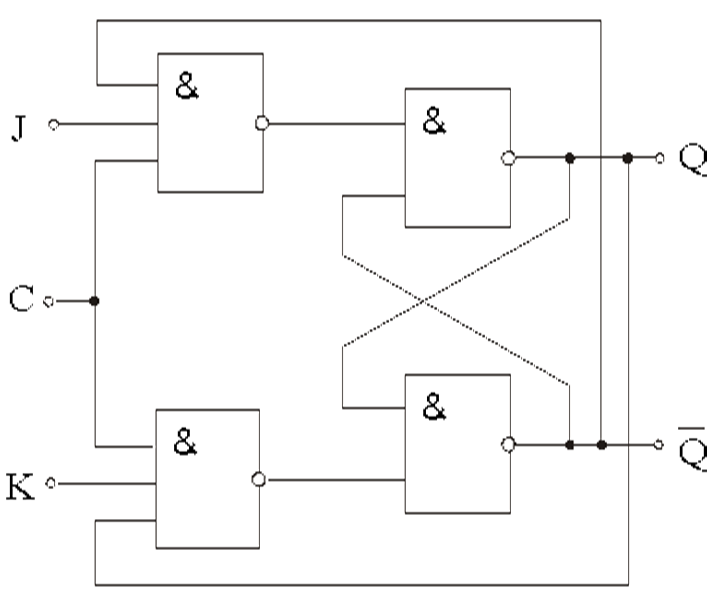

4. Синхронний jk-тригер

JK-тригер працює так само як RS-тригер, з одним лише винятком: при подачі логічної одиниці на обидва входи J і K стан виходу тригера змінюється на протилежний. Вхід J (від англ. Jump - стрибок) аналогічний входу S у RS-тригера. Вхід K (від англ. Kill - вбити) аналогічний входу R у RS-тригера. При подачі одиниці на вхід J і нуля на вхід K вихідний стан тригера стає рівним логічній одиниці. А при подачі одиниці на вхід K і нуля на вхід J вихідний стан тригера стає рівним логічному нулю. JK-тригер на відміну від RS-тригера не має заборонених станів на основних входах, проте це ніяк не допомагає при порушенні правил розробки логічних схем. На практиці застосовуються тільки синхронні JK-тригери, тобто стани основних входів J і K враховуються тільки в момент тактування, наприклад по позитивному фронту імпульсу на вході синхронізації.

|

|

||||||||||||||||||||||||||||||

а) |

б) |

Рис. 5 Схема (а) та таблиця станів (б) JK-тригера

5. УГО (умовні графічні позначення) тригерів

1 |

|

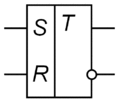

асинхронний RS-тригер |

2 |

|

синхронний RS-тригер |

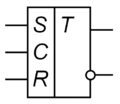

3 |

|

синхронний D-тригер |

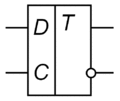

4 |

|

лічильний T-тригер |

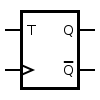

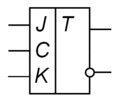

5 |

|

синхронний JK-тригер |