- •Результаты выполнения работ

- •Лабораторная работа № 1 Исследование интегральных микросхем логических элементов

- •Лабораторная работа №2. «Исследование работы дешифратора»

- •Лабораторная работа n 3. «Исследование работы мультиплексора»

- •Лабораторная работа № 4 «Исследование работы сумматора»

- •Лабораторная работа №5 "Исследование работы триггеров"

- •Лабараторная работа №6. "Исследование работы регистра"

- •« Исследование работы счетчика »

Лабораторная работа n 3. «Исследование работы мультиплексора»

Цель работы:

_________________________________________________________________________

Задание 1. Синтезировать схему мультиплексора 4*1 (четыре в один) на логических элементах И, ИЛИ, НЕ.

Разработать таблицу функционирования мультиплексора (табл. 1), записать логическое выражение выхода Q.

Таблица 1.

Номер входа |

Адресные входы |

Выход |

|

А1 |

А0 |

Q |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

2 |

1 |

0 |

|

3 |

1 |

1 |

|

Q =

1.2. По логическому выражению построить схему мультиплексора на логических элементах И, ИЛИ, НЕ (рис 1) и его условное графическое обозначение (рис 2.)

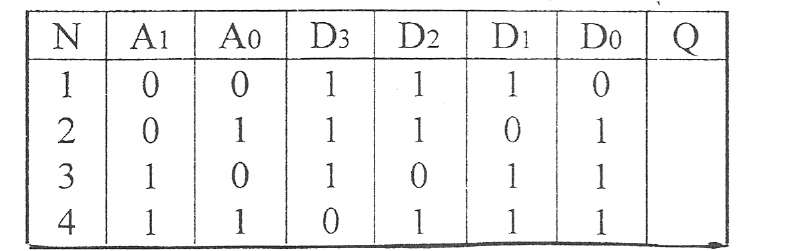

Задание 2. Исследование работы ИМС мультиплексора.

2.1 Собрать схему исследования (рис. 2)

Таблица

2.

2.4.Выводы

________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

2.5. Собрать схему исследования подключения ко входам D0 - D3 мультиплексора выходы счетчика (рис 3.).

2.6 – 2.8. Подать на адресные входы (А1А0) различные комбинации, зарисовать форму напряжения на выходе Q в таблицу 3.

Таблица 3.

A1 |

А0 |

Форма напряжения на выходе Q |

f |

0 |

0 |

|

f0 |

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

|

2.9. Выводы.

__________________________________________________________________________________________________________________________________________________________________________

Задание 3. Ответить на контрольные вопросы

1. Синтезировать схему мультиплексора 8* 1 на ИМС мультиплексора 4* 1. Указать:

- какой из входных сигналов будет на выходе, если подана адресная комбинация 110;

- какую адресную комбинацию надо подать на входы полученного мультиплексора,

чтобы на выходе появился сигнал с первого входа.

2. Синтезировать схему демультиплексора 1*4.

Лабораторная работа № 4 «Исследование работы сумматора»

Цель работы: ___________________________________________________________________________________________________________________________________________________________________________________________________________________________________

Задание 1. Синтезировать схему одноразрядного полусумматора на логических элементах.

1.1.Составить таблицу функционирования полусумматора (таблица 1).

Таблица

1

№

Ai

Bi

Si

Pi+1

0

1

2

3

1.2. Записать логические выражения выходов полусумматора

1.3. Нарисовать схему полусумматора. Привести условное графическое обозначение .

Задание 2. Исследование работы схемы одноразрядного полусумматора.

2.1. Собрать схему исследования полусумматора (рис. 3).

2.2. Подать на входы требуемые уровни, записать состояния выходов в таблицу 2.

Таблица

2

.

____________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

Задание 3. Исследование ИМС одноразрядного полного сумматора К155ИМ1.

3.1. Собрать схему исследования (рис. 4).

3.2. Подать на входы различные комбинации входных сигналов. Записать состояния выходов в таблицу 3.

Таблица 3

№ |

Аi |

Вi |

Pi |

Si |

Si |

Рi+1 |

0 |

0 |

0 |

0 |

|

|

|

1 |

0 |

0 |

1 |

|

|

|

2 |

0 |

1 |

0 |

|

|

|

3 |

0 |

1 |

1 |

|

|

|

4 |

1 |

0 |

0 |

|

|

|

5 |

1 |

0 |

1 |

|

|

|

6 |

1 |

1 |

0 |

|

|

|

7 |

1 |

1 |

1 |

|

|

|

3.3. Выводы.

_______________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

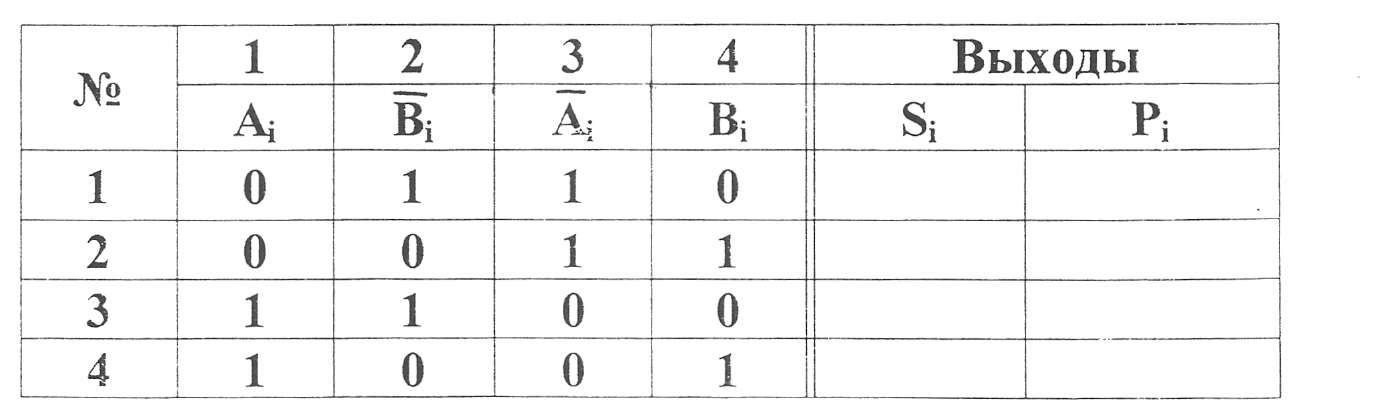

Задание 4. Исследование двухразрядного сумматора.

4.1. Собрать схему двухразрядного сумматора, используя две ИМС одноразрядных сумматоров и двух логических элементов И-НЕ (рис.53)

4.2. Подать на входы 1, 2, 3, 4 различные двухразрядные двоичные числа, записать состояния выходов в таблицу 4.

Таблица 4

№№ |

1 |

2 |

3 |

4 |

Выходы |

||

А1 |

В1 |

А2 |

В2 |

S1 |

S2 |

P3 |

|

1 |

1 |

1 |

0 |

1 |

|

|

|

2 |

0 |

1 |

0 |

1 |

|

|

|

3 |

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

4.4. Выводы.

_______________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

Задание 5. Ответить на контрольные вопросы.

Назначение одноразрядного сумматора.

Нарисовать схему трехразрядного двоичного сумматора.

Записать логические сигналы на входах и выходах схемы трехразрядного

сумматора при сложении двух двоичных чисел: 111 + 101